- 您现在的位置:买卖IC网 > PDF目录61074 > ICSSSTV16857CGLF-T SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 PDF资料下载

参数资料

| 型号: | ICSSSTV16857CGLF-T |

| 元件分类: | 锁存器 |

| 英文描述: | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 |

| 封装: | 0.240 INCH, TSSOP-48 |

| 文件页数: | 5/7页 |

| 文件大小: | 72K |

| 代理商: | ICSSSTV16857CGLF-T |

5

ICSSSTV16857C

0002F—10/25/02

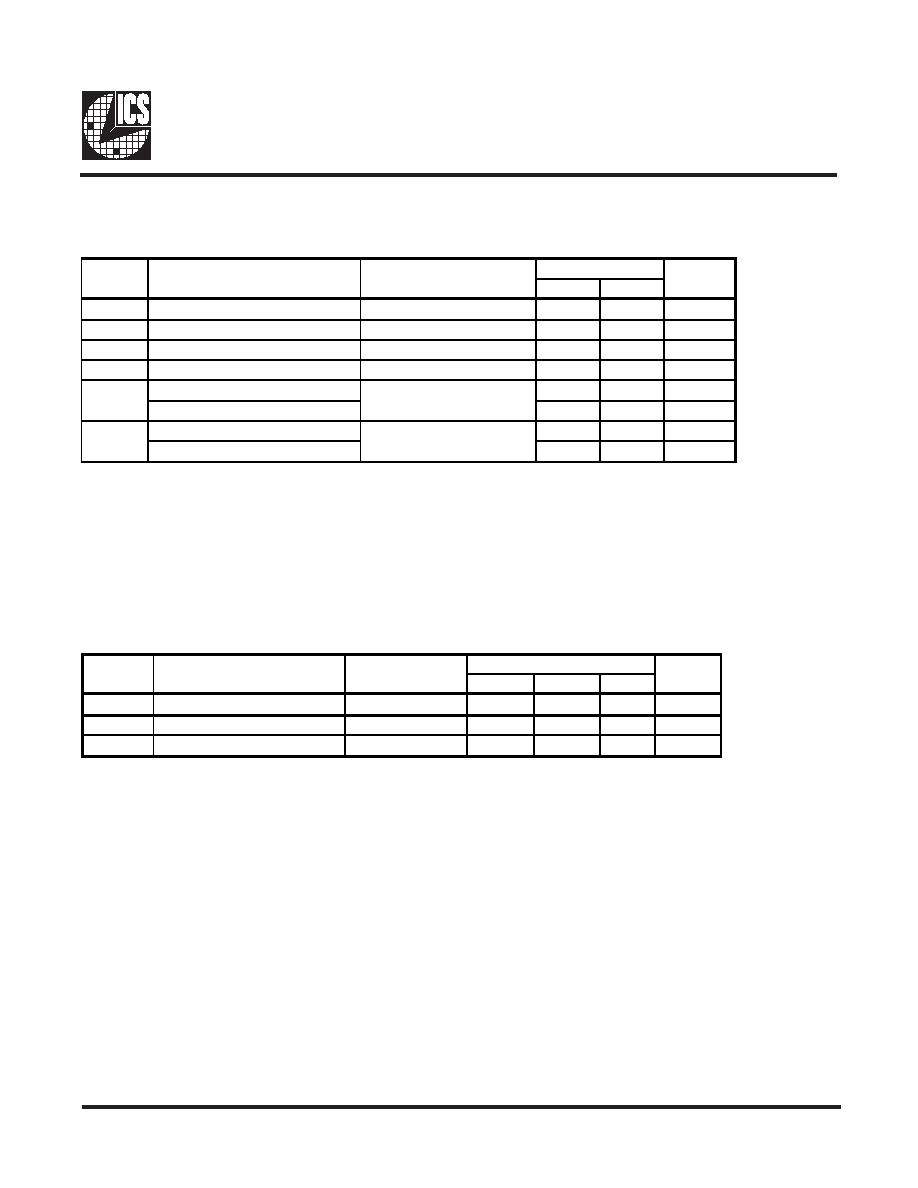

Switching Characteristics

(over recommended operating free-air temperature range, unless otherwise noted) (see Figure 1)

MIN

TYP

MAX

fmax

200

MHz

tPD

CLK, CLK#

Q

1.7

2.1

2.5

ns

tphl

RESET#

Q

3.5

ns

SYMBOL

VDD = 2.5V ±0.2V

UNITS

From

(Input)

To

(Output)

Timing Requirements

1

(over recommended operating free-air temperature range, unless otherwise noted)

MIN

MAX

fclock

Clock frequency

200

MHz

tPD

Clock to output time

1.7

2.5

ns

tRST

Reset to output time

3.5

ns

tSL

Output slew rate

1

4

V/ns

Setup time, fast slew rate

2 & 4

0.4

ns

Setup time, slow slew rate

3 & 4

0.5

ns

Hold time, fast slew rate

2 & 4

0.4

ns

Hold time, slow slew rate

3 & 4

0.5

ns

Notes:

1 - Guaranteed by design, not 100% tested in production.

2 - For data signal input slew rate

≥ 1V/ns.

3 - For data signal input slew rate

≥ 0.5V/ns and < 1V/ns.

4 - CLK, CLK# signals input slew rates are

≥ 1V/ns.

UNITS

Th

VDDQ = 2.5±0.2V

tS

Data before CLK

↑ , CLK#↓

Data after CLK

↑ , CLK#↓

SYMBOL

PARAMETERS

相关PDF资料 |

PDF描述 |

|---|---|

| ICSSSTV16857CYLLF-T | LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICSSSTV16857CYL-T | LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICSSSTV16857CYLLF-T | LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICSSSTV16857CYL-T | LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICSSSTVF16859BYGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICSSSTV16857CG-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YG-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YL-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16859 | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

| ICSSSTV16859CG-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

发布紧急采购,3分钟左右您将得到回复。