- 您现在的位置:买卖IC网 > PDF目录61074 > ICSSSTV16857CYLLF-T (INTEGRATED DEVICE TECHNOLOGY INC) LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | ICSSSTV16857CYLLF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | 4.40 MM, 0.40 MM PITCH, MO-153, TVSOP-48 |

| 文件页数: | 1/8页 |

| 文件大小: | 81K |

| 代理商: | ICSSSTV16857CYLLF-T |

Integrated

Circuit

Systems, Inc.

ICSSSTV16857C

Third party brands and names are the property of their respective owners.

16857C

Rev C

11/21/01

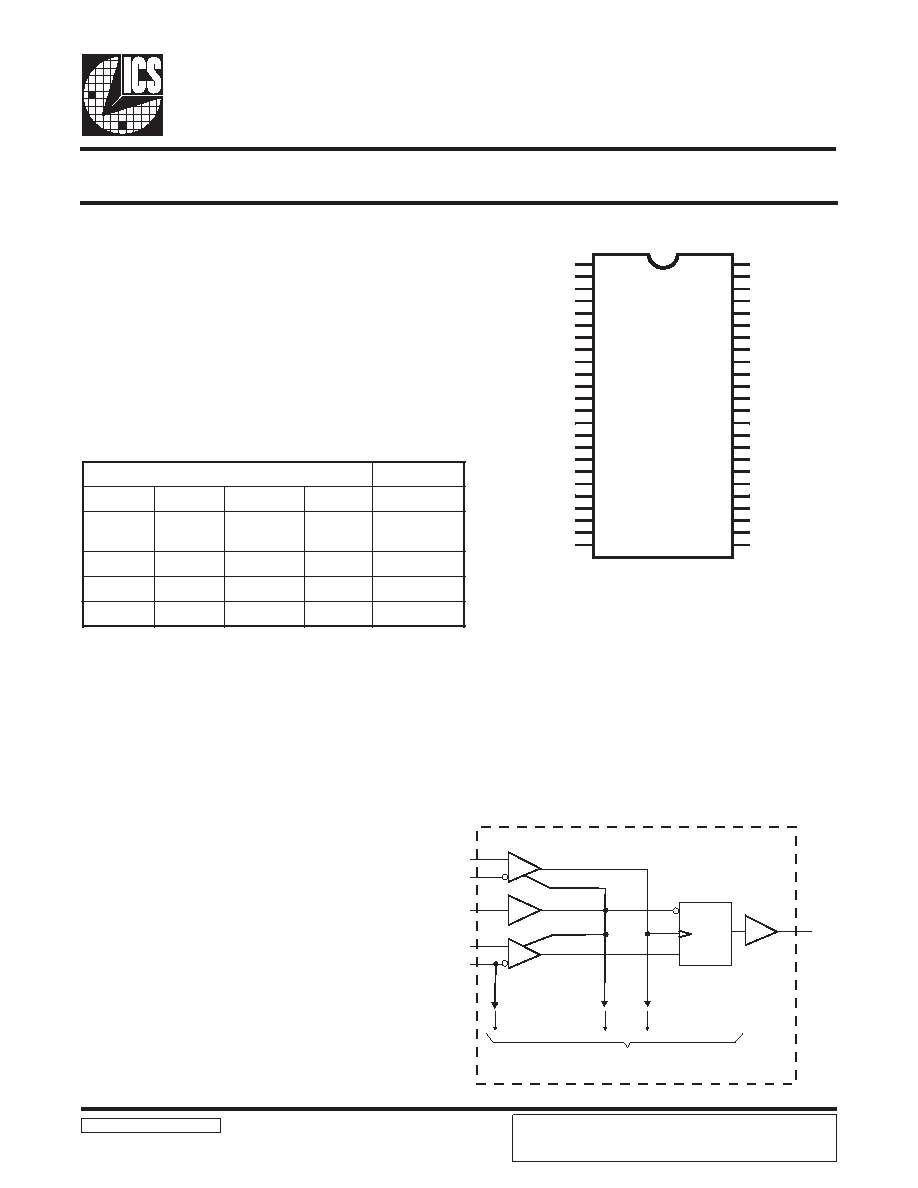

Pin Configuration

Recommended Application:

DDR Memory Modules

Product Features:

Differential clock signal

Meets SSTL_2 signal data

Supports SSTL_2 class I & II specifications

Low-voltage operation

VDD = 2.3V to 2.7V

48 pin TSSOP package

DDR 14-Bit Registered Buffer

Truth Table

1

Block Diagram

Q1

Q2

GND

VDDQ

Q3

Q4

Q5

GND

VDDQ

Q6

Q7

VDDQ

GND

Q8

Q9

VDDQ

GND

Q10

Q11

Q12

VDDQ

GND

Q13

Q14

D1

D2

GND

VDD

D3

D4

D5

D6

D7

CLK#

CLK

VDD

GND

VREF

RESET#

D8

D9

D10

D11

D12

VDD

GND

D13

D14

ICSSSTV16857C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

CLK

CLK#

38

39

48

35

34

D1

VREF

RESET#

To 13 Other Channels

Q1

1

CLK

R

D1

Notes:

1.

H = High Signal Level

L = Low Signal Level

↑ = Transition LOW-to-HIGH

↓ = Transition HIGH -to LOW

X = Irrelevant

2.

Output level before the indicated

steady state input conditions were

established.

s

t

u

p

n

Is

t

u

p

t

u

O

Q

#

T

E

S

E

RK

L

C#

K

L

CD

Q

L

r

o

X

g

n

i

t

a

o

l

F

r

o

X

g

n

i

t

a

o

l

F

r

o

X

g

n

i

t

a

o

l

F

L

H

↑↓

HH

H

↑↓

LL

HH

r

o

LH

r

o

LX

Q

0

)

2

(

48-Pin TSSOP & TVSOP

6.10 mm. Body, 0.50 mm. pitch = TSSOP

4.40 mm. Body, 0.40 mm. pitch = TSSOP (TVSOP)

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

相关PDF资料 |

PDF描述 |

|---|---|

| ICSSSTV16857CYL-T | LOW SKEW CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICSSSTVF16859BYGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

| ICSSSTVF16859BYGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

| ID8080A-1 | 8-BIT, 3.12 MHz, MICROPROCESSOR, CDIP40 |

| IDA3416-20 | SPECIALTY OPTOELECTRONIC DEVICE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICSSSTV16857YG-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YL-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16859 | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

| ICSSSTV16859CG-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

| ICSSSTV16859YG-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

发布紧急采购,3分钟左右您将得到回复。