参数资料

| 型号: | ID82C54 |

| 厂商: | Intersil |

| 文件页数: | 3/22页 |

| 文件大小: | 0K |

| 描述: | IC OSC PROG TIMER 8MHZ 24DIP |

| 标准包装: | 165 |

| 类型: | 可编程计时器 |

| 频率: | 8MHz |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 10mA |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 24-CDIP(0.600",15.24mm) |

| 包装: | 管件 |

| 供应商设备封装: | 24-CDIP |

| 安装类型: | 通孔 |

11

82C54

MODE DEFINITIONS

The following are defined for use in describing the operation

of the 82C54.

CLK PULSE -

A rising edge, then a falling edge, in that

order, of a Counter’s CLK input.

TRIGGER -

A rising edge of a Counter’s Gate input.

COUNTER LOADING -

The transfer of a count from the CR

to the CE (See “Functional Description”)

MODE 0: INTERRUPT ON TERMINAL COUNT

Mode 0 is typically used for event counting. After the Control

Word is written, OUT is initially low, and will remain low until

the Counter reaches zero. OUT then goes high and remains

high until a new count or a new Mode 0 Control Word is

written to the Counter.

GATE = 1 enables counting; GATE = 0 disables counting.

GATE has no effect on OUT.

After the Control Word and initial count are written to a

Counter, the initial count will be loaded on the next CLK

pulse. This CLK pulse does not decrement the count, so for

an initial count of N, OUT does not go high until N + 1 CLK

pulses after the initial count is written.

If a new count is written to the Counter it will be loaded on

the next CLK pulse and counting will continue from the new

count. If a two-byte count is written, the following happens:

1. Writing the first byte disables counting. Out is set low

immediately (no clock pulse required).

2. Writing the second byte allows the new count to be

loaded on the next CLK pulse.

This allows the counting sequence to be synchronized by

software. Again OUT does not go high until N + 1 CLK

pulses after the new count of N is written.

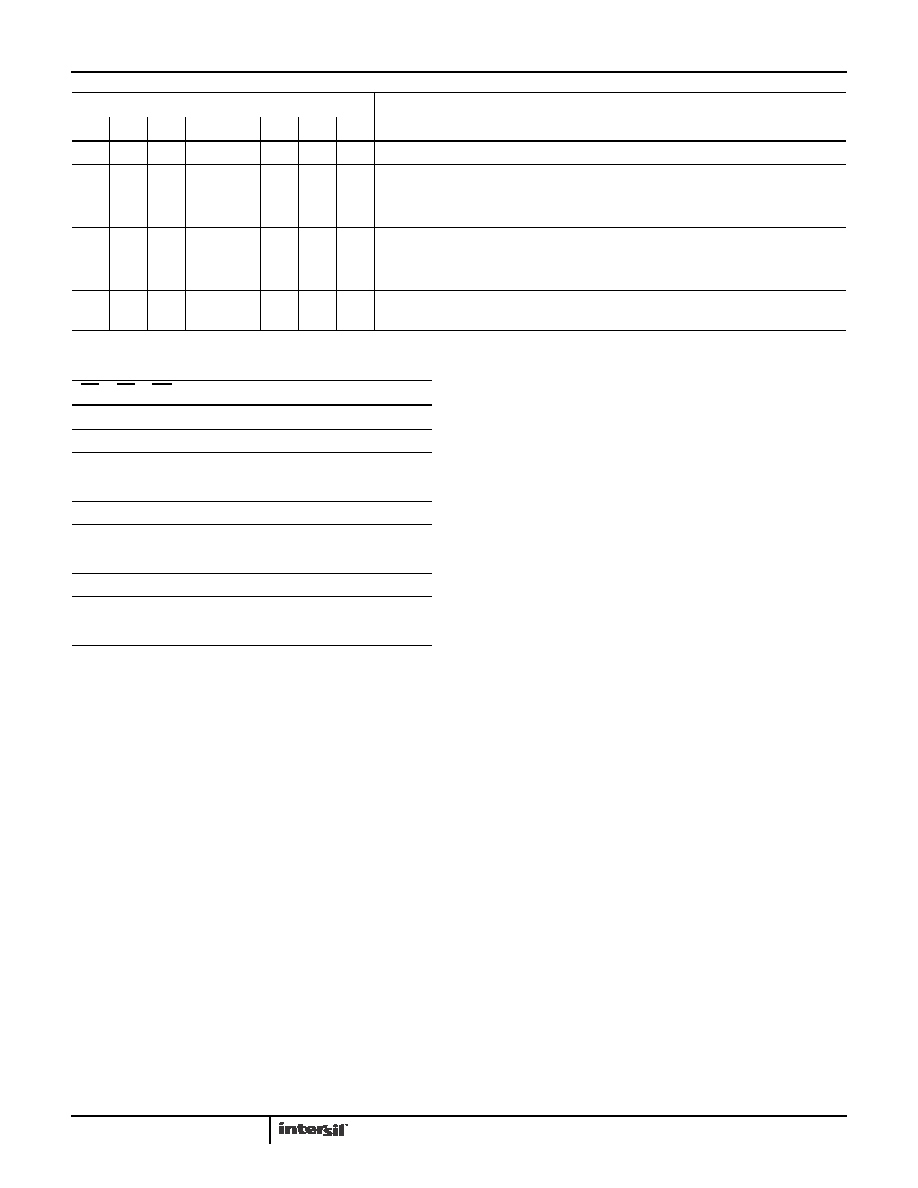

COMMANDS

DESCRIPTION

RESULT

D7

D6

D5

D4

D3

D2

D1

D0

1

0

1

0

Read-Back Count and Status of Counter 0

Count and Status Latched for Counter 0

1

0

1

0

Read-Back Status of Counter 1

Status Latched for Counter 1

1

0

1

0

Read-Back Status of Counters 2, 1

Status Latched for Counter 2,

But Not Counter 1

1

0

1

0

Read-Back Count of Counter 2

Count Latched for Counter 2

1

0

1

0

Read-Back Count and Status of Counter 1

Count Latched for Counter 1,

But Not Status

1

0

1

0

Read-Back Status of Counter 1

Command Ignored, Status Already

Latched for Counter 1

FIGURE 7. READ-BACK COMMAND EXAMPLE

CS

RD

WR

A1

A0

01000

Write into Counter 0

01001

Write into Counter 1

01010

Write into Counter 2

01011

Write Control Word

00100

Read from Counter 0

00101

Read from Counter 1

00110

Read from Counter 2

00111

No-Operation (Three-State)

1

XXXX

No-Operation (Three-State)

0

1

X

No-Operation (Three-State)

FIGURE 8. READ/WRITE OPERATIONS SUMMARY

相关PDF资料 |

PDF描述 |

|---|---|

| IDT2308A-4DCI8 | IC CLOCK MULT ZD HI DRV 16-SOIC |

| IDT2309-1HPGGI | IC CLK BUFFER ZD HI DRV 16-TSSOP |

| IDT2309A-1HPGG | IC CLK BUFFER ZD HI DRV 16-TSSOP |

| IDT2309B-1HPGGI | IC CLK BUFFER HIGH DRIVE 16TSSOP |

| IDT23S05-1HDCGI | IC CLK BUFFER PLL HI DRV 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ID82C54/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog Timer Circuit |

| ID82C54-10 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Programmable Interval Timer |

| ID82C54-12 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Programmable Interval Timer |

| ID82C55A | 功能描述:外围驱动器与原件 - PCI PERIPH PRG-I/O 5V 8MHZ 40CDIP IND RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| ID82C55A/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral Interface |

发布紧急采购,3分钟左右您将得到回复。