- 您现在的位置:买卖IC网 > PDF目录65576 > IDT5T9950APFGI8 (INTEGRATED DEVICE TECHNOLOGY INC) 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 PDF资料下载

参数资料

| 型号: | IDT5T9950APFGI8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| 封装: | LEAD FREE, TQFP-32 |

| 文件页数: | 2/9页 |

| 文件大小: | 81K |

| 代理商: | IDT5T9950APFGI8 |

2

INDUSTRIALTEMPERATURERANGE

IDT5T9950/A

2.5V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK II JR.

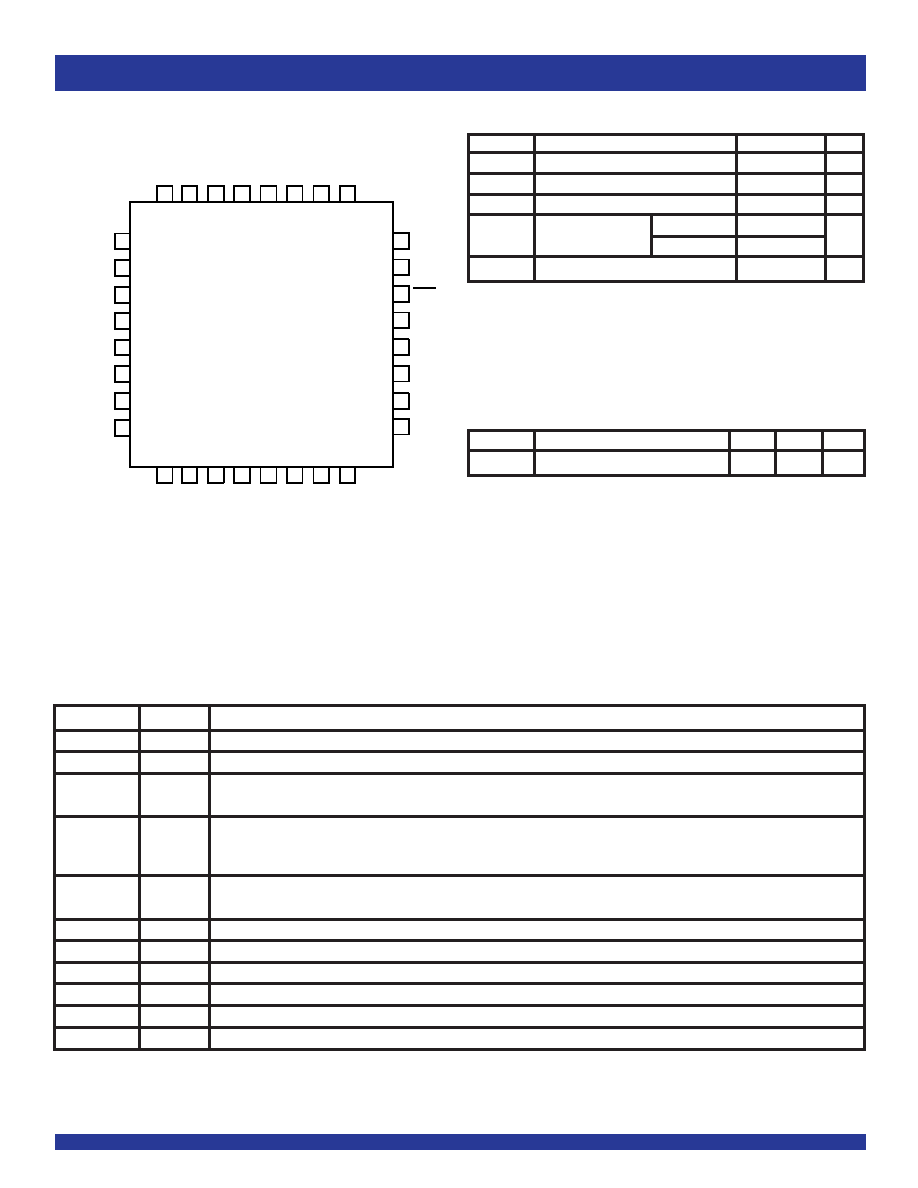

PIN CONFIGURATION

NOTE:

1. Stresses beyond those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute-

maximum-rated conditions for extended periods may affect device reliability.

ABSOLUTE MAXIMUM RATINGS(1)

Symbol

Description

Max

Unit

VDDQ, VDD

Supply Voltage to Ground

–0.5 to +4.6

V

VI

DC Input Voltage

–0.5 to VDD+0.5

V

REF Input Voltage

–0.5 to +4.6

V

Maximum Power

TA = 85°C

0.7

W

Dissipation

TA = 55°C

1.1

TSTG

Storage Temperature Range

–65 to +150

° C

NOTE:

1. Capacitance applies to all inputs except TEST, FS, nF[1:0], and DS[1:0].

CAPACITANCE(TA=+25°C,f=1MHz,V

IN

= 0V)

Parameter

Description

Typ.

Max.

Unit

CIN

InputCapacitance

5

7

pF

31

10

3

Q

1

30

29

28

27

26

25

11

12

13

14

15

16

F

S

R

E

F

G

N

D

T

E

S

T

2

F

1

3

Q

0

F

B

2

Q

1

2

Q

0

V

D

Q

V

D

Q

V

D

32

9

3

F

0

G

N

D

2

F

0

1

2

3

4

5

6

7

8

3F1

4F0

4F1

PE

4Q1

4Q0

GND

VDDQ

18

G ND

24

23

22

21

20

19

sO E

1F1

1F0

1Q0

1Q1

VDDQ

17

G ND

TQFP

TOP VIEW

NOTE:

1. When TEST = MID and

sOE = HIGH, PLL remains active with nF[1:0] = LL functioning as an output disable control for individual output banks. Skew selections remain in

effect unless nF[1:0] = LL.

PIN DESCRIPTION

Pin Name

Type

Description

REF

I N

Reference Clock Input

FB

I N

FeedbackInput

TEST(1)

I N

When MID or HIGH, disables PLL (except for conditions of Note 1). REF goes to all outputs. Skew Selections (See Control Summary

Table) remain in effect. Set LOW for normal operation.

sOE(1)

I N

Synchronous Output Enable. When HIGH, it stops clock outputs (except 2Q0 and 2Q1) in a LOW state (for PE = H) - 2Q0 and 2Q1may

be used as the feedback signal to maintain phase lock. When TEST is held at MID level and

sOEis HIGH, the nF[1:0] pins act as output

disable controls for individual banks when nF[1:0] = LL. Set

sOE LOW for normal operation (has internal pull-down).

PE

I N

Selectablepositiveornegativeedgecontrol. WhenLOW/HIGHtheoutputsaresynchronizedwiththenegative/positiveedgeofthereference

clock (has internal pull-up).

nF[1:0]

I N

3-level inputs for selecting 1 of 9 skew taps or frequency functions

FS

I N

Selects appropriate oscillator circuit based on anticipated frequency range. (See Programmable Skew Range.)

nQ[1:0]

OUT

Four banks of two outputs with programmable skew

VDDQ

PWR

Power supply for output buffers

VDD

PWR

Power supply for phase locked loop, lock output, and other internal circuitry

GND

PWR

Ground

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5T9950PFI | 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| IDT5T9950PFI8 | 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| IDT5T995PFGI | 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP44 |

| IDT5T995APFI | 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP44 |

| IDT5V2305NRGI8 | 5V SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5T9950PFGI | 功能描述:IC CLK BUFFER/DVR 1:10 32TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ II JR 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| IDT5T9950PFGI8 | 功能描述:IC CLK BUFFER/DVR 1:10 32TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ II JR 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T9955BFGI | 功能描述:IC CLK DRIVER DUAL PLL 96-FBGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ W 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| IDT5T9955BFGI8 | 功能描述:IC CLK DRIVER DUAL PLL 96-FBGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ W 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| IDT5T995APPGI | 功能描述:IC CLK DRIVER 2.5V PLL 44-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ II 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。