- 您现在的位置:买卖IC网 > PDF目录22177 > IDT70T3399S166DD (IDT, Integrated Device Technology Inc)IC SRAM 2MBIT 166MHZ 144TQFP PDF资料下载

参数资料

| 型号: | IDT70T3399S166DD |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 11/27页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 2MBIT 166MHZ 144TQFP |

| 产品变化通告: | Product Discontinuation 20/Aug/2008 |

| 标准包装: | 6 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,同步 |

| 存储容量: | 2M(128K x 18) |

| 速度: | 166MHz |

| 接口: | 并联 |

| 电源电压: | 2.4 V ~ 2.6 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 144-LQFP 裸露焊盘 |

| 供应商设备封装: | 144-TQFP(20x20) |

| 包装: | 托盘 |

| 其它名称: | 70T3399S166DD |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

�� �

�

�

�IDT70T3339/19/99S�

�High-Speed� 2.5V� 512/256/128K� x� 18� Dual-Port� Static� RAM�

�Industrial� and� Commercial� Temperature� Ranges�

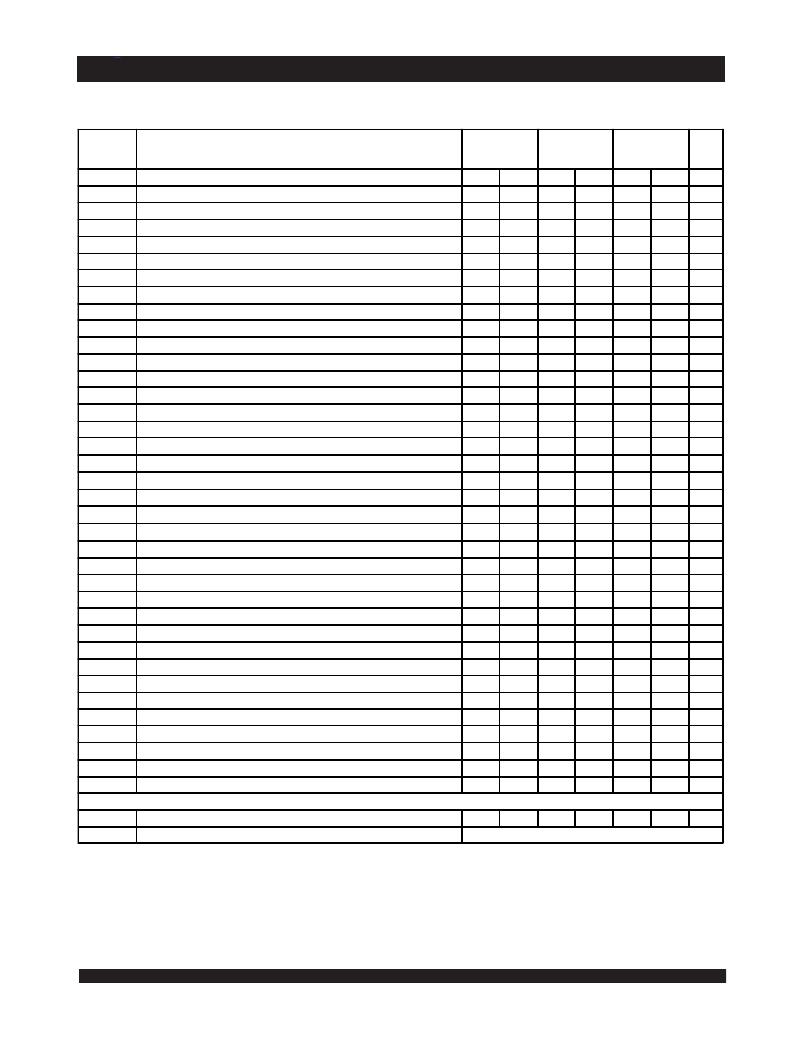

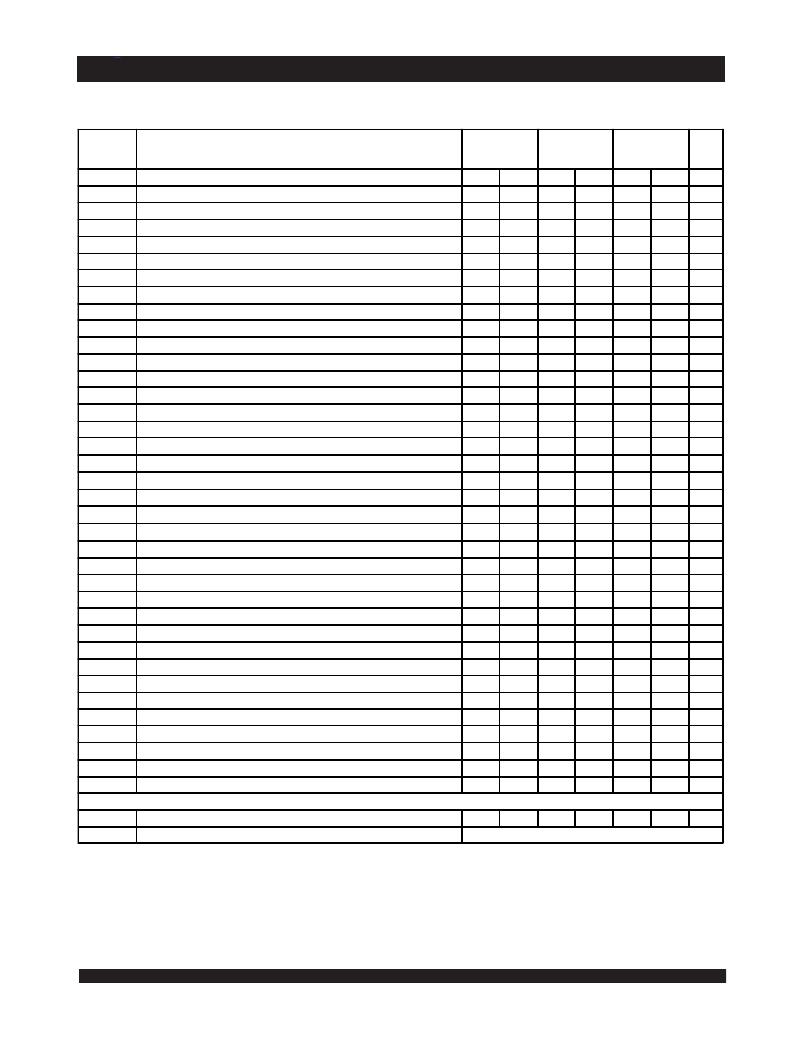

�AC� Electrical� Characteristics� Over� the� Operating� Temperature� Range�

�(Read� and� Write� Cycle� Timing)� (2,3)� (V� DD� =� 2.5V� ±� 100mV,� T� A� =� 0°C� to� +70°C)�

�70T3339/19/99�

�S200�

�Com'l� Only� (5)�

�70T3339/19/99�

�S166�

�Com'l�

�&� Ind� (4)�

�70T3339/19/99�

�S133�

�Com'l�

�&� Ind�

�Symbol�

�t� CYC1�

�t� CYC2�

�Clock� Cycle� Time� (Flow-Through)� (1)�

�Clock� Cycle� Time� (Pipelined)� (1)�

�Parameter�

�Min.�

�15�

�5�

�Max.�

�____�

�____�

�Min.�

�20�

�6�

�Max.�

�____�

�____�

�Min.�

�25�

�7.5�

�Max.�

�____�

�____�

�Unit�

�ns�

�ns�

�t� CH1�

�Clock� High� Time� (Flow-Through)�

�(1)�

�6�

�____�

�8�

�____�

�10�

�____�

�ns�

�t� OHZ�

�t� CL1�

�t� CH2�

�t� CL2�

�t� SA�

�t� HA�

�t� SC�

�t� HC�

�t� SB�

�t� HB�

�t� SW�

�t� HW�

�t� SD�

�t� HD�

�t� SAD�

�t� HAD�

�t� SCN�

�t� HCN�

�t� SRPT�

�t� HRPT�

�t� OE�

�t� OLZ� (6)�

�(6)�

�t� CD1�

�t� CD2�

�t� DC�

�t� CKHZ� (6)�

�t� CKLZ� (6)�

�t� INS�

�t� INR�

�t� COLS�

�t� COLR�

�t� ZZSC�

�t� ZZRC�

�Clock� Low� Time� (Flow-Through)� (1)�

�Clock� High� Time� (Pipelined)� (2)�

�Clock� Low� Time� (Pipelined)� (1)�

�Address� Setup� Time�

�Address� Hold� Time�

�Chip� Enable� Setup� Time�

�Chip� Enable� Hold� Time�

�Byte� Enable� Setup� Time�

�Byte� Enable� Hold� Time�

�R/W� Setup� Time�

�R/W� Hold� Time�

�Input� Data� Setup� Time�

�Input� Data� Hold� Time�

�ADS� Setup� Time�

�ADS� Hold� Time�

�CNTEN� Setup� Time�

�CNTEN� Hold� Time�

�REPEAT� Setup� Time�

�REPEAT� Hold� Time�

�Output� Enable� to� Data� Valid�

�Output� Enable� to� Output� Low-Z�

�Output� Enable� to� Output� High-Z�

�Clock� to� Data� Valid� (Flow-Through)� (1)�

�Clock� to� Data� Valid� (Pipelined)� (1)�

�Data� Output� Hold� After� Clock� High�

�Clock� High� to� Output� High-Z�

�Clock� High� to� Output� Low-Z�

�Interrupt� Flag� Set� Time�

�Interrupt� Flag� Reset� Time�

�Collision� Flag� Set� Time�

�Collision� Flag� Reset� Time�

�Sleep� Mode� Set� Cycles�

�Sleep� Mode� Recovery� Cycles�

�6�

�2�

�2�

�1.5�

�0.5�

�1.5�

�0.5�

�1.5�

�0.5�

�1.5�

�0.5�

�1.5�

�0.5�

�1.5�

�0.5�

�1.5�

�0.5�

�1.5�

�0.5�

�____�

�1�

�1�

�____�

�____�

�1�

�1�

�1�

�____�

�____�

�____�

�____�

�2�

�3�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�4.4�

�____�

�3.4�

�10�

�3.4�

�____�

�3.4�

�____�

�7�

�7�

�3.4�

�3.4�

�____�

�____�

�8�

�2.4�

�2.4�

�1.7�

�0.5�

�1.7�

�0.5�

�1.7�

�0.5�

�1.7�

�0.5�

�1.7�

�0.5�

�1.7�

�0.5�

�1.7�

�0.5�

�1.7�

�0.5�

�____�

�1�

�1�

�____�

�____�

�1�

�1�

�1�

�____�

�____�

�____�

�____�

�2�

�3�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�4.4�

�____�

�3.6�

�12�

�3.6�

�____�

�3.6�

�____�

�7�

�7�

�3.6�

�3.6�

�____�

�____�

�10�

�3�

�3�

�1.8�

�0.5�

�1.8�

�0.5�

�1.8�

�0.5�

�1.8�

�0.5�

�1.8�

�0.5�

�1.8�

�0.5�

�1.8�

�0.5�

�1.8�

�0.5�

�____�

�1�

�1�

�____�

�____�

�1�

�1�

�1�

�____�

�____�

�____�

�____�

�2�

�3�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�____�

�4.6�

�____�

�4.2�

�15�

�4.2�

�____�

�4.2�

�____�

�7�

�7�

�4.2�

�4.2�

�____�

�____�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�cycles�

�cycles�

�Port-to-Port� Delay�

�t� CO�

�Clock-to-Clock� Offset�

�4�

�____�

�5�

�____�

�6�

�____�

�ns�

�t� OFS�

�Clock-to-Clock� Offset� for� Collision� Detection�

�Please� refer� to� Collision� Detection� Timing� Table� on� Page� 20�

�5652� tbl� 11�

�NOTES:�

�1.� The� Pipelined� output� parameters� (t� CYC2� ,� t� CD2� )� apply� to� either� or� both� left� and� right� ports� when� FT� /PIPE� X� =� V� DD� (2.5V).� Flow-through� parameters� (t� CYC1� ,� t� CD1� )�

�apply� when� FT� /PIPE� =� V� ss� (0V)� for� that� port.�

�2.� All� input� signals� are� synchronous� with� respect� to� the� clock� except� for� the� asynchronous� Output� Enable� (� OE� ),� FT� /PIPE� and� OPT.� FT� /PIPE� and� OPT� should� be�

�treated� as� DC� signals,� i.e.� steady� state� during� operation.�

�3.� These� values� are� valid� for� either� level� of� V� DDQ� (3.3V/2.5V).� See� page� 5� for� details� on� selecting� the� desired� operating� voltage� levels� for� each� port.�

�4.� 166MHz� I-Temp� is� not� available� in� the� BF-208� package.�

�5.� 200Mhz� is� not� available� in� the� BF-208� package.�

�6.� Guaranteed� by� design� (not� production� tested).�

�11�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| PR3003G-T | DIODE FAST REC 3A 200V DO-201AD |

| T95R107M010HZSL | CAP TANT 100UF 10V 20% 2824 |

| IDT70T3399S133DDI | IC SRAM 2MBIT 133MHZ 144TQFP |

| T95R107K010HZSL | CAP TANT 100UF 10V 10% 2824 |

| PR3003-T | DIODE FAST REC 3A 200V DO-201AD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70T3399S200BC | 功能描述:IC SRAM 2MBIT 200MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70T3399S200BC8 | 功能描述:IC SRAM 2MBIT 200MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70T34L20BF | 功能描述:IC SRAM 72KBIT 20NS 100FBGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF |

| IDT70T34L20PF | 功能描述:IC SRAM 72KBIT 20NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF |

| IDT70T34L20PF8 | 功能描述:IC SRAM 72KBIT 20NS 100TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:45 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,异步 存储容量:128K(8K x 16) 速度:15ns 接口:并联 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 其它名称:70V25S15PF |

发布紧急采购,3分钟左右您将得到回复。