- 您现在的位置:买卖IC网 > PDF目录9912 > IDT72285L10TFG (IDT, Integrated Device Technology Inc)IC FIFO 65536X18 LP 10NS 64STQFP PDF资料下载

参数资料

| 型号: | IDT72285L10TFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 20/25页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 65536X18 LP 10NS 64STQFP |

| 标准包装: | 80 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存储容量: | 1.1M(65K x 18) |

| 访问时间: | 10ns |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 托盘 |

| 其它名称: | 72285L10TFG |

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72275/72285

CMOS SuperSync FIFO 32,768 x 18 and 65,536 x 18

4

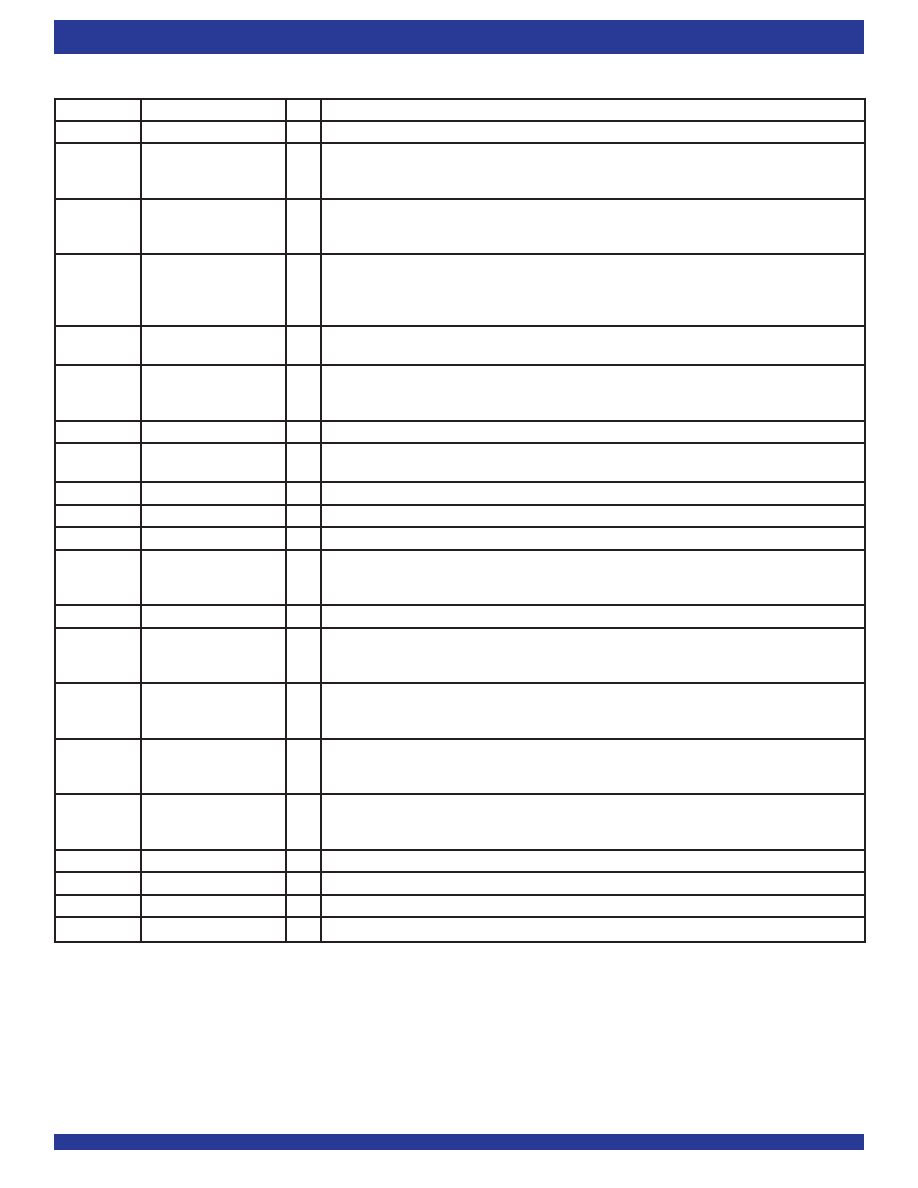

Symbol

Name

I/O

Description

D0–D17

DataInputs

I

Data inputs for a 18-bit bus.

MRS

MasterReset

I

MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During

MasterReset,theFIFOisconfiguredforeitherFWFTorIDTStandardmode,oneoftwoprogrammable

flagdefaultsettings,andserialorparallelprogrammingoftheoffsetsettings.

PRS

PartialReset

I

PRS initializes the read and write pointers to zero and sets the output register to all zeroes. During

Partial Reset, the existing mode (IDT or FWFT), programming method (serial or parallel), and

programmableflagsettingsareallretained.

RT

Retransmit

I

RT asserted on the rising edge of RCLK initializes the READ pointer to zero, sets the EF flag to LOW

(OR to HIGH in FWFT mode) temporarily and does not disturb the write pointer, programming

method,existingtimingmodeorprogrammableflagsettings.RTisusefultorereaddatafromthefirst

physicallocationoftheFIFO.

FWFT/SI

FirstWordFall

I

During Master Reset, selects First Word Fall Through or IDT Standard mode. After Master Reset,

Through/Serial In

thispinfunctionsasaserialinputforloadingoffsetregisters

WCLK

WriteClock

I

When enabled by WEN, the rising edge of WCLK writes data into the FIFO and offsets into the

programmable registers for parallel programming, and when enabled by SEN, the rising edge of

WCLKwritesonebitofdataintotheprogrammableregisterforserialprogramming.

WEN

WriteEnable

I

WEN enables WCLK for writing data into the FIFO memory and offset registers.

RCLK

Read Clock

I

WhenenabledbyREN,therisingedgeofRCLKreadsdatafromtheFIFOmemoryandoffsetsfromthe

programmableregisters.

REN

Read Enable

I

REN enables RCLK for reading data from the FIFO memory and offset registers.

OE

OutputEnable

I

OE controlstheoutputimpedanceofQn.

SEN

SerialEnable

I

SENenablesserialloadingofprogrammableflagoffsets.

LD

Load

I

DuringMasterReset,LDselectsoneoftwopartialflagdefaultoffsets(127or1,023anddeterminesthe

flagoffsetprogrammingmethod,serialorparallel.AfterMasterReset,thispinenableswritingtoandreading

fromtheoffsetregisters

DC

Don't Care

I

This pin must be tied to either VCC or GND and must not toggle after Master Reset.

FF/IR

Full Flag/

O

In the IDT Standard mode, the FF function is selected. FF indicates whether or not the FIFO memory

Input Ready

isfull.IntheFWFTmode,theIRfunctionisselected. IRindicateswhetherornotthereisspaceavailable

for writing to the FIFO memory.

EF/OR

EmptyFlag/

O

In the IDT Standard mode, the EF function is selected. EF indicates whether or not the FIFO memory

OutputReady

is empty. In FWFT mode, the OR function is selected. OR indicates whether or not there is valid data

availableattheoutputs.

PAF

Programmable

O

PAF goes LOW if the number of words in the FIFO memory is more than total word capacity of the

AlmostFullFlag

FIFO minus the full offset value m, which is stored in the Full Offset register. There are two possible

default values for m: 127 or 1,023.

PAE

Programmable

O

PAE goes LOW if the number of words in the FIFO memory is less than offset n, which is stored in the

AlmostEmptyFlag

EmptyOffsetregister.Therearetwopossibledefaultvaluesforn:127or1,023.Othervaluesforncan

be programmed into the device.

HF

Half-FullFlag

O

HF indicates whether the FIFO memory is more or less than half-full.

Q0–Q17

DataOutputs

O

Data outputs for an 18-bit bus.

VCC

Power

+5 Volt power supply pins.

GND

Ground

Groundpins.

PIN DESCRIPTION

相关PDF资料 |

PDF描述 |

|---|---|

| MS3101R20-16S | CONN RCPT 9POS PANEL MNT W/SCKT |

| MS27473T20F41P | CONN PLUG 41POS STRAIGHT W/PINS |

| IDT72285L10PFG | IC FIFO 65536X18 10NS 64TQFP |

| VE-23M-CU-B1 | CONVERTER MOD DC/DC 10V 200W |

| MAX149BCPP+ | IC ADC 10BIT SERIAL 20-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72285L15PF | 功能描述:IC FIFO 65536X18 LP 15NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72285L15PF8 | 功能描述:IC FIFO 65536X18 LP 15NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72285L15PFGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 65536X18 LP 15NS 64-TQFP |

| IDT72285L15PFGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 65536X18 LP 15NS 64-TQFP |

| IDT72285L15PFI | 功能描述:IC FIFO 65536X18 LP 15NS 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。