- 您现在的位置:买卖IC网 > PDF目录10023 > IDT72605L50J8 (IDT, Integrated Device Technology Inc)IC FIFO BI SYNC 256X18 68-PLCC PDF资料下载

参数资料

| 型号: | IDT72605L50J8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 15/17页 |

| 文件大小: | 0K |

| 描述: | IC FIFO BI SYNC 256X18 68-PLCC |

| 标准包装: | 250 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存储容量: | 9.2K(512 x 18) |

| 访问时间: | 50ns |

| 电源电压: | 4.5 V ~ 5.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 68-LCC(J 形引线) |

| 供应商设备封装: | 68-PLCC(24x24) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72605L50J8 |

7

IDT72605/72615 CMOS SYNCBiFIFO

256 x 18x 2 and 512 x 18 x 2

INDUSTRIALTEMPERATURERANGE

Data A

CSA

R/WA

ENA

OEA

I/O

Port A Operation

0

I

Data A is written on CLKA

↑. This write cycle immediately following low-impedance cycle is prohibited. Note

that even though OEA= 0, a LOW logic level on R/WA, once qualified by a rising edge on CLKA, will put Data A into

ahigh-impedancestate.

0

1

I

Data A is written on CLKA

↑

0

1

X

I

Data A is ignored

0

1

0

O

Data is read(1) from RAM array to output register on CLKA

↑, Data A is low-impedance

0

1

0

1

O

Data is read(1) from RAM array to output register on CLKA

↑, Data A is high-impedance

0

1

0

O

Outputregisterdoesnotchange(2),DataAislow-impedance

0

1

O

Outputregisterdoesnotchange(2),DataAishigh-impedance

1

0

X

I

Data A is ignored(3)

1

X

O

DataAishigh-impedance(3)

NOTES:

1. When A2A1A0 = 000, the next B

→A FIFO value is read out of the output register and the read pointer advances. If A2A1A0 = 001, the bypass path is selected and bypass

data from the Port B input register is read from the Port A output register. If A2A1A00 = 1XX, a flag offset register is selected and its offset is read out through Port A output

register.

2. Regardless of the condition of A2A1A0, the data in the Port A output register does not change and the B

→A read pointer does not advance.

3. If CSA# is HIGH, then BYPB is HIGH. No bypass occur under this condition.

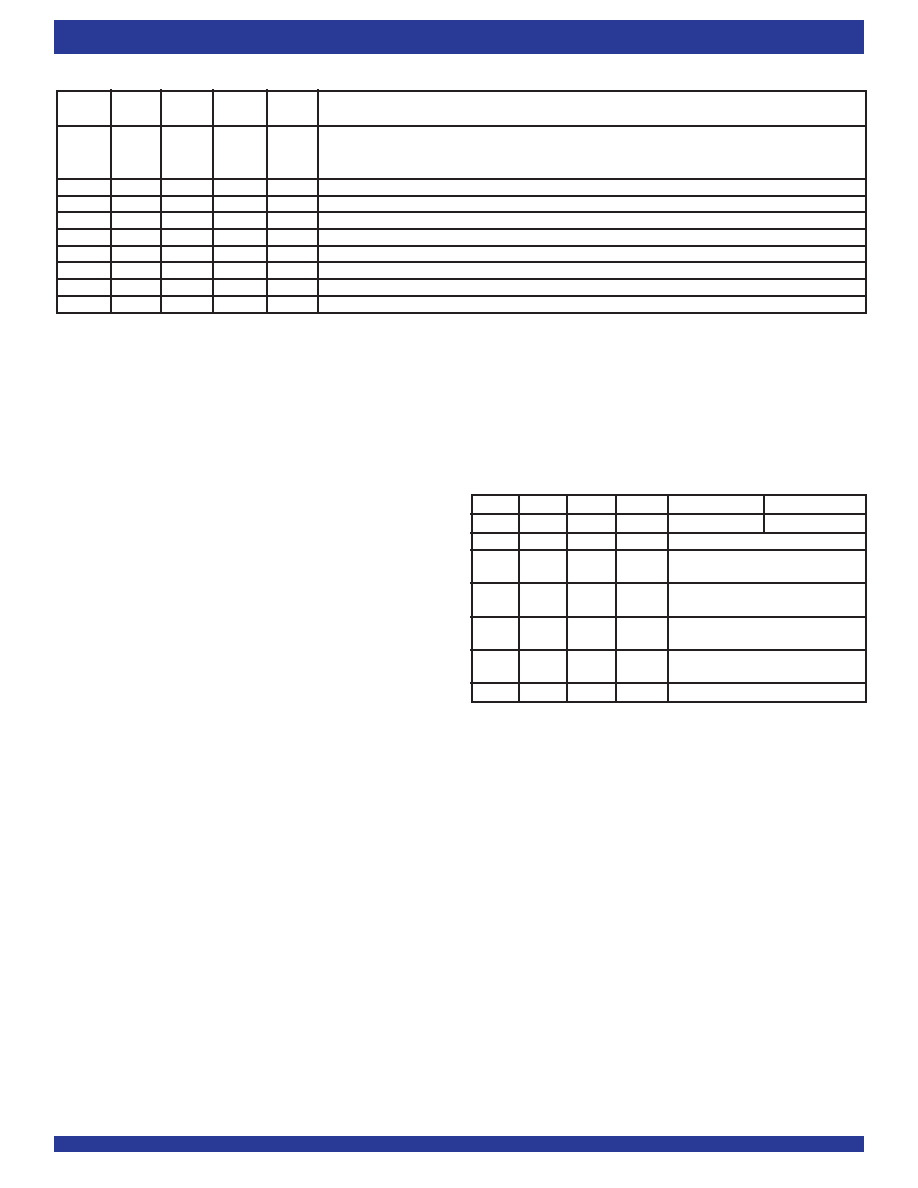

TABLE 1 PORT A OPERATION CONTROL SIGNALS

CSA

A2

A1

A0

Read

Write

0000

B

→A FIFO

A

→B FIFO

0001

18-bit Bypass Path

0100

A

→B FIFO Almost-Empty

FlagOffset

0101

A

→B FIFO Almost-Full

FlagOffset

0110

B

→A FIFO Almost-Empty

FlagOffset

0111

B

→A FIFO Almost-Full

FlagOffset

1

X

Port A Disabled

TABLE 2 ACCESSING PORT A RE-

SOURCES USING CSA, A2, A1, AND A0

ofeachportoperateindependently,PortAcanbereadingbypassdataatthe

same time Port B is reading bypass data.

When R/WA and ENA is LOW, data on pins DA0-DA17 is written into Port

Ainputregister. FollowingtherisingedgeofCLKAforthiswrite,theA

→BFull

Flag(FFAB)goesLOW. SubsequentwritesintoPortAareblockedbyinternal

logic until FFAB goes HIGH again. On the next CLKB rising edge, the A

→B

EmptyFlag(EFAB)goesHIGHindicatingtoPortBthatdataisavailable. Once

R/WBisHIGHandENBisLOW,dataisreadintothePortBoutputregister. OEB

stillcontrolswhetherPortBisinahigh-impedancestate. WhenOEBisLOW,

theoutputregisterdataappearsatDB0-DB17. EFABgoesLOWfollowingthe

CLKBrisingedgeforthisread. FFABgoesHIGHonthenextCLKArisingedge,

lettingPortAknowthatanotherwordcanbewrittenthroughthebypasspath.

Bypass data transfers from Port B to Port A work in a similar manner with

EFBA and FFBA indicating the Port A output register state.

When the Port A address changes from bypass mode (A2A1A0=001) to

FIFOmode(A2A1A0=000)ontherisingedgeofCLKA,thedataheldinthePort

Boutputregistermaybeoverwritten. UnlessPortAmonitorstheBYPBpinand

waitsforPortBtoclockoutthelastbypassword,datafromtheA

→BFIFOwill

overwrite data in the Port B output register. BYPB will go HIGH on the rising

edgeofCLKBsignifyingthatPortBhasfinisheditslastbypassoperation.Port

B must read any bypass data in the output register on this last CLKB clock or

itislostandtheSyncBiFIFOreturnstoFIFOoperations. Itisespeciallyimportant

tomonitorBYPBwhenCLKBismuchslowerthanCLKAtoavoidthiscondition.

BYPB will also go HIGH after CSA is brought HIGH; in this manner the Port B

bypass data may also be lost.

SincethePortAprocessorcontrolsCSAandthebypassmode,thisscenario

can be handled for B

→Abypassdata. ThePortAprocessormustbesetup

to read the last bypass word before leaving bypass mode.

PORT A CONTROL SIGNALS

ThePortAcontrolsignalspinsdictatethevariousoperationsshowninTable

2. Port A is accessed when CSA is LOW, and is inactive if CSA is HIGH. R/

WAandENAlinesdeterminewhenDataAcanbewrittenorread. IfR/WAand

ENAareLOW,dataiswrittenintoinputregisterontheLOW-to-HIGHtransition

ofCLKA. IfR/WAisHIGHandOEAisLOW,datacomesoutofbusandisread

fromoutputregisterintothree-statebuffer. Refertopindescriptionsformore

information.

PROGRAMMABLEFLAGS

The IDT SyncBiFIFO has eight flags: four flags for A

→B FIFO (EFAB,

PAEAB, PAFAB, FFAB), and four flags for B

→AFIFO(EFBA,PAEBA,PAFBA,

FFBA). TheEmptyandFullflagsarefixed,whiletheAlmost-EmptyandAlmost-

FulloffsetscanbesettoanydepththroughtheFlagOffsetRegisters(seeTable

3). The flags are asserted at the depths shown in the Flag Truth Table (Table

4).Afterreset,theprogrammableflagoffsetsaresetto8.ThismeanstheAlmost-

EmptyflagsareassertedatEmpty+8wordsdeep,andtheAlmost-Fullflagsare

asserted at Full -8 words deep.

ThePAEABissynchronizedtoCLKB,whilePAEABissynchronizedtoCLKA;

and PAEBA is synchronized to CLKA, while PAEBA is synchronized to CLKB.

Iftheminimumtime(tSKEW2)betweenarisingCLKBandarisingCLKAismet,

theflagwillchangestateonthecurrentclock;otherwise,theflagmaynotchange

stateuntilthenextclockrisingedge. Forthespecificflagtimings,refertoFigures

12-15.

PORT B CONTROL SIGNALS

ThePortBcontrolsignalpinsdictatethevariousoperationsshowninTable

5. Port B is independent of CSA. R/WB and ENB lines determine when Data

相关PDF资料 |

PDF描述 |

|---|---|

| MS3101A24-16S | CONN RCPT 7POS FREE HNG W/SCKT |

| MS27505E11F98S | CONN RCPT 6POS BOX MNT W/SCKT |

| VI-B6F-MW-F2 | CONVERTER MOD DC/DC 72V 100W |

| MS27466T11B35PB | CONN RCPT 13POS WALL MNT W/PINS |

| MS27466E11B35PB | CONN RCPT 13POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72605L50PF | 功能描述:IC FIFO BI SYNC 256X18 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72605L50PF8 | 功能描述:IC FIFO BI SYNC 256X18 64-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72615L20J | 功能描述:IC FIFO BY SYNC 512X18X2 68PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72615L20J8 | 功能描述:IC FIFO BY SYNC 512X18X2 68PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72615L20PF | 功能描述:IC FIFO BY SYNC 512X18X2 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:7200 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。