- 您现在的位置:买卖IC网 > PDF目录9970 > IDT72T1845L5BBI (IDT, Integrated Device Technology Inc)IC FIFO 2048X18 2.5V 5NS 144BGA PDF资料下载

参数资料

| 型号: | IDT72T1845L5BBI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 32/55页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 2048X18 2.5V 5NS 144BGA |

| 标准包装: | 1 |

| 系列: | 72T |

| 功能: | 异步,双端口 |

| 存储容量: | 36.8K(2K x 18) |

| 数据速率: | 10MHz |

| 访问时间: | 5ns |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA |

| 供应商设备封装: | 144-PBGA(13x13) |

| 包装: | 托盘 |

| 其它名称: | 72T1845L5BBI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

38

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72T1845/55/65/75/85/95/105/115/125 2.5V TeraSync 18-BIT/9-BIT FIFO 2Kx18/4Kx9, 4Kx18/

8Kx9, 8Kx18/16Kx9, 16Kx18/32Kx9, 32Kx18/64Kx9, 64Kx18/128Kx9, 128Kx18/256Kx9, 256Kx18/512Kx9, 512Kx18/1Mx9

FEBRUARY 10, 2009

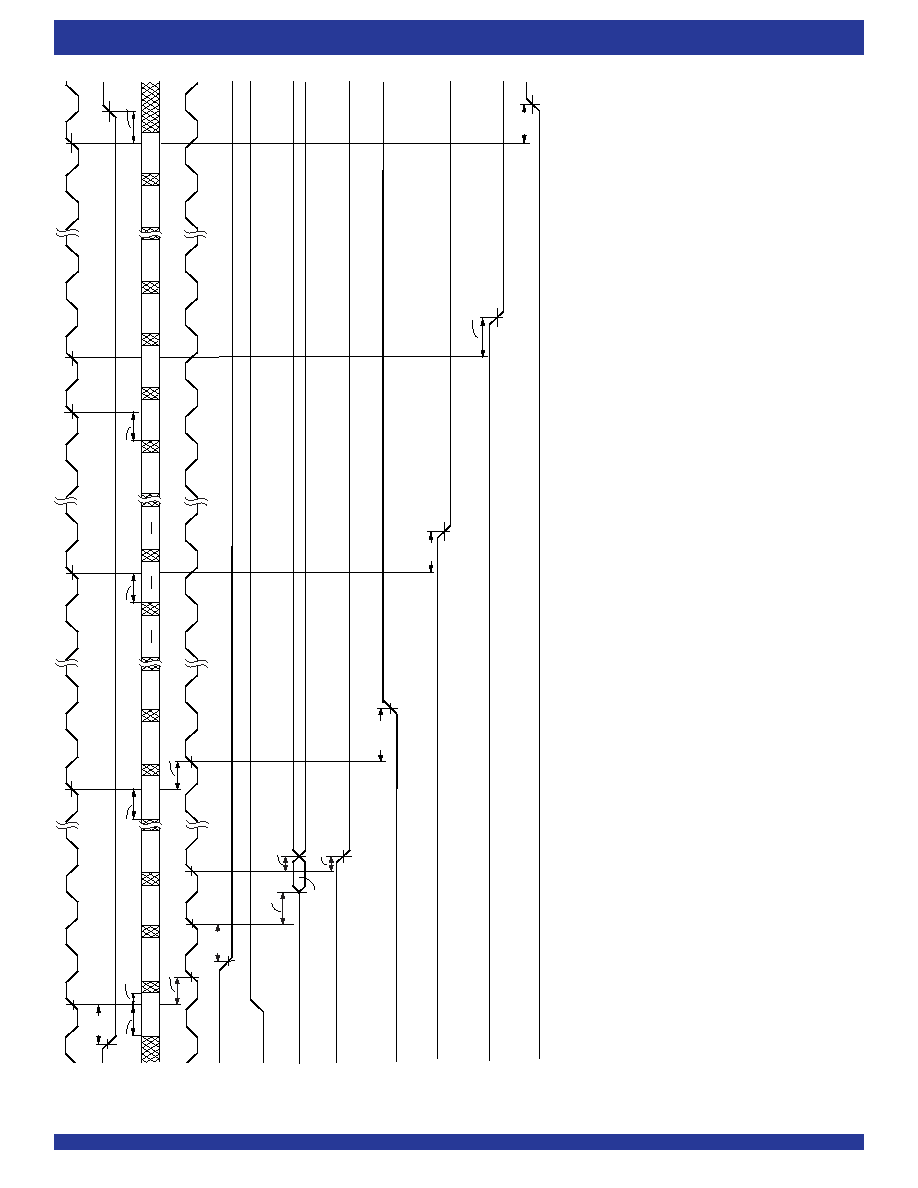

Figure

14.

Write

Timing

(First

Word

Fall

Through

Mode)

NOTES:

1.

tSKEW1

is

the

minimum

time

between

a

rising

WCLK

edge

and

a

rising

RCLK

edge

to

guarantee

that

OR

will

go

LOW

after

two

RCLK

cycles

plus

t

REF

.

If

the

time

between

the

rising

edge

of

WCLK

and

the

rising

edge

of

RCLK

is

less

than

t

SKEW1

,then

OR

assertion

may

be

delayed

one

extra

RCLK

cycle.

2.

tSKEW2

is

the

minimum

time

between

a

rising

WCLK

edge

and

a

rising

RCLK

edge

to

guarantee

that

PAE

will

go

HIGH

after

one

RCLK

cycle

plus

t

PAES

.

If

the

time

between

the

rising

edge

of

WCLK

and

the

rising

edge

of

RCLK

is

less

than

t

SKEW2

,then

the

PAE

deassertion

may

be

delayed

one

extra

RCLK

cycle.

3.

LD

=

HIGH,

OE

=

LOW

4

.

n=

PAE

offset,

m

=

PAF

offset

and

D

=

maximum

FIFO

depth.

5

.

Ifx18

input

or

x18

output

bus

width

is

selected,

D=2,049

for

IDT72T1845,

4,097

for

IDT72T1855,

8,193

for

IDT72T1865,

16,385

for

IDT72T1875,

32,769

for

IDT72T1885,

65,537

for

IDT72T1895,

131,073

for

IDT72T18105,

262,145

for

IDT72T18115,

524,288

for

IDT72T18125.

Ifboth

x9

input

and

x9

output

bus

widths

are

selected,

D=4,097

for

IDT72T1845,

8,193

for

IDT72T1855,

16,385

for

IDT72T1865,

32

,769

for

IDT72T1875,

65,537

for

IDT72T1885,

131,073

for

IDT72T1895,

262,144

for

IDT72T18105,

524,288

for

IDT72T18115,

1,048,576

for

IDT72T18125.

6

.

First

data

word

latency

=

t

SKEW1

+

2*T

RCLK

+

t

REF.

W

1

W

2

W

4

W

[n

+2]

W

[D-m-1]

W

[D-m-2]

W

[D-1]

W

D

W

[n+3]

W

[n+4]

W

[D-m]

W

[D-m+1]

WCLK

WEN

D0

-

Dn

RCLK

tDH

tDS

tSKEW1

(1)

REN

Q0

-

Qn

PAF

HF

PAE

IR

tDS

tSKEW2

tA

tREF

OR

tPAES

tHF

tPAFS

tWFF

W

[D-m+2]

W

1

tENH

5909

drw18

PREVIOUS

DATA

IN

OUTPUT

REGISTER

(2)

W

3

1

2

3

1

D-1

2

+1

]

[

W

D-1

+2

]

[

W

2

D-1

+3

]

[

W

2

1

2

tENS

RCS

tRCSLZ

tENS

相关PDF资料 |

PDF描述 |

|---|---|

| MAX11664AUB+ | IC ADC 10BIT 2CH 10UMAX |

| IDT72T1845L4-4BB | IC FIFO 2048X18 2.5V 4NS 240BGA |

| MAX11211EEE+T | ADC 18BIT DELTA-SIGMA 16-QSOP |

| VE-21M-MX-F1 | CONVERTER MOD DC/DC 10V 75W |

| IDT723663L15PF8 | IC FIFO SYNC 4096X36 128QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72T1845L6-7BB | 功能描述:IC FIFO 2048X18 6-7NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72T1855L4-4BB | 功能描述:IC FIFO 4096X18 2.5V 4NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72T1855L5BB | 功能描述:IC FIFO 4096X18 2.5V 5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72T1855L5BBI | 功能描述:IC FIFO 4096X18 2.5V 5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72T1855L6-7BB | 功能描述:IC FIFO 4096X18 6-7NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。