- 您现在的位置:买卖IC网 > PDF目录10083 > IDT72V225L15TFI8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 1024X18 15NS 64QFP PDF资料下载

参数资料

| 型号: | IDT72V225L15TFI8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 23/25页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 1024X18 15NS 64QFP |

| 标准包装: | 1,250 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 18.4K(1K x 18) |

| 访问时间: | 15ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V225L15TFI8 |

7

IDT72V205/72V215/72V225/72V235/72V245 3.3V CMOS SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

MARCH 2013

ThecontentsoftheoffsetregisterscanbereadonthedataoutputlinesQ0-

Q11 when the LD pin is set LOW and REN is set LOW. Data can then be read

onthenextLOW-to-HIGHtransitionofRCLK. ThefirsttransitionofRCLKwill

presenttheemptyoffsetvaluetothedataoutputlines.ThenexttransitionofRCLK

willpresentthefulloffsetvalue.OffsetregistercontentcanbereadoutintheIDT

Standard mode only. It cannot be read in the FWFT mode.

SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIM-

ING SELECTION

The IDT72V205/72V215/72V225/72V235/72V245 can be configured

during the "Configuration at Reset" cycle described in Table 3 with either

asynchronous or synchronous timing for PAE and PAF flags.

If asynchronous PAE/PAF configuration is selected (as per Table 3), the

PAEisassertedLOWontheLOW-to-HIGHtransitionofRCLK.PAEisresetto

HIGHontheLOW-to-HIGHtransitionofWCLK.Similarly,thePAFisasserted

LOWontheLOW-to-HIGHtransitionofWCLKandPAFisresettoHIGHonthe

LOW-to-HIGHtransitionofRCLK.Fordetailtimingdiagrams,seeFigure13for

asynchronous PAE timing and Figure 14 for asynchronous PAF timing.

IfsynchronousPAE/PAFconfigurationisselected,thePAEisassertedand

updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is

assertedandupdatedontherisingedgeofWCLKonlyandnotRCLK.Fordetail

timingdiagrams,seeFigure22forsynchronousPAEtimingandFigure23for

synchronousPAFtiming.

REGISTER-BUFFERED FLAG OUTPUT SELECTION

The IDT72V205/72V215/72V225/72V235/72V245 can be configured

duringthe"ConfigurationatReset"cycledescribedinTable4withsingle,double

ortripleregister-bufferedflagoutputsignals.Thevariouscombinationsavail-

able are described in Table 4 and Table 5. In general, going from single to

doubleortriplebufferedflagoutputsremovesthepossibilityofmetastableflag

indicationsonboundarystates(i.e,emptyorfullconditions).Thetrade-offisthe

addition of clock cycle delays for the respective flag to be asserted. Not all

combinationsof register-bufferedflagoutputsaresupported.Register-buffered

outputsapplytotheEmptyFlagandFullFlagonly. Partialflagsarenoteffected.

Table 4 and Table 5 summarize the options available.

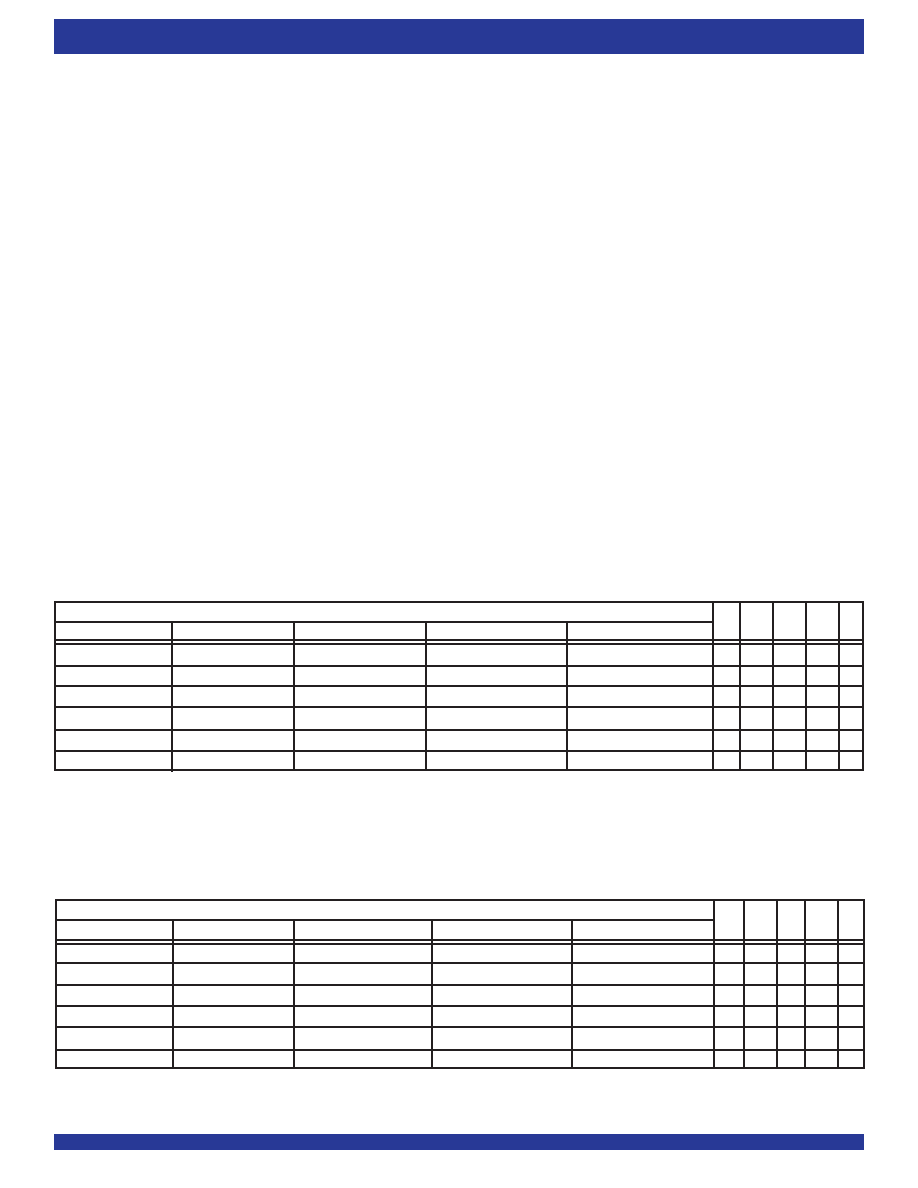

Number of Words in FIFO

IDT72V205

IDT72V215

IDT72V225

IDT72V235

IDT72V245

FF PAF

HF PAE EF

00

0

H

L

1 to n(1)

HH

H

L

H

(n + 1) to 128

(n + 1) to 256

(n + 1) to 512

(n + 1) to 1,024

(n + 1) to 2,048

H

129 to (256-(m+1))(2)

257 to (512-(m+1))(2)

513 to (1,024-(m+1))(2)

1,025 to (2,048-(m+1))(2)

2,049 to (4,096-(m+1))(2)

HH

L

H

(256-m)to255

(512-m)to511

(1,024-m)to1,023

(2,048-m)to2,047

(4,096-m)to4,095

H

L

H

256

512

1,024

2,048

4,096

L

H

TABLE 1 — STATUS FLAGS FOR IDT STANDARD MODE

TABLE 2 — STATUS FLAGS FOR FWFT MODE

Number of Words in FIFO

IDT72V205

IDT72V215

IDT72V225

IDT72V235

IDT72V245

IR PAF HF PAE OR

00

0

L

H

L

H

1 to (n + 1)(1)

LH

H

L

(n + 2) to 129

(n + 2) to 257

(n + 2) to 513

(n + 2) to 1,025

(n + 2) to 2,049

L

H

L

130 to (257-(m+1))(2)

258 to (513-(m+1))(2)

514 to (1,025-(m+1))(2)

1,026 to (2,049-(m+1))(2)

2,050 to (4,097-(m+1))(2)

LH

L

(257-m) to 256

(513-m) to 512

(1,025-m) to 1,024

(2,049-m) to 2,048

(4,097-m) to 4,096

LL

L

H

L

257

513

1,025

2,049

4,097

H

L

H

L

NOTES:

1. n = Empty Offset (Default Values : IDT72V205 n = 31, IDT72V215 n = 63, IDT72V225/72V235/72V245 n = 127)

2. m = Full Offset (Default Values : IDT72V205 m = 31, IDT72V215 m = 63, IDT72V225/72V235/72V245 m = 127)

NOTES:

1. n = Empty Offset (Default Values : IDT72V205 n = 31, IDT72V215 n = 63, IDT72V225/72V235/72V245 n = 127)

2. m = Full Offset (Default Values : IDT72V205 m = 31, IDT72V215 m = 63, IDT72V225/72V235/72V245 m = 127)

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102R32-17PX | CONN RCPT 4POS BOX MNT W/PINS |

| IDT72V225L10TF8 | IC FIFO SYNC 1024X18 10NS 64QFP |

| MS27466T23F21PC | CONN RCPT 21POS WALL MT W/PINS |

| MS3102R32-17PW | CONN RCPT 4POS BOX MNT W/PINS |

| XR5487EID-F | IC TXRX RS485 PROFIBUS 8NSOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V225L20PF | 功能描述:IC FIFO SYNC 1024X18 20NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V225L20PF8 | 功能描述:IC FIFO SYNC 1024X18 20NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V225L20TF | 功能描述:IC FIFO SYNC 1024X18 20NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V225L20TF8 | 功能描述:IC FIFO SYNC 1024X18 20NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V231L10J | 功能描述:IC FIFO SYNC 2048X9 10NS 32-PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

发布紧急采购,3分钟左右您将得到回复。