- 您现在的位置:买卖IC网 > PDF目录10009 > IDT72V3612L20PF (IDT, Integrated Device Technology Inc)IC FIFO 64X36X2 20NS 120QFP PDF资料下载

参数资料

| 型号: | IDT72V3612L20PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/24页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 64X36X2 20NS 120QFP |

| 标准包装: | 45 |

| 系列: | 72V |

| 功能: | 异步 |

| 存储容量: | 4.6K(64 x 36 x2) |

| 数据速率: | 50MHz |

| 访问时间: | 20ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-TQFP(14x14) |

| 包装: | 托盘 |

| 其它名称: | 72V3612L20PF |

10

IDT72V3612 3.3V, CMOS SyncBiFIFOTM

64 x 36 x 2

COMMERCIALTEMPERATURERANGE

andreadoperationsandarenotrelatedtohigh-impedancecontrolofthedata

outputs. If a port enable is LOW during a clock cycle, the port chip select and

write/readselectmaychangestatesduringthesetupandholdtimewindowof

thecycle.

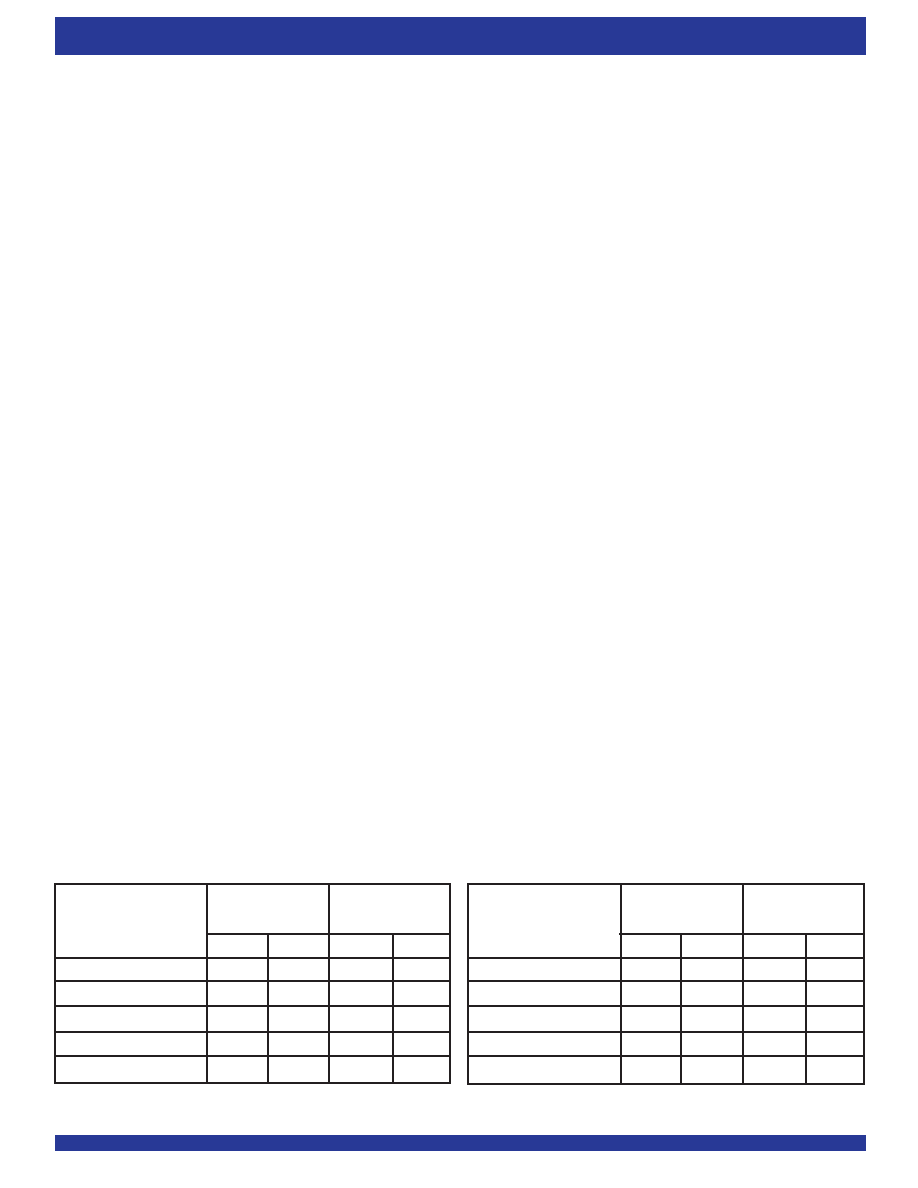

SYNCHRONIZED FIFO FLAGS

Each FIFO is synchronized to its port clock through two flip-flop stages.

This is done to improve flag reliability by reducing the probability of

metastable events on the output when CLKA and CLKB operate asynchro-

nously to one another. EFA, AEA, FFA, and AFA are synchronized by

CLKA. EFB, AEB, FFB, and AFB are synchronized to CLKB. Tables 4 and

5 show the relationship of each port flag to the level of FIFO1 and FIFO2 fill.

EMPTY FLAGS (EFA, EFB)

The Empty Flag of a FIFO is synchronized to the port clock that reads

data from its array. When the Empty Flag is HIGH, new data can be read

tothe FIFO output register. WhentheEmpty Flag is LOW,theFIFOis empty

and attempted FIFO reads are ignored.

The read pointer of a FIFO is incremented each time a new word is

clocked to the output register. The state machine that controls an Empty

Flag monitors a write-pointer and read-pointer comparator that indicates

when the FIFO memory status is empty, empty+1, or empty+2. A word

written to a FIFO can be read to the FIFO output register in a minimum of

three cycles of the Empty Flag synchronizing clock. Therefore, an Empty

Flag is LOW if a word in memory is the next data to be sent to the FIFO output

register and two cycles of the port clock that reads data from the FIFO have

not elapsed since the time the word was written. The Empty Flag of the FIFO

is set HIGH by the second LOW-to-HIGH transition of the synchronizing

clock, and the new data word can be read to the FIFO output register in the

following cycle.

A LOW-to-HIGH transition on an Empty Flag synchronizing clock begins

the first synchronization cycle of a write if the clock transition occurs at time

tSKEW1 or greater after the write. Otherwise, the subsequent clock cycle can

be the first synchronization cycle (see Figure 7 and Figure 8).

FULL FLAG (FFA, FFB)

The Full Flag of a FIFO is synchronized to the port clock that writes data

to its array. When the Full Flag is HIGH, a memory location is free in the

FIFO to receive new data. No memory locations are free when the Full Flag

is LOW and attempted writes to the FIFO are ignored.

EachtimeawordiswrittentoaFIFO,thewritepointerisincremented. The

statemachinethatcontrolsaFullFlagmonitorsawrite-pointerandreadpointer

comparatorthatindicateswhentheFIFOmemorystatusisfull,full-1,orfull-2.

Synchronized

Number of Words

to CLKB

to CLKA

in the FIFO1(1)

EFB

AEB

AFA

FFA

0L

L

H

1 to X

H

L

H

(X+1) to [64-(X+1)]

H

(64-X) to 63

H

L

H

64

H

L

Synchronized

Number of Words

to CLKB

to CLKA

in the FIFO2(1)

EFA

AEA

AFB

FFB

0L

L

H

1 to X

H

L

H

(X+1) to [64-(X+1)]

H

(64-X) to 63

H

L

H

64

H

L

NOTE:

1. X is the value in the Almost-Empty flag and Almost-Full flag offset register.

FromthetimeawordisreadfromaFIFO,thepreviousmemorylocationisready

tobewritteninaminimumofthreecyclesoftheFullFlagsynchronizingclock.

Therefore,aFullFlagisLOWiflessthantwocyclesoftheFullFlagsynchronizing

clockhaveelapsedsincethenextmemorywritelocationhasbeenread. The

secondLOW-to-HIGHtransitionontheFullFlagsynchronizationclockafterthe

readsetstheFullFlagHIGHandthedatacanbewritteninthefollowingclock

cycle.

A LOW-to-HIGH transition on a Full Flag synchronizing clock begins the

first synchronization cycle of a read if the clock transition occurs at time

tSKEW1 or greater after the read. Otherwise, the subsequent clock cycle can

be the first synchronization cycle (see Figure 9 and Figure 10).

ALMOST EMPTY FLAGS (AEA, AEB)

The Almost-Empty flag of a FIFO is synchronized to the port clock that

reads data from its array. The state machine that controls an Almost-Empty

flag monitors a write-pointer comparator that indicates when the FIFO

memory status is almost-empty, almost-empty+1, or almost-empty+2. The

almost-empty state is defined by the value of the Almost-Full and Almost-

Empty Offset register (X). This register is loaded with one of four preset

values during a device reset (see Reset section). An Almost-Empty flag is

LOW when the FIFO contains X or less words in memory and is HIGH when

the FIFO contains (X+1) or more words.

Two LOW-to-HIGH transitions of the Almost-Empty flag synchroniz-

ing clocks are required after a FIFO write for the Almost-Empty flag to reflect

the new level of fill. Therefore, the Almost-Empty flag of a FIFO containing

(X+1) or more words remains LOW if two cycles of the synchronizing clock

have not elapsed since the write that filled the memory to the (X+1) level.

An Almost-Empty flag is set HIGH by the second LOW-to-HIGH transition

of the synchronizing clock after the FIFO write that fills memory to the (X+1)

level. A LOW-to-HIGH transition of an Almost-Empty flag synchronizing

clock begins the first synchronization cycle if it occurs at time tSKEW2 or

greater after the write that fills the FIFO to (X+1) words. Otherwise, the

subsequent synchronizing clock cycle can be the first synchronization cycle

(see Figure 11 and 12).

ALMOST FULL FLAGS (AFA, AFB)

The Almost-Full flag of a FIFO is synchronized to the port clock that

writes data to its array. The state machine that controls an Almost-Full flag

monitorsawrite-pointerandread-pointercomparatorthatindicateswhenthe

FIFOmemorystatusisalmost-full,almost-full-1,oralmost-full-2. Thealmost-full

stateisdefinedbythevalueoftheAlmost-FullandAlmost-EmptyOffsetregister

(X). Thisregisterisloadedwithoneoffourpresetvaluesduringadevicereset

(seeResetsection). AnAlmost-FullflagisLOWwhentheFIFOcontains(64-

TABLE 4 – FIFO1 FLAG OPERATION

TABLE 5 – FIFO2 FLAG OPERATION

相关PDF资料 |

PDF描述 |

|---|---|

| MS27473T14B37P | CONN PLUG 37POS STRAIGHT W/PINS |

| IDT72V3611L20PF | IC FIFO SYNC 64X36 20NS 120-TQFP |

| MS3101A22-18S | CONN RCPT 8POS FREE HNG W/SCKT |

| VI-263-IW-F1 | CONVERTER MOD DC/DC 24V 100W |

| VE-26L-MY | CONVERTER MOD DC/DC 28V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3612L20PF8 | 功能描述:IC FIFO 64X36X2 20NS 120QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3612L20PQF | 功能描述:IC FIFO 64X36X2 20NS 132QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3613L12PF | 功能描述:IC FIFO CLOCK 64X36 12NS 120TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3613L12PF8 | 功能描述:IC FIFO CLOCK 64X36 12NS 120TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3613L12PQF | 功能描述:IC FIFO CLOCK 64X36 12NS 132PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。