- 您现在的位置:买卖IC网 > PDF目录10037 > IDT72V805L20PF (IDT, Integrated Device Technology Inc)IC FIFO SYNC 256X18 20NS 128QFP PDF资料下载

参数资料

| 型号: | IDT72V805L20PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 13/26页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 256X18 20NS 128QFP |

| 标准包装: | 72 |

| 系列: | 72V |

| 功能: | 异步,同步 |

| 存储容量: | 4.6K(256 x 18) |

| 数据速率: | 50MHz |

| 访问时间: | 20ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 72V805L20PF |

20

IDT72V805/72V815/72V825/72V835/72V845

3.3 V CMOS DUAL SyncFIFO 256 x 18, 512 x 18, 1,024 x 18, 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

FEBRUARY 11, 2009

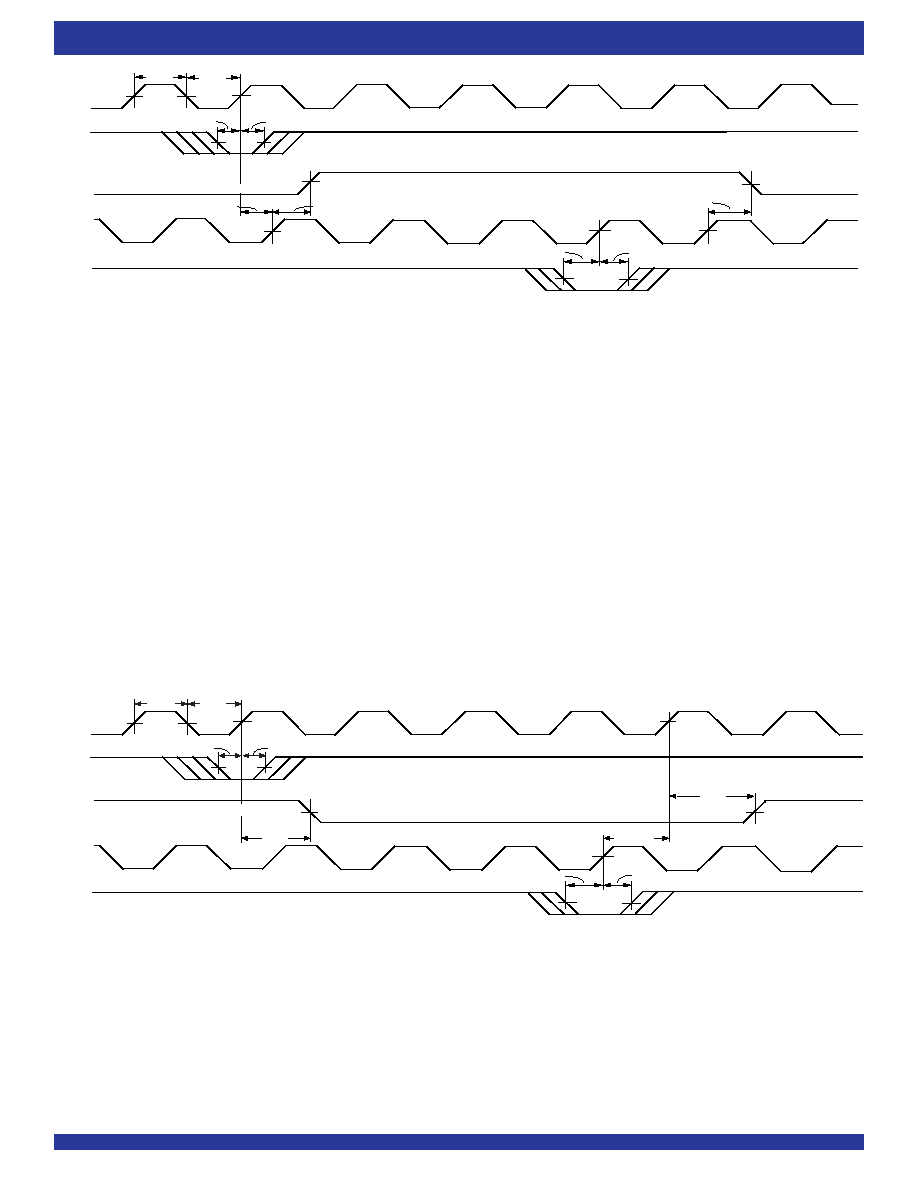

WCLK

tENH

WEN

PAE

RCLK

REN

4295 drw 22

tENS

tENH

tENS

n + 1 words in FIFO(2),

n + 2 words in FIFO(3)

tSKEW2

tPAES

n Words in FIFO(2),

n + 1 words in FIFO(3)

(4)

tPAES

n words in FIFO(2),

n + 1words in FIFO(3)

tCLKH

tCLKL

WCLK

tENH

WEN

PAF

RCLK

REN

4295 drw 23

tENS

tENH

tENS

D - m Words in FIFO

D -(m+1) Words

in FIFO

tSKEW2(3)

tPAFS

D-(m+1) Words in FIFO

tCLKL

tCLKH

Figure 22. Synchronous Programmable Almost-Empty Flag Timing (IDT Standard and FWFT Modes)

NOTES:

1. n =

PAE offset.

2. For IDT Standard Mode.

3. For FWFT Mode.

4. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge for

PAE to go HIGH during the current clock cycle. If the time between the rising edge

of WCLK and the rising edge of RCLK is less than tSKEW2, then the

PAE deassertion may be delayed one extra RCLK cycle.

5.

PAE is asserted and updated on the rising edge of RCLK only.

6. Select this mode by setting (

FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during Reset.

NOTES:

1. m =

PAF offset.

2. D = maximum FIFO Depth.

In IDT Standard Mode: D = 256 for the IDT72V805, 512 for the IDT72V815, 1,024 for the IDT72V825, 2,048 for the IDT72V835 and 4,096 for the IDT72V845. In FWFT Mode:

D = 257 for the IDT72V805, 513 for the IDT72V815, 1,025 for the IDT72V825, 2,049 for the IDT72V835 and 4,097 for the IDT72V845.

3. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge for

PAF to go HIGH during the current clock cycle. If the time between the rising edge of RCLK and

the rising edge of WCLK is less than tSKEW2, then the

PAF deassertion time may be delayed an extra WCLK cycle.

4.

PAF is asserted and updated on the rising edge of WCLK only.

5. Select this mode by setting (

FL, RXI, WXI) = (1,0,0), (1,0,1), or (1,1,0) during Reset.

Figure 23. Synchronous Programmable Almost-Full Flag Timing (IDT Standard and FWFT Modes)

相关PDF资料 |

PDF描述 |

|---|---|

| VI-BTH-MY | CONVERTER MOD DC/DC 52V 50W |

| LTC1322CSW#TR | IC TXRX RS232/485/EIA562 24SOIC |

| AD7572LN05 | IC ADC 12BIT HS LC2MOS 24-DIP |

| LTC1348ISW#TRPBF | IC TXRX 3.3V/5V RS232 28-SOIC |

| VI-J04-MX-S | CONVERTER MOD DC/DC 48V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V805L20PF8 | 功能描述:IC FIFO SYNC 256X18 20NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

| IDT72V811L10PF | 功能描述:IC FIFO SYNC 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V811L10PF8 | 功能描述:IC FIFO SYNC 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V811L10TF | 功能描述:IC FIFO SYNC 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V811L10TF8 | 功能描述:IC FIFO SYNC 512X9 10NS 64QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。