- 您现在的位置:买卖IC网 > PDF目录10037 > IDT72V815L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 512X18 15NS 128QFP PDF资料下载

参数资料

| 型号: | IDT72V815L15PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 24/26页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 512X18 15NS 128QFP |

| 标准包装: | 1,000 |

| 系列: | 72V |

| 功能: | 异步,同步 |

| 存储容量: | 9.2K(512 x 18) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V815L15PF8 |

IDT72V805/72V815/72V825/72V835/72V845

3.3 V CMOS DUAL SyncFIFO 256 x 18, 512 x 18, 1,024 x 18, 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

7

FEBRUARY 11, 2009

Number of Words in FIFO

IDT72V805

IDT72V815

IDT72V825

IDT72V835

IDT72V845

IR PAF HF PAE OR

00

0

L

H

L

H

1 to (n + 1)(1)

LH

HL

L

(n + 2) to 129

(n + 2) to 257

(n + 2) to 513

(n + 2) to 1,025

(n + 2) to 2,049

L

H

L

130 to (257-(m+1))(2)

258 to (513-(m+1))(2)

514 to (1,025-(m+1))(2)

1,026 to (2,049-(m+1))(2)

2,050 to (4,097-(m+1))(2)

LHLHL

(257-m) to 256

(513-m) to 512

(1,025-m) to 1,024

(2,049-m) to 2,048

(4,097-m) to 4,096

LL

L

H

L

257

513

1,025

2,049

4,097

H

L

H

L

normal read/write operation. When the

LD pin and WEN are again set LOW,

the next offset register in sequence is written.

The contents of the offset registers can be read on the data output lines

Q0-Q11 when the

LD pin is set LOW and REN is set LOW. Data can then

be read on the next LOW-to-HIGH transition of RCLK. The first transition

of RCLK will present the Empty Offset value to the data output lines. The

next transition of RCLK will present the Full Offset value. Offset register

content can be read out in the IDT Standard mode only. It cannot be read

in the FWFT mode.

SYNCHRONOUS VS ASYNCHRONOUS PROGRAMMABLE FLAG

TIMING SELECTION

The IDT72V805/72V815/72V825/72V835/72V845 can be configured

during the "Configuration at Reset" cycle described in Table 3 with either

asynchronous or synchronous timing for

PAE and PAF flags.

If asynchronous

PAE/PAF configuration is selected (as per Table 3), the

PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset

to HIGH on the LOW-to-HIGH transition of WCLK. Similarly, the

PAF is

asserted LOW on the LOW-to-HIGH transition of WCLK and

PAF is reset

to HIGH on the LOW-to-HIGH transition of RCLK. For detail timing dia-

grams, see Figure 13 for asynchronous

PAE timing and Figure 14 for

asynchronous

PAF timing.

If synchronous

PAE/PAF configuration is selected , the PAE is asserted

and updated on the rising edge of RCLK only and not WCLK. Similarly,

PAF

is asserted and updated on the rising edge of WCLK only and not RCLK. For

detail timing diagrams, see Figure 22 for synchronous

PAE timing and

Figure 23 for synchronous

PAF timing.

REGISTER-BUFFERED FLAG OUTPUT SELECTION

The IDT72V805/72V815/72V825/72V835/72V845 can be configured

during the "Configuration at Reset" cycle described in Table 4 with single,

double or triple register-buffered flag output signals. The various combina-

tions available are described in Table 4 and Table 5. In general, going from

single to double or triple buffered flag outputs removes the possibility of

metastable flag indications on boundary states (i.e, empty or full condi-

tions). The trade-off is the addition of clock cycle delays for the respective

flag to be asserted. Not all combinations of register-buffered flag outputs

are supported. Register-buffered outputs apply to the Empty Flag and Full

Flag only. Partial flags are not effected. Table 4 and Table 5 summarize

the options available.

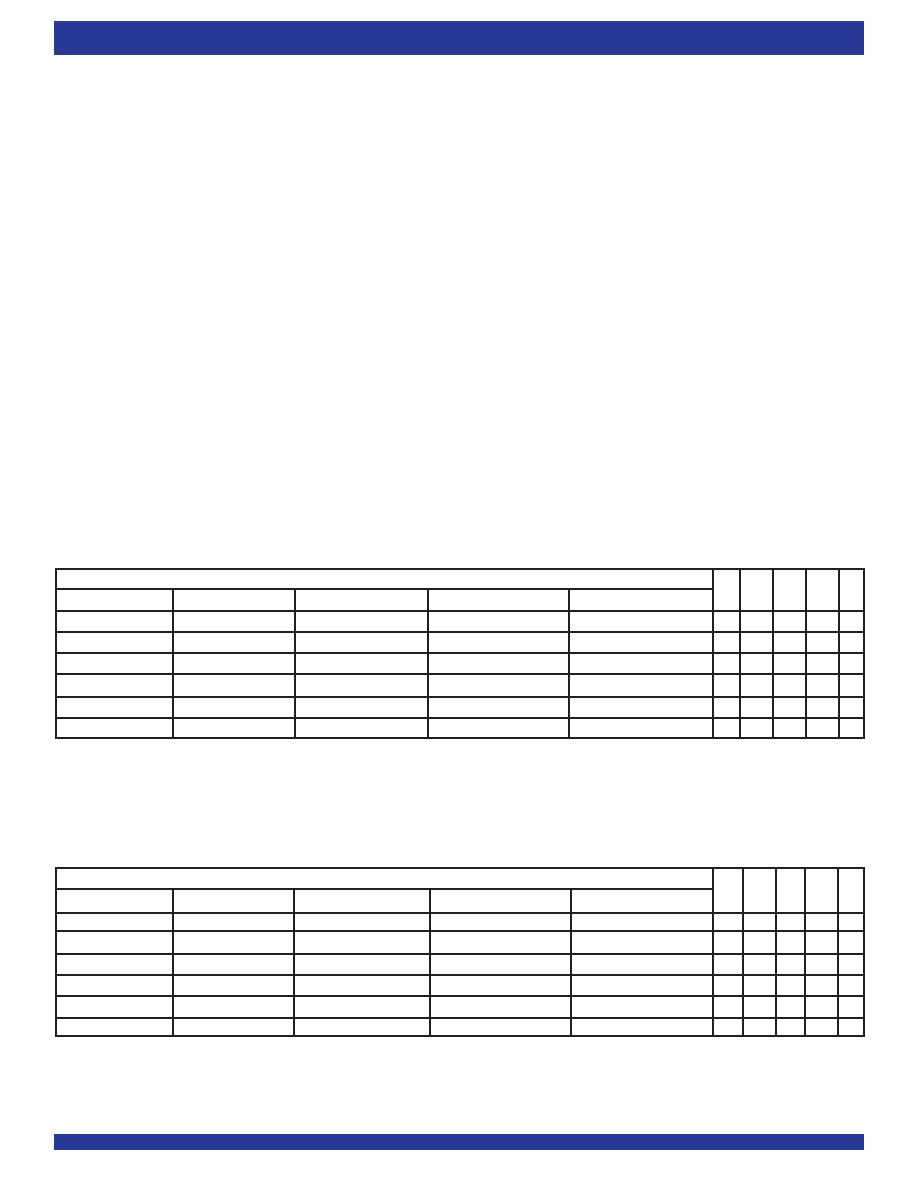

TABLE 1 — STATUS FLAGS FOR IDT STANDARD MODE

Number of Words in FIFO

IDT72V805

IDT72V815

IDT72V825

IDT72V835

IDT72V845

FF PAF HF PAE EF

00

0

H

L

1 to n(1)

HH

H

L

H

(n + 1) to 128

(n + 1) to 256

(n + 1) to 512

(n + 1) to 1,024

(n + 1) to 2,048

H

129 to (256-(m+1))(2)

257 to (512-(m+1))(2)

513 to (1,024-(m+1))(2)

1,025 to (2,048-(m+1))(2)

2,049 to (4,096-(m+1))(2)

HH

L

H

(256-m) to 255

(512-m) to 511

(1,024-m) to 1,023

(2,048-m) to 2,047

(4,096-m) to 4,095

H

L

H

256

512

1,024

2,048

4,096

L

H

TABLE 2 — STATUS FLAGS FOR FWFT MODE

NOTES:

1. n = Empty Offset (Default Values : IDT72V805 n=31, IDT72V815 n = 63, IDT72V825/72V835/72V845 n = 127)

2. m = Full Offset (Default Values : IDT72V805 m=31, IDT72V815 m = 63, IDT72V825/72V835/72V845 m = 127)

NOTES:

1. n = Empty Offset (Default Values : IDT72V805 n = 31, IDT72V815 n = 63, IDT72V825/72V835/72V845 n = 127)

2. m = Full Offset (Default Values : IDT72V805 m = 31, IDT72V815 m = 63, IDT72V825/72V835/72V845 m = 127)

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72815LB15PF8 | IC FIFO SYNC DUAL 512X18 128TQFP |

| VI-BNR-IV-F3 | CONVERTER MOD DC/DC 7.5V 150W |

| VI-B5Z-MY | CONVERTER MOD DC/DC 2V 20W |

| VI-BNR-IV-F2 | CONVERTER MOD DC/DC 7.5V 150W |

| MS27467T21A35P | CONN PLUG 79POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V815L15PFI | 功能描述:IC FIFO SYNC 512X18 15NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V815L15PFI8 | 功能描述:IC FIFO SYNC 512X18 15NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V815L20PF | 功能描述:IC FIFO SYNC 512X18 20NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V815L20PF8 | 功能描述:IC FIFO SYNC 512X18 20NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V81L15PA | 功能描述:IC FIFO ASYNCH 512X9 56TSSOP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:80 系列:7200 功能:同步 存储容量:18.4K(1K x 18) 数据速率:- 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(10x10) 包装:托盘 其它名称:72225LB10TF |

发布紧急采购,3分钟左右您将得到回复。