- 您现在的位置:买卖IC网 > PDF目录65590 > IDT74LVC161ADC8 (INTEGRATED DEVICE TECHNOLOGY INC) LVC/LCX/Z SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, PDSO16 PDF资料下载

参数资料

| 型号: | IDT74LVC161ADC8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 计数器 |

| 英文描述: | LVC/LCX/Z SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, PDSO16 |

| 封装: | SOIC-16 |

| 文件页数: | 1/7页 |

| 文件大小: | 194K |

| 代理商: | IDT74LVC161ADC8 |

INDUSTRIALTEMPERATURERANGE

IDT74LVC161A

3.3VCMOSPRESETTABLE SYNCHRONOUS 4-BIT BINARY COUNTER

1

OCTOBER 1999

INDUSTRIAL TEMPERATURE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

1999 Integrated Device Technology, Inc.

DSC-5156/3

FEATURES:

0.5 MICRON CMOS Technology

ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

VCC = 3.3V ± 0.3V, Normal Range

VCC = 2.7V to 3.6V, Extended Range

CMOS power levels (0.4

μμμμμ W typ. static)

Rail-to-Rail output swing for increased noise margin

All inputs, outputs, and I/Os are 5V tolerant

Supports hot insertion

Available in SOIC and TSSOP packages

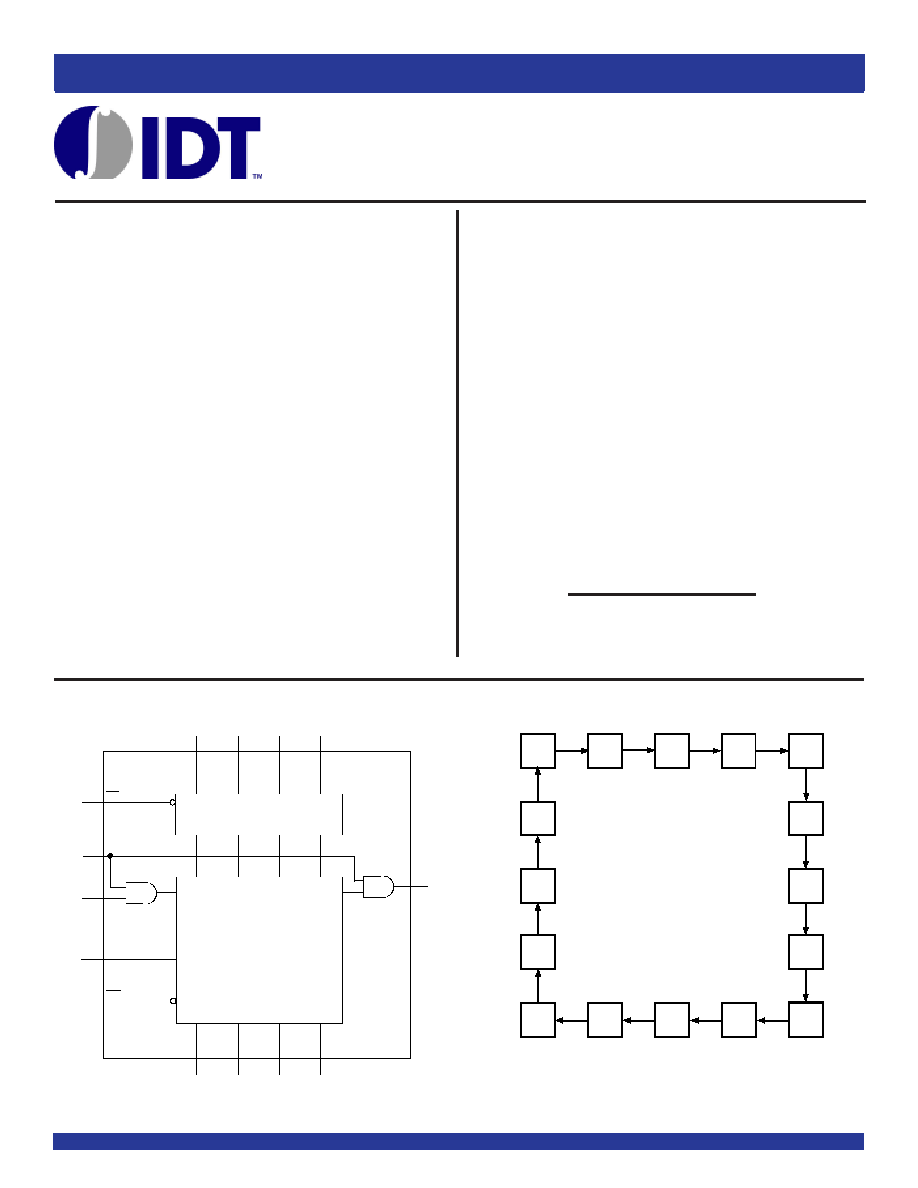

FUNCTIONAL DIAGRAM

DRIVE FEATURES:

High Output Drivers: ±24mA

Reduced system switching noise

APPLICATIONS:

5V and 3.3V mixed voltage systems

Data communication and telecommunication systems

IDT74LVC161A

DESCRIPTION:

The LVC161A is a high-performance, low-power, low-voltage, Si-gate

CMOS device, superior to most advanced CMOS-compatible TTL families.

The LVC161A is a presettable synchronous binary counter which

3.3V CMOS PRESETTABLE

SYNCHRONOUS 4-BIT BINARY

COUNTER WITH ASYNCHRONOUS

RESET, 5 VOLT TOLERANT I/O

STATE DIAGRAM

Inputs can be driven from either 3.3V or 5V devices. This feature allows

the use of this device as a translator in a mixed 3.3V/5V supply system.

f

max =

tp

(max) (CP to TC) + tsu (CEP to CP)

1

01

2

3

4

5

6

7

8

9

10

11

12

13

14

15

PARALLEL LOAD

CIRCUITRY

BINARY COUNTER

34

5

6

14

13

12

11

Q0

Q1

Q2

Q3

D0

D1

D2

D3

PE

CET

CEP

CP

MR

TC

9

10

7

2

1

15

features an internal look-ahead carry and can be used for high-speed

counting. Synchronous operation is provided by having all flip-flops clocked

simultaniously on the positive-going edge of the clock (CP). Outputs (Q

0 to

Q

3) of the counters may be preset to a high or low level. A low level at the

parallel enable input (

PE) disables the counting action and causes the data

at inputs (D

0 to D3) to be loaded into the counter on the positive-going edge

of the clock (provided that the set-up and hold time requirements for

PE are

met). Preset takes place regardless of the levels at the count enable inputs

(CEP and CET). A low level at the master reset input (

MR)setsallfouroutputs

of the flip-flops (Q

0 to Q3) to low level regardless of the levels at CP, PE, CET,

and CEP inputs (thus providing an asynchronous clear function).

The look-ahead carry simplifies serial cascading of the counters. Both

count enable inputs (CEP and CET) must be high to count. The CET input

is fed forward to enable the terminal count output (TC). The TC output thus

enabled will produce a high output pulse of a duration approximately equal

to a high level output of Q

0. This pulse can be used to enable the next

cascaded stage. The maximum clock frequency for the cascaded counters

is determined by the CP to TC propagation delay and CEP to CP set-up time,

according to the following formula:

相关PDF资料 |

PDF描述 |

|---|---|

| IDT74LVC162245APFG | LVC/LCX/Z SERIES, DUAL 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO48 |

| IDT74LVC16241APV | LVC/LCX/Z SERIES, QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| IDT74LVC16241APV8 | LVC/LCX/Z SERIES, QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| IDT74LVC16241APF | LVC/LCX/Z SERIES, QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| IDT74LVC16241APF8 | LVC/LCX/Z SERIES, QUAD 4-BIT DRIVER, TRUE OUTPUT, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74LVC162244APA | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT74LVC162244APAG | 功能描述:IC BUFF DVR TRI-ST 16BIT 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:74LVC 标准包装:2,000 系列:74LVCH 逻辑类型:缓冲器/线路驱动器,非反相 元件数:2 每个元件的位元数:4 输出电流高,低:24mA,24mA 电源电压:1.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:20-SOIC(0.295",7.50mm 宽) 供应商设备封装:20-SOIC 包装:带卷 (TR) |

| IDT74LVC162244APAG8 | 功能描述:IC BUFF DVR TRI-ST 16BIT 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:74LVC 标准包装:47 系列:74LVX 逻辑类型:缓冲器/线路驱动器,非反相 元件数:4 每个元件的位元数:1 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.209",5.30mm 宽) 供应商设备封装:14-SOIC 包装:管件 |

| IDT74LVC162244APFG | 功能描述:IC BUFF DVR TRI-ST 16BIT 48TVSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:74LVC 标准包装:47 系列:74LVX 逻辑类型:缓冲器/线路驱动器,非反相 元件数:4 每个元件的位元数:1 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.209",5.30mm 宽) 供应商设备封装:14-SOIC 包装:管件 |

| IDT74LVC162244APFG8 | 功能描述:IC BUFF DVR TRI-ST 16BIT 48TVSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 缓冲器,驱动器,接收器,收发器 系列:74LVC 标准包装:47 系列:74LVX 逻辑类型:缓冲器/线路驱动器,非反相 元件数:4 每个元件的位元数:1 输出电流高,低:4mA,4mA 电源电压:2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:14-SOIC(0.209",5.30mm 宽) 供应商设备封装:14-SOIC 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。