- 您现在的位置:买卖IC网 > PDF目录9717 > IDT74SSTU32865BKG (IDT, Integrated Device Technology Inc)IC BUFFER 28BIT 1:2 REG 160TFBGA PDF资料下载

参数资料

| 型号: | IDT74SSTU32865BKG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 15/15页 |

| 文件大小: | 0K |

| 描述: | IC BUFFER 28BIT 1:2 REG 160TFBGA |

| 产品变化通告: | Product Discontinuation 09/Dec/2011 |

| 标准包装: | 119 |

| 逻辑类型: | 1:2 寄存缓冲器,带奇偶位 |

| 位数: | 28 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-LFBGA |

| 供应商设备封装: | 160-CABGA(9x13) |

| 包装: | 托盘 |

| 其它名称: | 74SSTU32865BKG |

9

COMMERCIALTEMPERATURERANGE

IDT74SSTU32865

28-BIT 1:2 REGISTERED BUFFER WITH PARITY

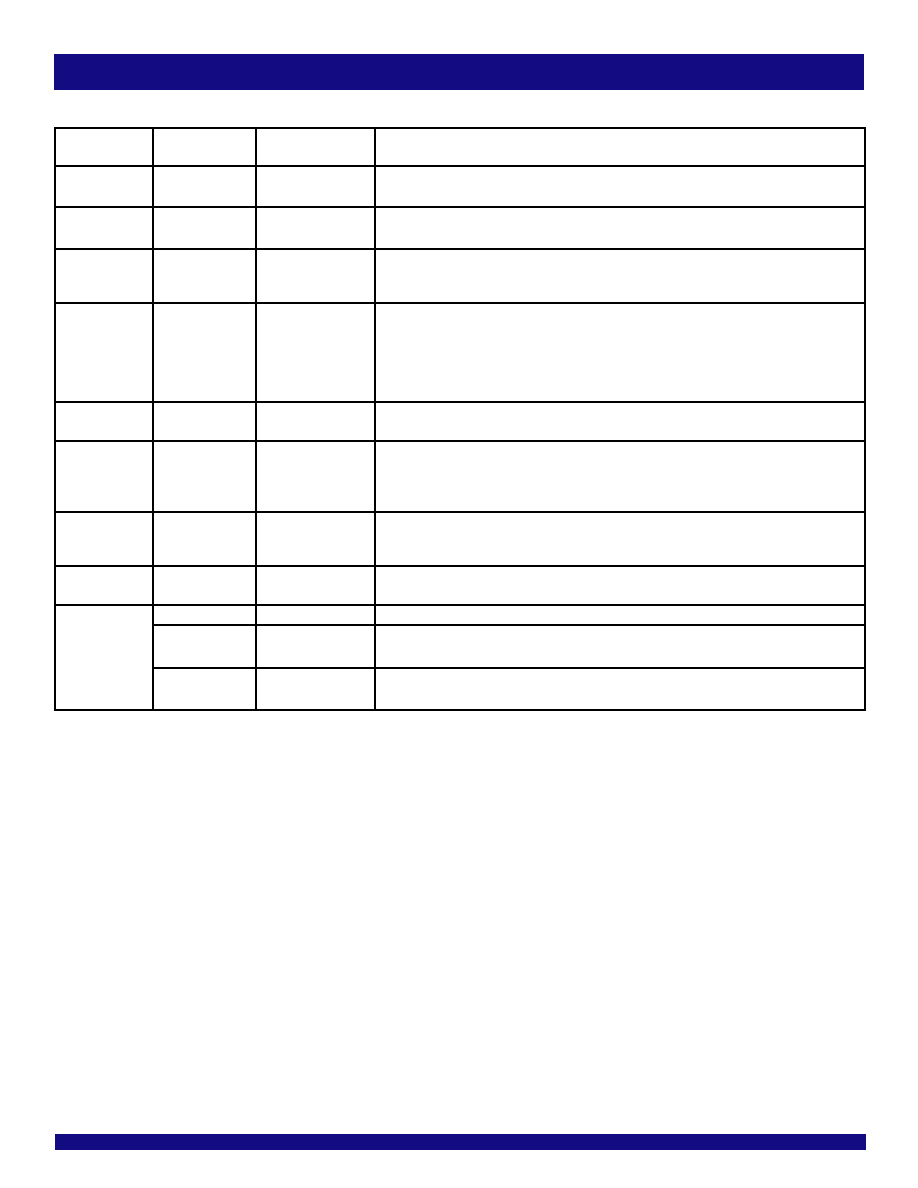

TERMINAL FUNCTIONS

Signal

Terminal

Group

Name

Type

Description

UngatedInputs

DCKE0, DCKE1

SSTL_18

DRAM function pins not associated with Chip Select

DODT0,DODT1

Chip Select

D0:D21

SSTL_18

DRAM inputs, re-driven only when Chip Select is LOW

GatedInputs

ChipSelectInputs

DCS0, DCS1

SSTL_18

DRAM Chip Select signals. These pins initiate DRAM address/command decodes, and as such at

leastonewillbeLOWwhenavalidaddress/commandispresent. Theregistercanbeprogrammed

to re-drive all D-inputs only (CSGateEN HIGH) when at least one Chip Select input is LOW.

Re-DrivenOutputs

Q0A:Q21A

SSTL_18

Outputsoftheregister,validafterthespecifiedclockcountandimmediatelyfollowingarisingedge

Q0B:Q21B

of theclock

QCS0-1A, B

QCKE0-1A, B

QODT0-1A, B

ParityInput

PARIN

SSTL_18

InputparityisreceivedonpinPARIN,andshouldmaintainoddparityacrosstheD0:D21inputs,atthe

risingedgeoftheclock

ParityErrorOutput

PTYERR

OpenDrain

WhenLOW,thisoutputindicatesthataparityerrorwasidentifiedassociatedwiththeaddressand/or

command inputs. PTYERR will be active for two clock cycles, and delayed by an additional clock

cycleforcompatibilitywithfinalparityouttimingontheindustry-standardDDR-IIregisterwithparity(in

JEDECdefinition).

ProgramInputs

CSGateEN

1.8V LVCMOS

ChipSelectGateEnable. WhenHIGH,theD0:D21inputswillbelatchedonlywhenatleastoneChip

SelectinputisLOWduringtherisingedgeoftheclock. WhenLOW,theD0:D21inputswillbelatched

and redriven on every rising edge of the clock.

Clock Inputs

CLK, CLK

SSTL_18

Differentialmasterclockinputpairtotheregister. Theregisteroperationistriggeredbyarisingedgeon

the positive clock input (CLK).

Miscellaneous

MCL, MCH

Must be connected to a Logic LOW or HIGH.

Inputs

RESET

1.8V LVCMOS

AsynchronousResetInput. WhenLOW,itcausesaresetoftheinternallatches,therebyforcingthe

outputs LOW. RESET also resets the PTYERR signal.

VREF

0.9Vnominal

InputreferencevoltageforSSTL_18inputs. Twopins(internallytiedtogether)areusedforincreased

reliability.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-20M-MX-F2 | CONVERTER MOD DC/DC 10V 75W |

| AR1100T-I/MQ | IC TOUCH SCREEN CTLR 20-QFN |

| VI-203-MX-F4 | CONVERTER MOD DC/DC 24V 75W |

| AR1100T-I/SS | IC TOUCH SCREEN CTLR 20-SSOP |

| VI-203-MX-F3 | CONVERTER MOD DC/DC 24V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74SSTU32865BKG8 | 功能描述:IC BUFFER 28BIT 1:2 REG 160TFBGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTU32866BBFG | 功能描述:IC BUFFER 1.8V CONFIG 96-BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTU32866BBFG8 | 功能描述:IC BUFFER 1.8V CONFIG 96-BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTU32D868BKG | 功能描述:IC BUFFER 28BIT 1:2 REG 176TFBGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTU32D868BKG8 | 功能描述:IC BUFFER 28BIT 1:2 REG 176TFBGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。