- 您现在的位置:买卖IC网 > PDF目录9717 > IDT74SSTUBH32865ABKG (IDT, Integrated Device Technology Inc)IC BUFFER 28BIT 1:2 REG 160-BGA PDF资料下载

参数资料

| 型号: | IDT74SSTUBH32865ABKG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 2/17页 |

| 文件大小: | 0K |

| 描述: | IC BUFFER 28BIT 1:2 REG 160-BGA |

| 产品变化通告: | Product Discontinuation 09/Dec/2011 |

| 标准包装: | 119 |

| 逻辑类型: | 1:2 寄存缓冲器,带奇偶位 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 位数: | 28 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-LFBGA |

| 供应商设备封装: | 160-CABGA(9x13) |

| 包装: | 托盘 |

| 其它名称: | 74SSTUBH32865ABKG |

IDT74SSTUBH32865A

28-BIT 1:2 REGISTERED BUFFER FOR DDR2

COMMERCIAL TEMPERATURE GRADE

28-BIT 1:2 REGISTERED BUFFER FOR DDR2

10

IDT74SSTUBH32865A

7103/10

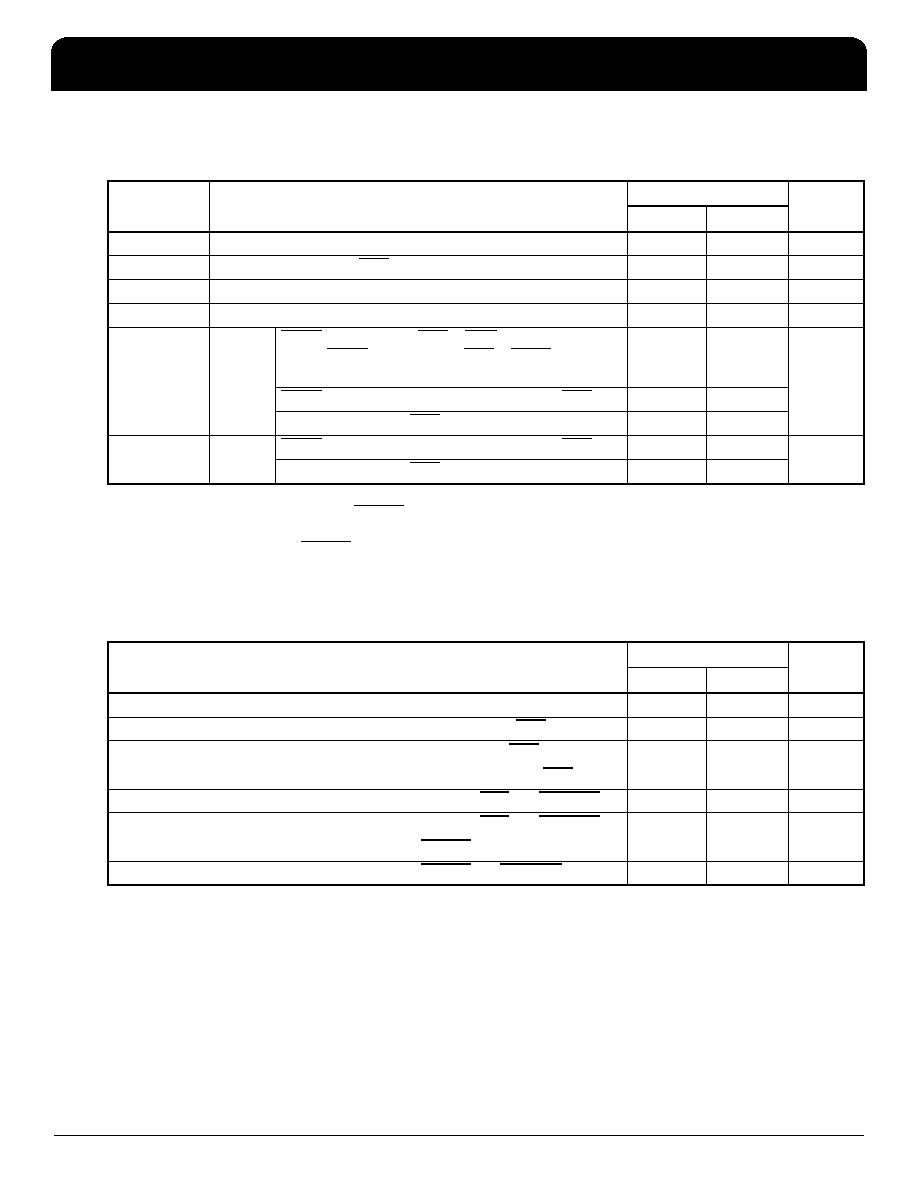

Timing Requirements Over Recommended Operating Free-Air Temperature

Range

Switching Characteristics Over Recommended Free Air Operating Range

(unless otherwise noted)

Symbol

Parameter

VDD = 1.8V ± 0.1V

Units

Min.

Max.

fCLOCK

Clock Frequency

410

MHz

tW

Pulse Duration; CLK, CLK HIGH or LOW

1

ns

tACT

Differential Inputs Active Time1

1

VREF must be held at a valid input voltage level and data inputs must be held at valid logic levels for a

minimum time of tACT(max) after RESET is taken HIGH.

10

ns

tINACT

Differential Inputs Inactive Time2

2

VREF, data, and clock inputs must be held at a valid input voltage levels (not floating) for a minimum

time of tINACT(max) after RESET is taken LOW.

15

ns

tSU

Setup

Time

DCS0 before CLK

↑, CLK↓, DCS and CSGateEN

HIGH; DCS1 before CLK

↑, CLK↓, DCS0 and

CSGateEN HIGH

0.6

ns

DCSn, DODT, DCKE, and Dn after CLK

↑, CLK↓

0.5

PARIN after CLK

↑, CLK↓

0.5

tH

Hold

Time

DCSn, DODT, DCKE, and Dn after CLK

↑, CLK↓

0.4

ns

PARIN after CLK

↑, CLK↓

0.4

Symbol

Parameter

VDD = 1.8V ± 0.1V

Units

Min.

Max.

fMAX

Max Input Clock Frequency

410

MHz

tPDM1

1

Design target as per JEDEC specifications.

Propagation Delay, single bit switching, CLK

↑ to CLK↓ to Qn

1.1

1.6

ns

tPDQ2

2

Production Test. (See Production Test Circuit in TEST CIRCUIT AND WAVEFORM section.)

Propagation Delay, single-bit switching, CLK

↑ / CLK↓ to Qn

0.4

0.8

ns

tPDMSS1

Propagation Delay, simultaneous switching, CLK

↑ to CLK↓ to Qn

1.7

ns

tLH

LOW to HIGH Propagation Delay, CLK

↑ to CLK↓ to PTYERR

1.2

3

ns

tHL

HIGH to LOW Propagation Delay, CLK

↑ to CLK↓ to PTYERR

13

ns

tPHL

HIGH to LOW Propagation Delay, RESET

↓ to Qn↓

3ns

tPLH

LOW to HIGH Propagation Delay, RESET

↓ to PTYERR↑

3ns

相关PDF资料 |

PDF描述 |

|---|---|

| VE-JWK-MX-F4 | CONVERTER MOD DC/DC 40V 75W |

| VE-B4N-IV-B1 | CONVERTER MOD DC/DC 18.5V 150W |

| MS3451W16S-8S | CONN RCPT 5POS CBL MNT W/SCKT |

| IDT74SSTUBF32865ABK | IC BUFFER 28BIT 1:2 REG 160-BGA |

| VE-B4M-IV-B1 | CONVERTER MOD DC/DC 10V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT74SSTUBH32865ABKG8 | 功能描述:IC BUFFER 28BIT 1:2 REG 160-BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTUBH32868ABKG | 功能描述:IC BUFFER 28BIT CONF DDR2 176BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTUBH32868ABKG8 | 功能描述:IC BUFFER 28BIT CONF DDR2 176BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| IDT74SSTV16857PA | 制造商:Integrated Device Technology Inc 功能描述:SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 |

| IDT74SSTV16857PAG | 功能描述:IC BUFFER 14BIT SSTL I/O 48TSSOP RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:74SSTV 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。