- 您现在的位置:买卖IC网 > PDF目录9971 > IDT82V2084PF (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 4CH 128-TQFP PDF资料下载

参数资料

| 型号: | IDT82V2084PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 16/75页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 4CH 128-TQFP |

| 标准包装: | 15 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 82V2084PF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

23

INDUSTRIAL

TEMPERATURE RANGES

QUAD CHANNEL T1/E1/J1 LONG HAUL/SHORT HAUL LINE INTERFACE UNIT

3.4

JITTER ATTENUATOR

ThereisoneJitterAttenuatorineachchanneloftheLIU.TheJitterAtten-

uator can be deployed in the transmit path or the receive path, and can also

be disabled. This is selected by the JACF[1:0] bits (JACF, 01H...).

3.4.1

JITTER ATTENUATION FUNCTION DESCRIPTION

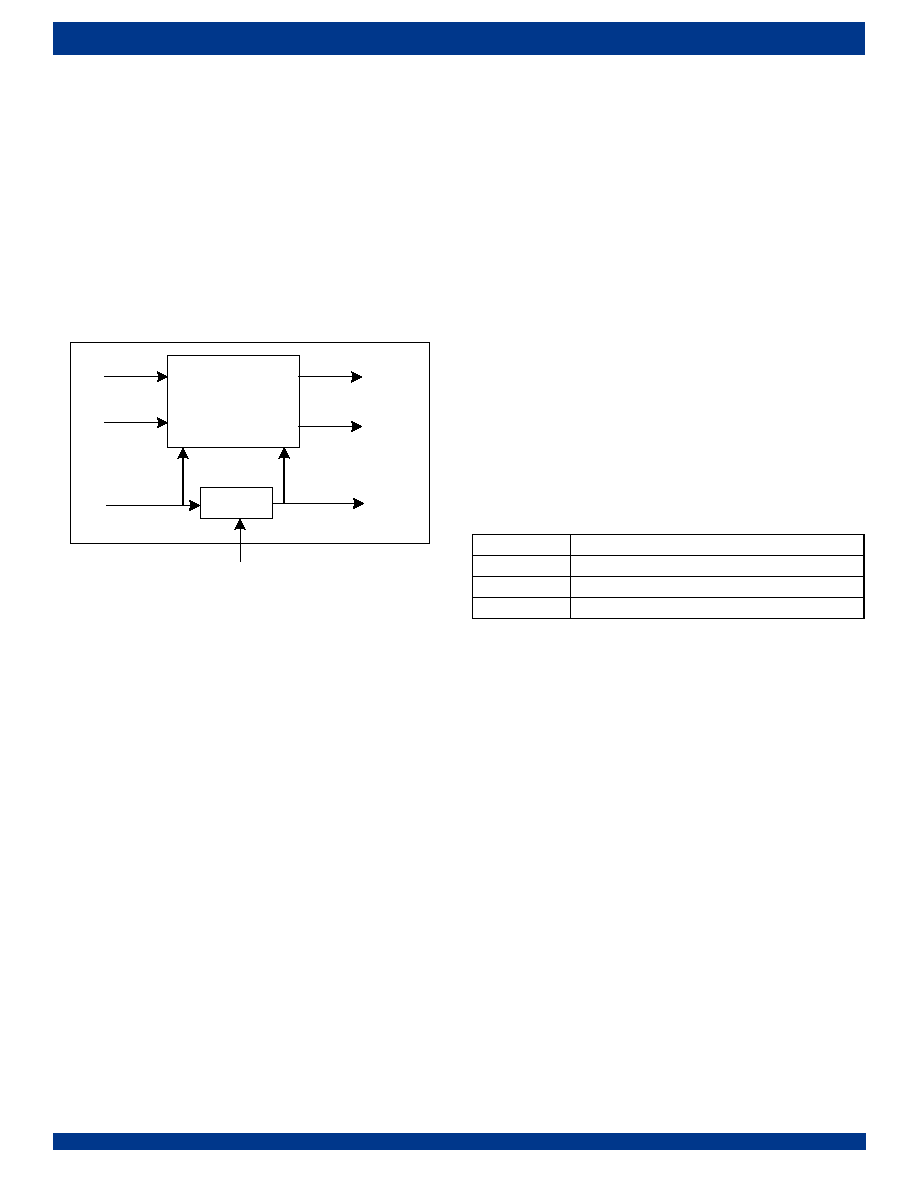

The Jitter Attenuator is composed of a FIFO and a DPLL, as shown in

Figure-12. The FIFO is used as a pool to buffer the jittered input data, then

the data is clocked out of the FIFO by a de-jittered clock. The depth of the

FIFO can be 32 bits, 64 bits or 128 bits, as selected by the JADP[1:0] bits

(JACF, 01H...). Consequently, the constant delay of the Jitter Attenuator

will be 16 bits, 32 bits or 64 bits. Deeper FIFO can tolerate larger jitter, but

at the expense of increasing data latency time.

Figure-12 Jitter Attenuator

In E1 applications, the Corner Frequency of the DPLL can be 0.9 Hz or

6.8 Hz, as selected by the JABW bit (JACF, 01H...). In T1/J1 applications,

the Corner Frequency of the DPLL can be 1.25 Hz or 5.00 Hz, as selected

by the JABW bit (JACF, 01H...). The lower the Corner Frequency is, the

longer time is needed to achieve synchronization.

When the incoming data moves faster than the outgoing data, the FIFO

will overflow. This overflow is captured by the JAOV_IS bit (INTS1, 17H...).

If the incoming data moves slower than the outgoing data, the FIFO will

underflow. This underflow is captured by the JAUD_IS bit (INTS1, 17H...).

For some applications that are sensitive to data corruption, the JA limit

mode can be enabled by setting JA_LIMIT bit (JACF, 01H...) to ‘1’. In the

JA limit mode, the speed of the outgoing data will be adjusted automatically

when the FIFO is close to its full or emptiness. The criteria of starting speed

adjustment are shown in Table-16. The JA limit mode can reduce the pos-

sibility of FIFO overflow and underflow, but the quality of jitter attenuation

is deteriorated.

3.4.2

JITTER ATTENUATOR PERFORMANCE

The performance of the Jitter Attenuator in the IDT82V2084 meets the

ITU-T I.431, G.703, G.736-739, G.823, G.824, ETSI 300011, ETSI TBR12/

13, AT&T TR62411 specifications. Details of the Jitter Attenuator perfor-

mance is shown in Table-68 Jitter Tolerance and Table-69 Jitter Attenuator

FIFO

32/64/128

DPLL

Jittered Data

De-jittered Data

Jittered Clock

De-jittered Clock

MCLK

W

R

RCLKn

RDn/RDPn

RDNn

Table-16 Criteria of Starting Speed Adjustment

FIFO Depth

Criteria for Adjusting Data Outgoing Speed

32 Bits

2 bits close to its full or emptiness

64 Bits

3 bits close to its full or emptiness

128 Bits

4 bits close to its full or emptiness

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82P2284BBG8 | TXRX T1/J1/E1 4CHAN 208-PBGA |

| IDT72V273L10PF8 | IC FIFO 16384X18 10NS 80QFP |

| MAX11619EEE+T | IC ADC 10BIT 4CH 16QSOP |

| IDT82P2284BB8 | TXRX T1/J1/E1 4CHAN 208-PBGA |

| MS27473T12B35SB | CONN PLUG 22POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2084PF8 | 功能描述:IC LIU T1/J1/E1 4CH 128-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2084PFG | 功能描述:IC LIU T1/J1/E1 4CH 128-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2084PFG8 | 功能描述:IC LINE INTERFC UNIT 4CH 128TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2088 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL CHANNEL T1/E1/J1 LONG HAUL/ SHORT HAUL LINE INTERFACE UNIT |

| IDT82V2088_08 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL CHANNEL T1/E1/J1 LONG HAUL/ SHORT HAUL LINE INTERFACE UNIT |

发布紧急采购,3分钟左右您将得到回复。