- 您现在的位置:买卖IC网 > PDF目录1924 > IDT82V2084PFG (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 4CH 128-TQFP PDF资料下载

参数资料

| 型号: | IDT82V2084PFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 37/75页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 4CH 128-TQFP |

| 标准包装: | 15 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 82V2084PFG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

42

INDUSTRIAL

TEMPERATURE RANGES

QUAD CHANNEL T1/E1/J1 LONG HAUL/SHORT HAUL LINE INTERFACE UNIT

4.2.5

NETWORK DIAGNOSTICS CONTROL REGISTERS

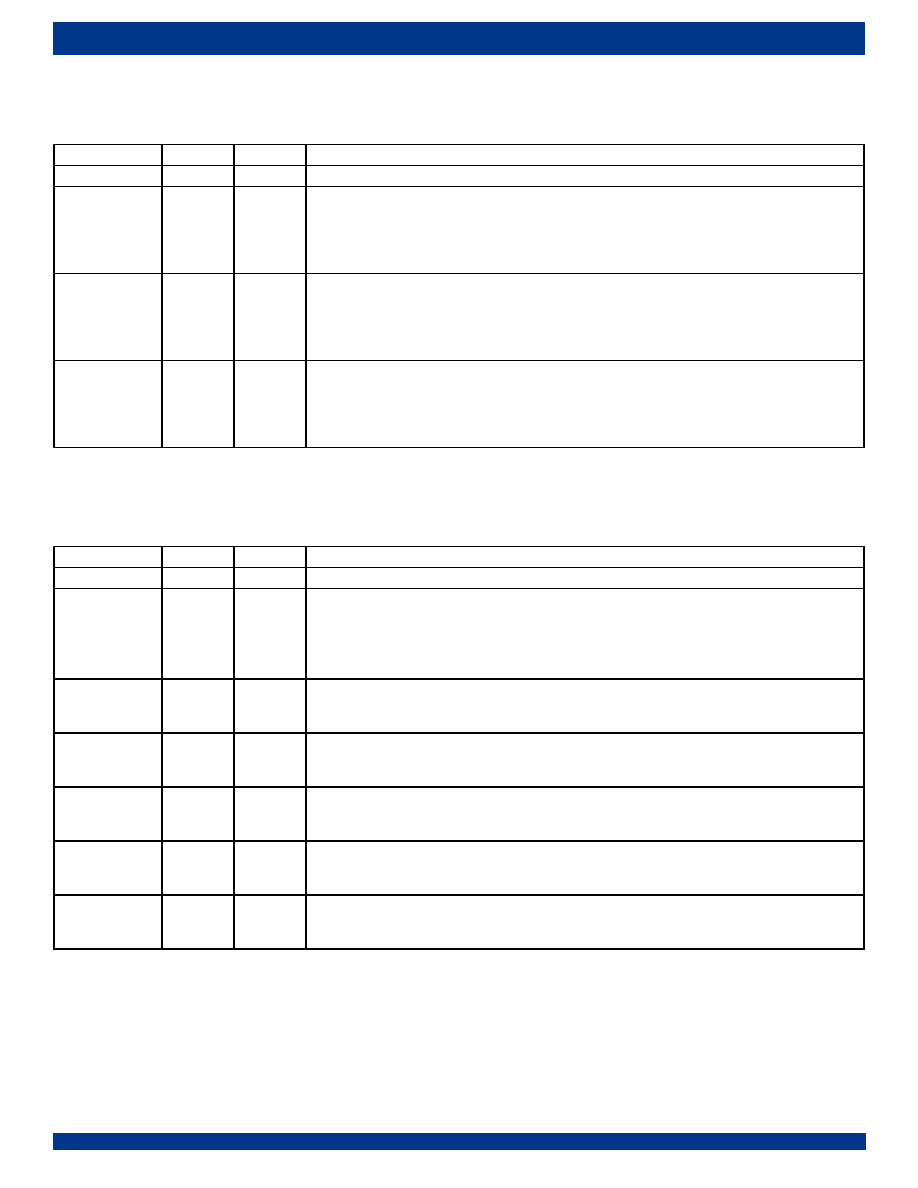

Table-38 RCF2: Receiver Configuration Register 2

(R/W, Address =09H,49H,89H,C9H)

Symbol

Bit

Default

Description

-

7-6

00

Reserved

SLICE[1:0]

5-4

01

Receive slicer threshold

= 00: The receive slicer generates a mark if the voltage on RTIPn/RRINGn exceeds 40% of the peak amplitude.

= 01: The receive slicer generates a mark if the voltage on RTIPn/RRINGn exceeds 50% of the peak amplitude.

= 10: The receive slicer generates a mark if the voltage on RTIPn/RRINGn exceeds 60% of the peak amplitude.

= 11: The receive slicer generates a mark if the voltage on RTIPn/RRINGn exceeds 70% of the peak amplitude.

UPDW[1:0]

3-2

10

Equalizer observation window

= 00: 32 bits

= 01: 64 bits

= 10: 128 bits

= 11: 256 bits

MG[1:0]

1-0

00

Monitor gain setting: these bits select the internal linear gain boost

= 00: 0 dB

= 01: 22 dB

= 10: 26 dB

= 11: 32 dB

Table-39 MAINT0: Maintenance Function Control Register 0

(R/W, Address = 0AH,4AH,8AH,CAH)

Symbol

Bit

Default

Description

-7

0

Reserved

PATT[1:0]

6-5

00

These bits select the internal pattern and insert it into the transmit data stream.

= 00: normal operation (PATT_CLK = 0) / insert all zeros (PATT_CLK = 1)

= 01: insert All Ones

= 10: insert PRBS (E1: 215-1) or QRSS (T1/J1: 220-1)

= 11: insert programmable Inband Loopback activate or deactivate code

PATT_CLK

4

0

Selects reference clock for transmitting internal pattern

= 0: uses TCLKn as the reference clock

= 1: uses MCLK as the reference clock

PRBS_INV

3

0

Inverts PRBS

= 0: PRBS data is not inverted

= 1: PRBS data is inverted before transmission and detection

LAC

2

0

The LOS/AIS criterion is selected as below:

= 0: G.775 (E1) / T1.231 (T1/J1)

= 1: ETSI 300233 & I.431 (E1) / I.431 (T1/J1)

AISE

1

0

AIS enable during LOS

= 0: AIS insertion on RDPn/RDNn/RCLKn is disabled during LOS

= 1: AIS insertion on RDPn/RDNn/RCLKn is enabled during LOS

ATAO

0

Automatically Transmit All Ones (enabled only when PATT[1:0] = 01)

= 0: disabled

= 1: Automatically Transmit All Ones pattern at TTIPn/TRINGn during LOS.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V2088DRG | IC LIU T1/J1/E1 8CH 208-TQFP |

| IDT82V2108BBG | IC FRAMER T1/J1/E1 8CH 144-BGA |

| IDT82V2604BBG | IC INVERSE MUX 4CH ATM 208-BGA |

| IDT82V2608BBG | IC INVERSE MUX 8CH ATM 208-BGA |

| IDT82V2616BBG | IC INVERSE MUX 16CH ATM 272-PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2084PFG8 | 功能描述:IC LINE INTERFC UNIT 4CH 128TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2088 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL CHANNEL T1/E1/J1 LONG HAUL/ SHORT HAUL LINE INTERFACE UNIT |

| IDT82V2088_08 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL CHANNEL T1/E1/J1 LONG HAUL/ SHORT HAUL LINE INTERFACE UNIT |

| IDT82V2088BB | 功能描述:IC LIU T1/J1/E1 8CH 208-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2088BBG | 功能描述:IC LINE INTERFACE UNIT 208-PBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。