- 您现在的位置:买卖IC网 > PDF目录377488 > IDT82V3001A (Integrated Device Technology, Inc.) WAN PLL WITH SINGLE REFERENCE INPUT PDF资料下载

参数资料

| 型号: | IDT82V3001A |

| 厂商: | Integrated Device Technology, Inc. |

| 英文描述: | WAN PLL WITH SINGLE REFERENCE INPUT |

| 中文描述: | 广域网锁相环单参考输入 |

| 文件页数: | 8/27页 |

| 文件大小: | 345K |

| 代理商: | IDT82V3001A |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

8

IDT82V3001A WAN PLL WITH SINGLE REFERENCE INPUT INDUSTRIAL TEMPERATURE RANGE

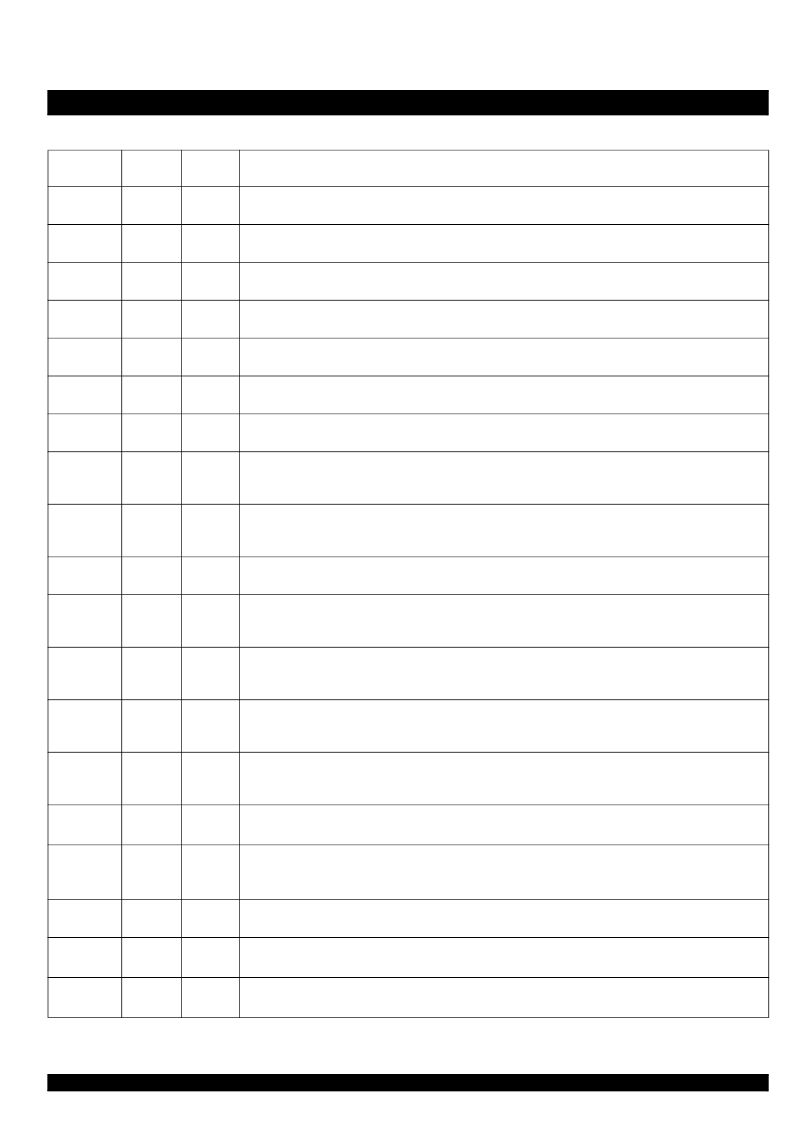

C16o

(CMOS) O

24

Clock 16.384 MHz.

This output is a 16.384 MHz clock used for ST-BUS operation.

C8o

(CMOS) O

23

Clock 8.192 MHz.

This output is an 8.192 MHz clock used for ST-BUS operation.

C4o

(CMOS) O

20

Clock 4.096 MHz.

This output is a 4.096 MHz clock used for ST-BUS operation.

C2o

(CMOS) O

17

Clock 2.048 MHz.

This output is a 2.048 MHz clock used for ST-BUS operation.

C3o

(CMOS) O

16

Clock 3.088 MHz.

This output is a 3.088 MHz clock used for T1 applications.

C1.5o

(CMOS) O

15

Clock 1.544 MHz.

This output is a 1.544 MHz clock used for T1 applications.

C6o

(CMOS) O

14

Clock 6.312 MHz.

This output is a 6.312 MHz clock used for DS2 applications.

F32o

(CMOS) O

40

Frame Pulse ST-BUS 8.192 Mb/s.

This is an 8 kHz 31 ns active low framing pulse, which marks the beginning of an ST-BUS frame. This is typically used for

ST-BUS operation at 8.192 Mb/s.

F16o

(CMOS) O

39

Frame Pulse ST-BUS 8.192 Mb/s.

This is an 8 kHz 61 ns active low framing pulse, which marks the beginning of an ST-BUS frame. This is typically used for

ST-BUS operation at 8.192 Mb/s.

F8o

(CMOS) O

36

Frame Pulse.

This is an 8 kHz 122 ns active high framing pulse, which marks the beginning of a frame.

F0o

(CMOS) O

33

Frame Pulse ST-BUS 2.048 Mb/s.

This is an 8 kHz 244 ns active low framing pulse, which marks the beginning of an ST-BUS frame. This is typically used

for ST-BUS operation at 2.048 Mb/s and 4.096 Mb/s.

RSP

(CMOS) O

41

Receive Sync Pulse.

This is an 8 kHz 488 ns active high framing pulse, which marks the beginning of an ST-BUS frame. This is typically used

to connect to Siemens MUNICH-32 device.

TSP

(CMOS) O

42

Transmit Sync Pulse.

This is an 8 kHz 488 ns active high framing pulse, which marks the beginning of an ST-BUS frame. This is typically used

to connect to Siemens MUNICH-32 device.

TDO

(CMOS) O

29

Test Serial Data Out.

JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state if JTAG scan is

not enabled.

TDI

I

32

Test Serial Data In.

JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to V

DD

.

TRST

I

30

Test Reset.

Asynchronously initializes the JTAG TAP controller by putting it in Test-Logic-Reset state. This pin is internally pulled up

to V

DD

. It is connected to the ground for normal applications.

TCK

I

28

Test Clock.

Provides a clock to JTAG test logic.

TMS

I

31

Test Mode Select.

JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to V

DD

.

IC0, IC1, IC2

-

53, 54, 55Internal Connection.

SS

when in normal operation.

Table - 1 Pin Description (Continued)

Name

Type

Pin

Number

Description

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V3001APV | WAN PLL WITH SINGLE REFERENCE INPUT |

| IDT82V3002A | WAN PLL WITH DUAL REFERENCE INPUTS |

| IDT82V3002APV | WAN PLL WITH DUAL REFERENCE INPUTS |

| IDT82V3010 | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

| IDT82V3010PV | T1/E1/OC3 TELECOM CLOCK GENERATOR WITH DUAL REFERENCE INPUTS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V3001A_08 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL WITH SINGLE REFERENCE INPUT |

| IDT82V3001APV | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL WITH SINGLE REFERENCE INPUT |

| IDT82V3001APVG | 功能描述:IC PLL WAN W/SGL REF INP 56SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| IDT82V3001APVG8 | 功能描述:IC PLL WAN W/SGL REF INP 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3002A | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL WITH DUAL REFERENCE INPUTS |

发布紧急采购,3分钟左右您将得到回复。