- 您现在的位置:买卖IC网 > PDF目录377488 > IDTCSPT857C (Integrated Device Technology, Inc.) 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER PDF资料下载

参数资料

| 型号: | IDTCSPT857C |

| 厂商: | Integrated Device Technology, Inc. |

| 英文描述: | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| 中文描述: | 为2.5V - 2.6V的锁相环微分1:10 SDRAM的时钟驱动器 |

| 文件页数: | 7/15页 |

| 文件大小: | 148K |

| 代理商: | IDTCSPT857C |

7

IDTCSPT857C

2.5V - 2.6V PLL DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

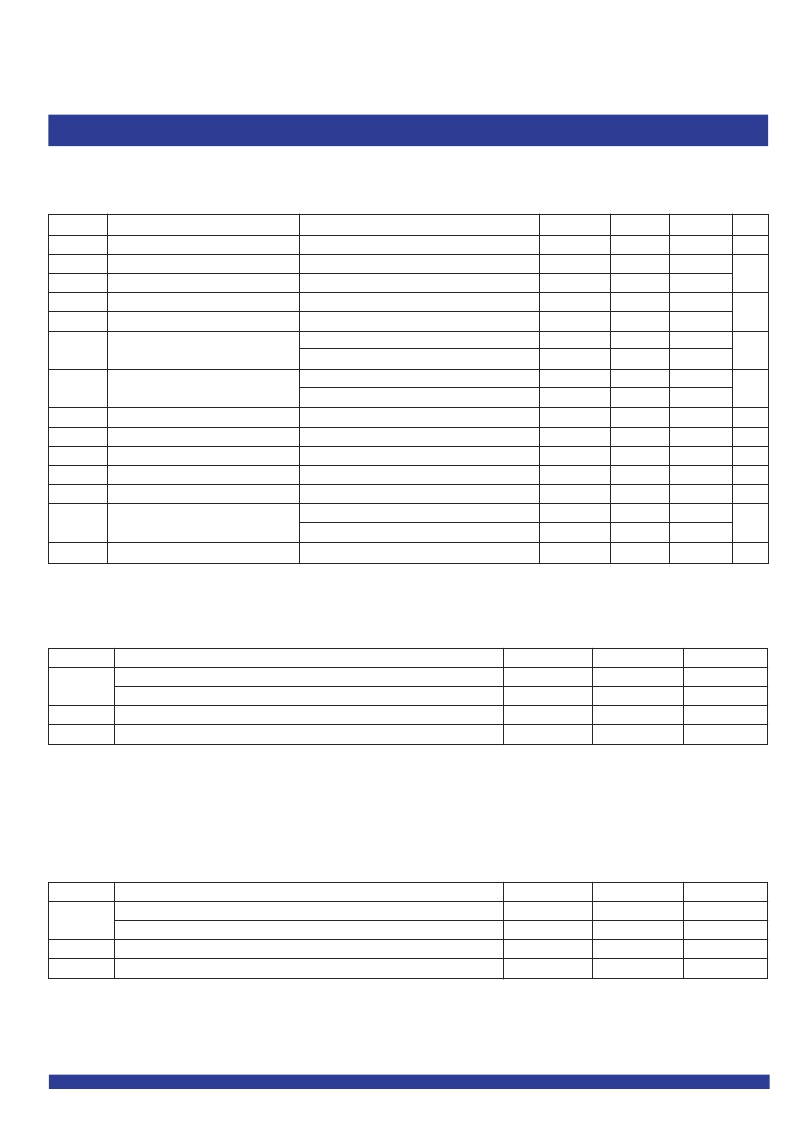

DC ELECTRICAL CHARACTERISTICS OV ER OPERATING RANGE FOR PC3200

Following Conditions Apply Unless Otherwise Specified:

Commercial: T

A

= 0°C to +70°C; Industrial: T

A

= -40°C to +85°C

Symbol

Parameter

Conditions

V

IK

Input Clamp Voltage (All Inputs)

V

DDQ

= 2.5V, I

I

= -18mA

V

IL (dc)

Static Input LOW Voltage

PWRDWN

V

IH (dc)

Static Input HIGH Voltage

PWRDWN

V

IL (ac)

Dynamc Input LOW Voltage

CLK,

CLK

, FBIN,

FBIN

V

IH (ac)

Dynamc Input HIGH Voltage

CLK,

CLK

, FBIN,

FBIN

V

OL

Output LOW Voltage

A

VDD

/V

DDQ

= Mn., I

OL

= 100

μ

A

A

VDD

/V

DDQ

= Mn., I

OL

= 12mA

V

OH

Output HIGH Voltage

A

VDD

/V

DDQ

= Mn., I

OH

= -100

μ

A

A

VDD

/V

DDQ

= Mn., I

OH

= -12mA

V

IX

Input Differential Cross Voltage

V

ID(DC) (1)

DC Input Differential Voltage

V

ID(AC) (1)

AC Input Differential Voltage

I

IN

Input Current

V

DDQ

= 2.7V, V

I

= 0V to 2.7V

I

DDPD

Power-Down Current on V

DDQ

and A

VDD

A

VDD

/V

DDQ

= Max., CLK = 0MHz or

PWRDWN

= L

I

DDQ

Dynamc Power Supply Current on V

DDQ

A

VDD

/V

DDQ

= Max., CLK = 200MHz, 120

/14pF

A

VDD

/V

DDQ

= Max., CLK = 200MHz, 120

/14pF

I

ADD

Dynamc Power Supply Current on A

VDD

A

VDD

/V

DDQ

= Max., CLK = 200MHz

Min.

– 0.3

1.7

1.7

Typ.

Max.

– 1.2

0.7

Unit

V

V

V

DDQ

+ 0.3

0.7

V

DDQ

0.1

0.6

V

V

V

DDQ

– 0.1

1.7

V

DDQ

/2 – 0.2

0.36

0.7

V

V

DDQ

/2 + 0.2

V

DDQ

+ 0.6

V

DDQ

+ 0.6

±10

200

360

300

12

V

V

V

μ

A

μ

A

mA

100

320

250

mA

NOTE:

1. V

ID

is the magnitude of the difference between the input level on CLK and the input level on

CLK

.

TIMING REQUIREMENTS FOR PC3200

Symbol

Parameter

f

CLK

Operating Clock Frequency

(1,2)

Application Clock Frequency

(1,3)

t

DC

Input Clock Duty Cycle

t

L

Stabilization Time

(4)

Min.

60

60

40

Max.

220

220

60

100

Unit

MHz

MHz

%

μ

s

NOTES:

1.

2.

3.

4.

The PLL will track a spread spectrumclock input.

Operating clock frequency is the range over which the PLL will lock, but may not meet all timng specifications.

Application clock frequency is the range over which timng specifications apply.

Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up.

T IMING REQUIREMENT S FOR PC1600 - PC2700

Symbol

Parameter

f

CLK

Operating Clock Frequency

(1,2)

Application Clock Frequency

(1,3)

t

DC

Input Clock Duty Cycle

t

L

Stabilization Time

(4)

Min.

60

60

40

Max.

200

200

60

100

Unit

MHz

MHz

%

μ

s

NOTES:

1.

2.

3.

4.

The PLL will track a spread spectrumclock input.

Operating clock frequency is the range over which the PLL will lock, but may not meet all timng specifications.

Application clock frequency is the range over which timng specifications apply.

Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up.

相关PDF资料 |

PDF描述 |

|---|---|

| IDTCSPT857CBV | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CBVI | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CNLG | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CNLGI | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CNLI | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDTCSPT857CBV | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CBVG | 功能描述:IC PLL CLK DVR SDRAM 56-VFBGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| IDTCSPT857CBVG8 | 功能描述:IC PLL CLK DVR SDRAM 56-VFBGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| IDTCSPT857CBVI | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

| IDTCSPT857CNL | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

发布紧急采购,3分钟左右您将得到回复。