- 您现在的位置:买卖IC网 > PDF目录67720 > IMISC670DYB PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | IMISC670DYB |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 文件页数: | 7/12页 |

| 文件大小: | 505K |

| 代理商: | IMISC670DYB |

SC670

I

2C Clock Generator for Pentium Notebook Designs.

Approved Product

INTERNATIONAL MICROCIRCUITS, INC. 525 LOS COCHES ST.

Rev.1.4

6/20/97

MILPITAS, CA 95035. TEL: 408-263-6300. FAX 408-263-6571

Page 4 of 12

2-WIRE I

2C CONTROL INTERFACE

The 2-wire control interface implements a write only slave interface. The IMISC670 cannot be read back. Sub-

addressing is not supported, thus all preceding bytes must be sent in order to change one of the control bytes. The 2-

wire control interface allows each clock output to be individually enabled or disabled. It also allows 24/48 MHZ frequency

selection and test mode enable.

During normal data transfer, the SDATA signal only changes when the SDCLK signal is low, and is stable when

SDCLK is high. There are two exceptions to this. A high to low transition on SDATA while SDCLK is high is used to

indicate the start of a data transfer cycle. A low to high transition on SDATA while SDCLK is high indicates the end of a

data transfer cycle. Data is always sent as complete 8-bit bytes, after which an acknowledge is generated. The first

byte of a transfer cycle is a 7-bit address with a Read/Write bit as the LSB. Data is transferred MSB first.

The IMISC670 will respond to writes to 10 bytes (max) of data to address D2 by generating the acknowledge

(low) signal on the SDATA wire following reception of each byte.

The IMISC670 will not respond to any other control

interface conditions. The I

2C interface is disabled when the PWR_DWN# pin is low. Previously set control registers are

retained.

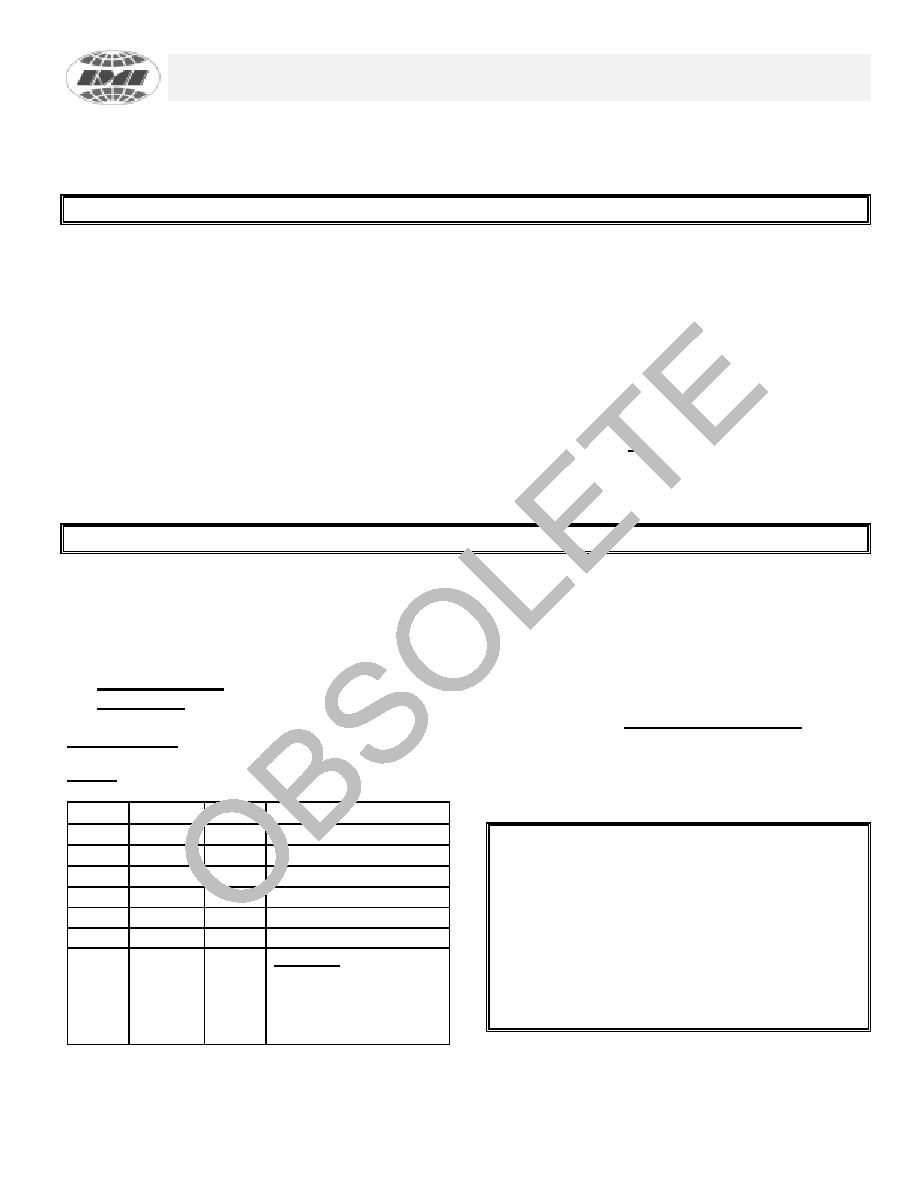

SERIAL CONTROL REGISTERS

NOTE: The Pin# column lists the affected pin number where applicable. The @Pup column gives the state

at true power up. Bytes are set to the values shown only on true power up, and not when the PWR_DWN#

pin is activated.

Following the acknowledge of the Address Byte (D2), two additional bytes must be sent:

1) “Command Code “ byte, and

2) “Byte Count” byte.

Although the data (bits) in these two bytes are considered “don’t care”, they must be sent and will be

acknowledged.

Byte 0: Function Select Register (1 = enable, 0 = Stopped)

Bit

@Pup

Pin#

Description

70

*

Reserved, Don’t set

60

*

Reserved, Don’t set

50

*

Reserved, Don’t set

40

*

Reserved, Don’t set

3

1

23

48/24 Mhz

2

1

22

48/24 Mhz

1

0

Bit1 Bit0

1

1 Tri-State

1

0 Reserved

0

1 Test Mode

0

Normal

IMPORTANT NOTE

Reserved bits are intended for possible

future functions. It is important that they

be left at their Power Up logic levels at all

times. Otherwise data sheet specifications

cannot be guaranteed.

相关PDF资料 |

PDF描述 |

|---|---|

| IMISG522BXB | OTHER CLOCK GENERATOR, PDSO16 |

| IMISG522BX | 120 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| IMISG524BX | 120 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| IMISG570CYB | PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| IMISG570CYB | PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IMISC671CTB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| IMISC671CYB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| IMISC671DYB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| IMISC674BYB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CPU System Clock Generator |

| IMISC675AYB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Miscellaneous Clock Generator |

发布紧急采购,3分钟左右您将得到回复。