- 您现在的位置:买卖IC网 > PDF目录378631 > IN74LS161 (INTEGRAL JOINT STOCK COMPANY) Octal Bus Transceivers And Registers With 3-State Outputs 24-TSSOP -40 to 85 PDF资料下载

参数资料

| 型号: | IN74LS161 |

| 厂商: | INTEGRAL JOINT STOCK COMPANY |

| 英文描述: | Octal Bus Transceivers And Registers With 3-State Outputs 24-TSSOP -40 to 85 |

| 中文描述: | 同步4位计数器,二进制,直接复位 |

| 文件页数: | 1/6页 |

| 文件大小: | 341K |

| 代理商: | IN74LS161 |

TECHNICAL DATA

Synchronous 4 Bit Counters; Binary,

Direct Reset

IN74LS161

This synchronous, presettable counter features an internal carry look-

ahead for application in high-speed counting designs. Synchronous

operation is provided by having all flip-flops clocked simultaneously so

that the outputs change conicident with each other when so instructed by

the count-enable inputs and internal gating.

This mode of operation eliminates the output counting spikes that are

normally associated with asynchronous (ripple clock) counters. A buffered

clock input triggers the four flip-flops on the rising (positive-going) edge

of the clock input wave form.

This counter is fully programmable; that is the outputs may be preset

to either level. As presetting is synchronous setting up a low level at the

load input disables the counter and causes the outputs to agree with the

setup data after the next clock pulse regardless of the levels of the enable

inputs.

The carry look-ahead circuitry provides for cascading counters for n-

bit synchronous applications without additional gating. Instrumental in

accomplishiing this function are two counter-enable inputs and a ripple

carry output. Both countenable inputs (ENABLE P and ENABLE T)

must be high to count, and ENABLE T is fed forward to enable the

ripple carry output. The ripple carry output thus enabled will produce a

high-level output pulse with a duration approximately equal to the high

level portion of the Q

A

output. The high-level overflow ripple carry

pulse can be enable successive cascaded stages. Transitions at the

ENPor ENT are allowed regardless of the level of the clock input.

Internal Look-Ahead for Fast Counting

Carry Output for n-Bit Cascading

Synchronous Counting

Synchronously Programmable

Load Control Line

Diode-Clamped Inputs

ORDERING INFORMATION

IN74LS161N Plastic

IN74LS161D SOIC

T

A

= 0

°

to 70

°

C for all packages

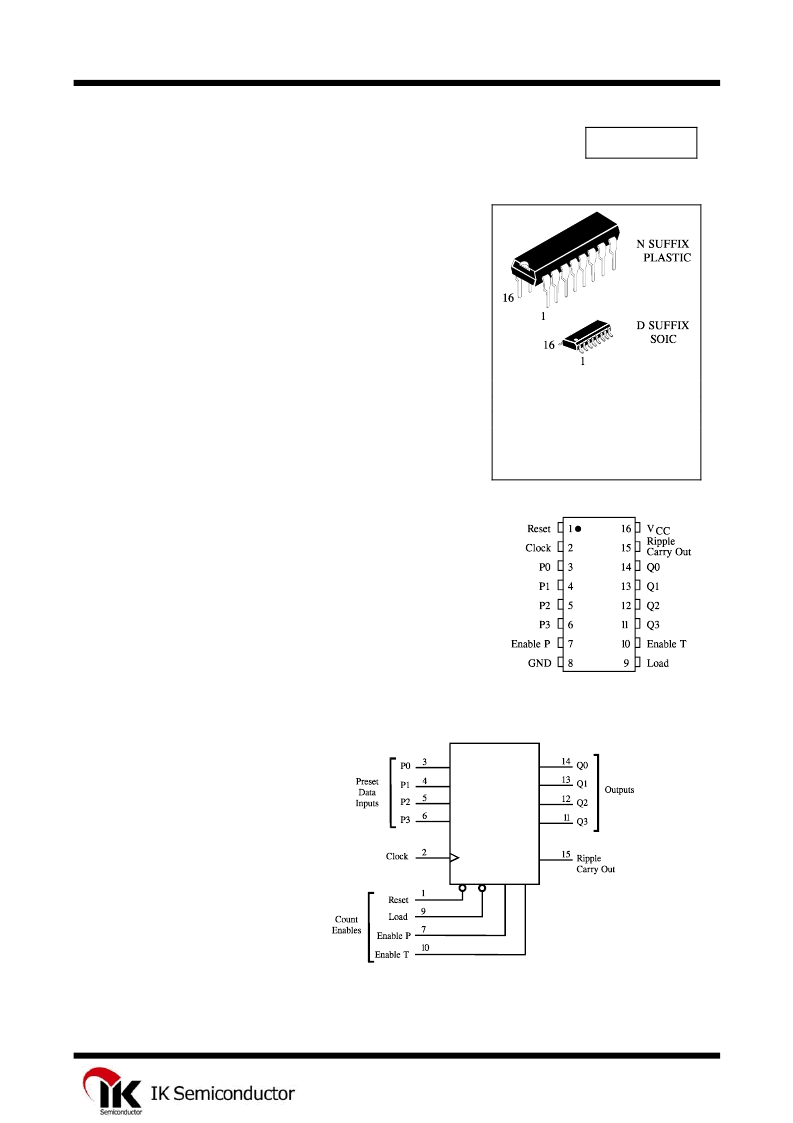

PIN ASSIGNMENT

LOGIC DIAGRAM

PIN 16 =V

CC

PIN 8 = GND

1

相关PDF资料 |

PDF描述 |

|---|---|

| IN74LS161D | Octal Bus Transceivers And Registers With 3-State Outputs 24-TSSOP -40 to 85 |

| IN74LS161N | Synchronous 4 Bit Counters; Binary, Direct Reset |

| IN74LS164 | 8-Bit Serial-Input/Parallel-Outpout Shift Register |

| IN74LS164D | Octal Bus Transceivers And Registers With 3-State Outputs 24-SSOP -40 to 85 |

| IN74LS164N | Octal Bus Transceivers And Registers With 3-State Outputs 24-SSOP -40 to 85 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IN750A-1JANTX | 制造商:ERJ 功能描述: |

| IN750A1JANTXV | 制造商: 功能描述: |

| IN751A | 制造商: 功能描述: 制造商:undefined 功能描述: |

| IN75232 | 制造商:INTEGRAL 制造商全称:INTEGRAL 功能描述:EIA-232-D INTERFACE 1 CHIP IC |

| IN753ARL | 制造商:n/a 功能描述:SAMPLE |

发布紧急采购,3分钟左右您将得到回复。