- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C54 (HARRIS SEMICONDUCTOR) CMOS Programmable Interval Timer PDF资料下载

参数资料

| 型号: | IP82C54 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | XO, clock |

| 英文描述: | CMOS Programmable Interval Timer |

| 中文描述: | 3 TIMER(S), PROGRAMMABLE TIMER, PDIP24 |

| 文件页数: | 11/17页 |

| 文件大小: | 142K |

| 代理商: | IP82C54 |

4-11

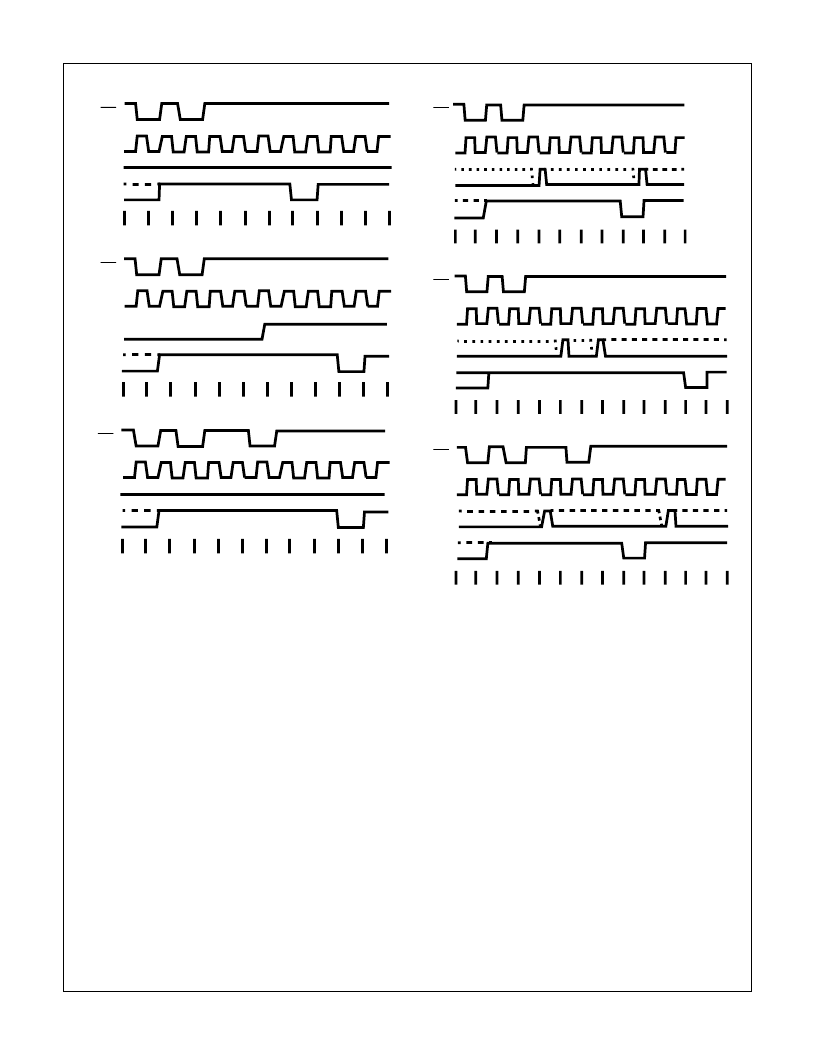

FIGURE 13. MODE 4

Mode 5: Hardware Triggered Strobe (Retriggerable)

OUT will initially be high. Counting is triggered by a rising

edge of GATE. When the initial count has expired, OUT will

go low for one CLK pulse and then go high again.

After writing the Control Word and initial count, the counter

will not be loaded until the CLK pulse after a trigger. This

CLK pulse does not decrement the count, so for an initial

count of N, OUT does not strobe low until N + 1 CLK pulses

after trigger.

A trigger results in the Counter being loaded with the initial

count on the next CLK pulse. The counting sequence is trig-

gerable. OUT will not strobe low for N + 1 CLK pulses after

any trigger GATE has no effect on OUT.

If a new count is written during counting, the current count-

ing sequence will not be affected. If a trigger occurs after the

new count is written but before the current count expires, the

Counter will be loaded with new count on the next CLK pulse

and counting will continue from there.

FIGURE 14. MODE 5

Operation Common to All Modes

Programming

When a Control Word is written to a Counter, all Control

Logic, is immediately reset and OUT goes to a known initial

state; no CLK pulses are required for this.

Gate

The GATE input is always sampled on the rising edge of

CLK. In Modes 0, 2, 3 and 4 the GATE input is level sensi-

tive, and logic level is sampled on the rising edge of CLK. In

modes 1, 2, 3 and 5 the GATE input is rising-edge sensitive.

In these Modes, a rising edge of Gate (trigger) sets an edge-

sensitive flip-flop in the Counter. This flip-flop is then sam-

pled on the next rising edge of CLK. The flip-flop is reset

immediately after it is sampled. In this way, a trigger will be

detected no matter when it occurs - a high logic level does

not have to be maintained until the next rising edge of CLK.

Note that in Modes 2 and 3, the GATE input is both edge-

and level-sensitive.

N

N

N

N

0

2

0

1

0

0

FF

FF

FF

FE

FF

FD

0

3

WR

CLK

GATE

OUT

CW = 18

LSB = 3

WR

CLK

GATE

OUT

WR

CLK

GATE

OUT

CW = 18

LSB = 3

CW = 18

LSB = 3

N

N

N

0

3

0

2

0

1

0

2

0

1

0

0

FF

FF

N

N

N

N

0

3

0

3

0

2

0

1

0

0

FF

FF

0

3

LSB = 2

N

N

N

N

N

0

3

0

2

0

1

0

0

FF

FF

0

3

WR

CLK

GATE

OUT

CW = 1A LSB = 3

N

N

N

N

0

3

0

2

0

3

0

2

0

1

N

N

N

N

0

3

0

2

0

1

0

0

FF

FF

FF

FE

WR

CLK

GATE

OUT

CW = 1A LSB = 3

WR

CLK

GATE

OUT

CW = 1A LSB = 3

N

N

N

0

0

FF

FF

LSB = 5

N

0

5

0

4

82C54

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C54-10 | CMOS Programmable Interval Timer |

| IP82C59A | CMOS Priority Interrupt Controller |

| IP82C59A-5 | CMOS Priority Interrupt Controller |

| IP82C59A-12 | CMOS Priority Interrupt Controller |

| IP82C83H | CMOS Octal Latching Inverting Bus Driver |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C54/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog Timer Circuit |

| IP82C54-10 | 功能描述:计时器和支持产品 PERIPH PRG-CNTR 5V 10MHZ 24PDIP IND RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| IP82C54-10S5001 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C54-10Z | 功能描述:计时器和支持产品 W/ANNEAL PERIPH PRG- CNTR 5V 10MHZ 24PDIP RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| IP82C54-12 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Programmable Interval Timer |

发布紧急采购,3分钟左右您将得到回复。