- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C59A-5 (INTERSIL CORP) CMOS Priority Interrupt Controller PDF资料下载

参数资料

| 型号: | IP82C59A-5 |

| 厂商: | INTERSIL CORP |

| 元件分类: | 中断控制器 |

| 英文描述: | CMOS Priority Interrupt Controller |

| 中文描述: | 80C86; 80C88; 80C286; 8080; 8085; 8086; 8088; 80286; NSC800 COMPATIBLE, INTERRUPT CONTROLLER, PDIP28 |

| 封装: | PLASTIC, DIP-28 |

| 文件页数: | 6/20页 |

| 文件大小: | 152K |

| 代理商: | IP82C59A-5 |

4-6

6. This completes the interrupt cycle. In the AEOI mode, the

ISR bit is reset at the end of the second INTA pulse. Oth-

erwise, the ISR bit remains set until an appropriate EOI

command is issued at the end of the interrupt subroutine.

If no interrupt request is present at step 4 of either sequence

(i.e., the request was too short in duration), the 82C59A will

issue an interrupt level 7. If a slave is programmed on IR bit

7, the CAS lines remain inactive and vector addresses are

output from the master 82C59A.

Interrupt Sequence Outputs

8080, 8085 Interrupt Response Mode

This sequence is timed by three INTA pulses. During the first

lNTA pulse, the CALL opcode is enabled onto the data bus.

First Interrupt Vector Byte Data: Hex CD

During the second INTA pulse, the lower address of the

appropriate service routine is enabled onto the data bus.

When interval = 4 bits, A5 - A7 are programmed, while

A0 - A4 are automatically inserted by the 82C59A. When

interval = 8, only A6 and A7 are programmed, while A0 - A5

are automatically inserted.

During the third INTA pulse, the higher address of the appro-

priate service routine, which was programmed as byte 2 of the

initialization sequence (A8 - A15), is enabled onto the bus.

D7

D6

D5

D4

D3

D2

D1

D0

Call Code

1

1

0

0

1

1

0

1

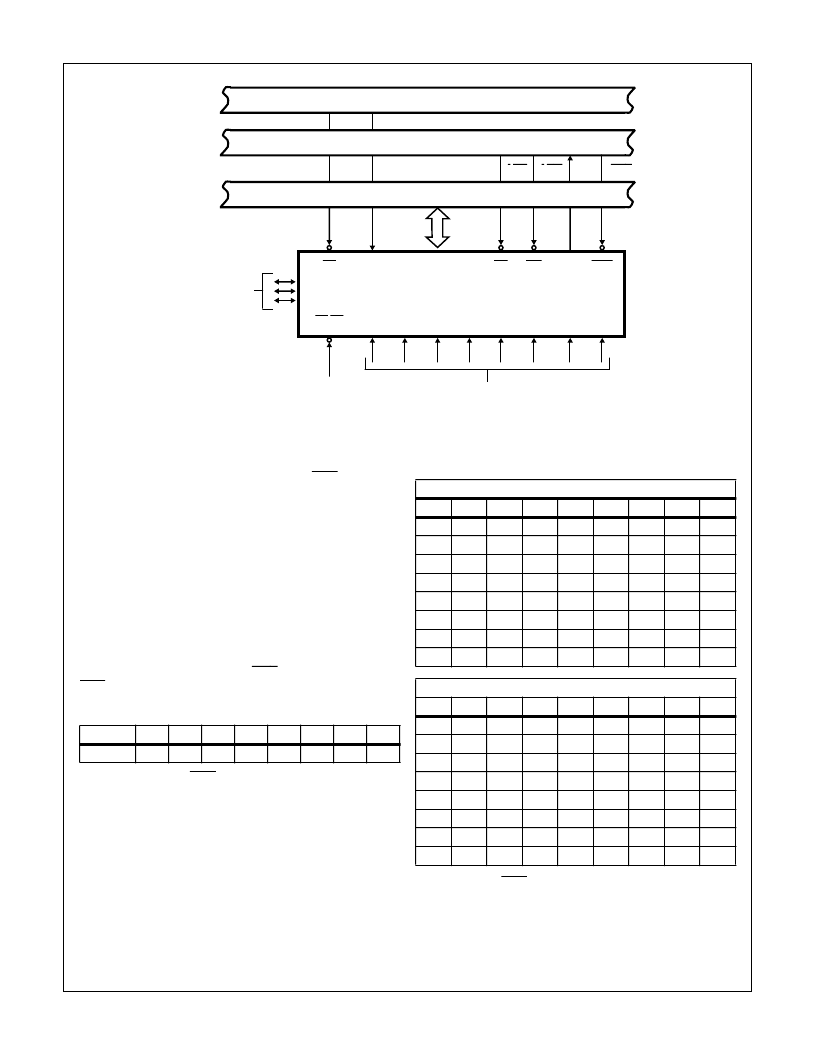

ADDRESS BUS (16)

CONTROL BUS

DATA BUS (8)

I/OR

I/OW

INT

INTA

CASCADE

LINES

CAS 0

CAS 1

CAS 2

SP/EN

CS

RD

WR

INTA

INT

D

7

- D

0

A

0

SLAVE PROGRAM/

ENABLE BUFFER

INTERRUPT

REQUESTS

82C59A

IRQ

5

IRQ

7

IRQ

6

IRQ

4

IRQ

3

IRQ

2

IRQ

1

IRQ

0

FIGURE 5. 82C59A STANDARD SYSTEM BUS INTERFACE

CONTENT OF SECOND INTERRUPT VECTOR BYTE

IR

INTERVAL = 4

D7

D6

D5

D4

D3

D2

D1

D0

7

A7

A6

A5

1

1

1

0

0

6

A7

A6

A5

1

1

0

0

0

5

A7

A6

A5

1

0

1

0

0

4

A7

A6

A5

1

0

0

0

0

3

A7

A6

A5

0

1

1

0

0

2

A7

A6

A5

0

1

0

0

0

1

A7

A6

A5

0

0

1

0

0

0

A7

A6

A5

0

0

0

0

0

IR

INTERVAL = 8

D7

D6

DS

D4

D3

D2

D1

D0

7

A7

A6

1

1

1

0

0

0

6

A7

A6

1

1

0

0

0

0

5

A7

A6

1

0

1

0

0

0

4

A7

A6

1

0

0

0

0

0

3

A7

A6

0

1

1

0

0

0

2

A7

A6

0

1

0

0

0

0

1

A7

A6

0

0

1

0

0

0

0

A7

A6

0

0

0

0

0

0

82C59A

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C59A-12 | CMOS Priority Interrupt Controller |

| IP82C83H | CMOS Octal Latching Inverting Bus Driver |

| IP82C84A | CMOS Clock Generator Driver |

| IP82C86H | CMOS Octal Bus Transceiver |

| IP82C86H-5 | CMOS Octal Bus Transceiver |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C59AS2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| IP82C82 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C82/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Non-Inverting Buffer/Driver |

| IP82C83H | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Octal Latching Inverting Bus Driver |

| IP82C84A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Clock Generator Driver |

发布紧急采购,3分钟左右您将得到回复。