- 您现在的位置:买卖IC网 > PDF目录11567 > IS82C59AX96 (Intersil)IC CTRLR INTERRUPT 8MHZ 28-PLCC PDF资料下载

参数资料

| 型号: | IS82C59AX96 |

| 厂商: | Intersil |

| 文件页数: | 7/22页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR INTERRUPT 8MHZ 28-PLCC |

| 标准包装: | 750 |

| 控制器类型: | CMOS 优先中断控制器 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 1mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC(11.51x11.51) |

| 包装: | 带卷 (TR) |

15

FN2784.5

March 17, 2006

Reading the 82C59A Status

The input status of several internal registers can be read to

update the user information on the system. The following

registers can be read via OCW3 (lRR and ISR) or OCW1

(lMR).

Interrupt Request Register (IRR): 8-bit register which

contains the levels requesting an interrupt to be

acknowledged. The highest request level is reset from the

lRR when an interrupt is acknowledged. lRR is not affected

by lMR.

In-Service Register (ISR): 8-bit register which contains the

priority levels that are being serviced. The ISR is updated

when an End of Interrupt Command is issued.

Interrupt Mask Register: 8-bit register which contains the

interrupt request lines which are masked.

The lRR can be read when, prior to the RD pulse, a Read

Register Command is issued with OCW3 (RR = 1, RIS = 0).

The ISR can be read when, prior to the RD pulse, a Read

Register Command is issued with OCW3 (RR = 1, RIS = 1).

There is no need to write an OCW3 before every status read

operation, as long as the status read corresponds with the

previous one: i.e., the 82C59A “remembers” whether the lRR

or ISR has been previously selected by the OCW3. This is

not true when poll is used. In the poll mode, the 82C59A

treats the RD following a “poll write” operation as an INTA.

After initialization, the 82C59A is set to lRR.

For reading the lMR, no OCW3 is needed. The output data bus

will contain the lMR whenever RD is active and A0 = 1 (OCW1).

Polling overrides status read when P = 1, RR = 1 in OCW3.

Edge and Level Triggered Modes

This mode is programmed using bit 3 in lCW1.

If LTlM = “0”, an interrupt request will be recognized by a low to

high transition on an IR input. The IR input can remain high

without generating another interrupt.

If LTIM = “1”, an interrupt request will be recognized by a “high”

level on an IR input, and there is no need for an edge detection.

The interrupt request must be removed before the EOI

command is issued or the CPU interrupt is enabled to prevent a

second interrupt from occurring.

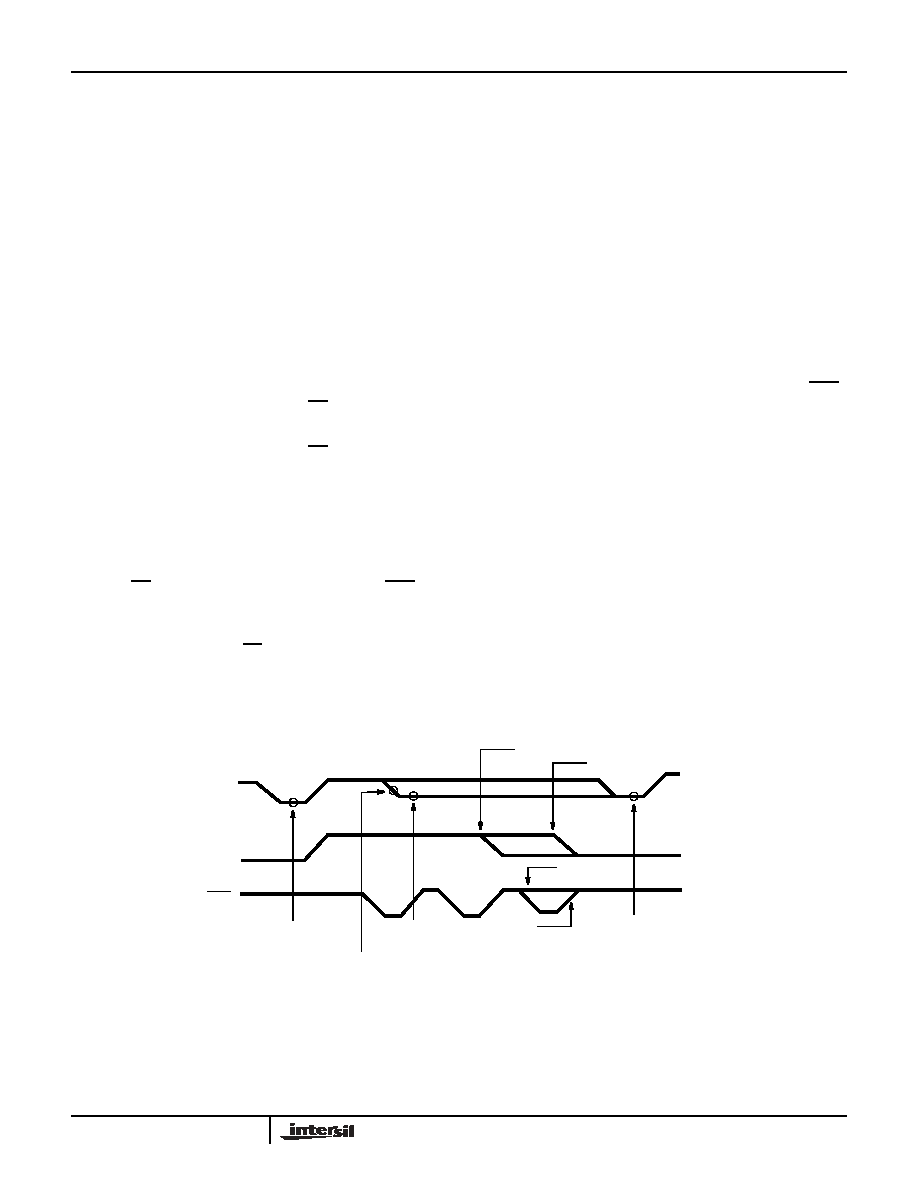

The priority cell diagram shows a conceptual circuit of the level

sensitive and edge sensitive input circuitry of the 82C59A. Be

sure to note that the request latch is a transparent D type latch.

In both the edge and level triggered modes the IR inputs

must remain high until after the falling edge of the first INTA.

If the IR input goes low before this time a DEFAULT lR7 will

occur when the CPU acknowledges the interrupt. This can

be a useful safeguard for detecting interrupts caused by

spurious noise glitches on the IR inputs. To implement this

feature the lR7 routine is used for “clean up” simply

executing a return instruction, thus, ignoring the interrupt. If

lR7 is needed for other purposes a default lR7 can still be

detected by reading the ISR. A normal lR7 interrupt will set

the corresponding ISR bit, a default IR7 won’t. If a default

IR7 routine occurs during a normal lR7 routine, however, the

ISR will remain set. In this case it is necessary to keep track

of whether or not the IR7 routine was previously entered. If

another lR7 occurs it is a default.

In power sensitive applications, it is advisable to place the

82C59A in the edge-triggered mode with the IR lines

normally high. This will minimize the current through the

internal pull-up resistors on the IR pins.

LATCH

ARM

(NOTE 1)

EARLIEST IR

CAN BE

REMOVED

LATCH

ARM

(NOTE 1)

8080/85

LATCH

ARM

(NOTE 1)

80C86/88/286

8080/85

IR

INT

INTA

NOTE:

1. Edge triggered mode only.

FIGURE 10. IR TRIGGERING TIMING REQUIREMENTS

82C59A

相关PDF资料 |

PDF描述 |

|---|---|

| PIC18F23K20-E/MV | IC MCU 8BIT 8KB FLASH 28UQFN |

| V375A8C400BF2 | CONVERTER MOD DC/DC 8V 400W |

| IS82C59A-12Z96 | IC CTRLR INTERRPT 12.5MHZ 28PLCC |

| IS82C59A-12Z | IC CTRLR INTERRPT 12.5MHZ 28PLCC |

| PIC16LF1936-I/SP | IC PIC MCU FLASH 512KX14 28SPDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS82C59AZ | 功能描述:接口-I/O扩展器 PERIPH INT CNTRLR 5V 8MHZ 28PLCC IND RoHS:否 制造商:NXP Semiconductors 逻辑系列: 输入/输出端数量: 最大工作频率:100 kHz 工作电源电压:1.65 V to 5.5 V 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:HVQFN-16 封装:Reel |

| IS82C59AZX96 | 功能描述:接口-I/O扩展器 PERIPH INT CNTRLR 5V 8MHZ 28PLCC IND RoHS:否 制造商:NXP Semiconductors 逻辑系列: 输入/输出端数量: 最大工作频率:100 kHz 工作电源电压:1.65 V to 5.5 V 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:HVQFN-16 封装:Reel |

| IS82C600 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRAILBLAZER High-Speed SRAM with Address Decoding and Ready Logic |

| IS82C82 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Harris Corporation 功能描述: |

| IS82C83H | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Octal Latching Inverting Bus Driver |

发布紧急采购,3分钟左右您将得到回复。