- 您现在的位置:买卖IC网 > PDF目录11567 > IS82C59AX96 (Intersil)IC CTRLR INTERRUPT 8MHZ 28-PLCC PDF资料下载

参数资料

| 型号: | IS82C59AX96 |

| 厂商: | Intersil |

| 文件页数: | 8/22页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR INTERRUPT 8MHZ 28-PLCC |

| 标准包装: | 750 |

| 控制器类型: | CMOS 优先中断控制器 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 电流 - 电源: | 1mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-LCC(J 形引线) |

| 供应商设备封装: | 28-PLCC(11.51x11.51) |

| 包装: | 带卷 (TR) |

16

FN2784.5

March 17, 2006

The Special Fully Nested Mode

This mode will be used in the case of a big system where

cascading is used, and the priority has to be conserved

within each slave. In this case the special fully nested mode

will be programmed to the master (using lCW4). This mode

is similar to the normal nested mode with the following

exceptions:

a. When an interrupt request from a certain slave is in ser-

vice, this slave is not locked out from the master’s priority

logic and further interrupt requests from higher priority

IRs within the slave will be recognized by the master and

will initiate interrupts to the processor. (In the normal

nested mode a slave is masked out when its request is in

service and no higher requests from the same slave can

be serviced.

b. When exiting the Interrupt Service routine the software

has to check whether the interrupt serviced was the only

one from that slave. This is done by sending a non-spe-

cific End of Interrupt (EOI) command to the slave and

then reading its In-Service register and checking for zero.

If it is empty, a non-specified EOI can be sent to the mas-

ter, too. If not, no EOI should be sent.

Buffered Mode

When the 82C59A is used in a large system where bus

driving buffers are required on the data bus and the

cascading mode is used, there exists the problem of

enabling buffers

The buffered mode will structure the 82C59A to send an

enable signal on SP/EN to enable the buffers. In this mode,

whenever the 82C59A’s data bus outputs are enabled, the

SP/EN output becomes active.

This modification forces the use of software programming to

determine whether the 82C59A is a master or a slave. Bit 3

in ICW4 programs the buffered mode, and bit 2 in lCW4

determines whether it is a master or a slave.

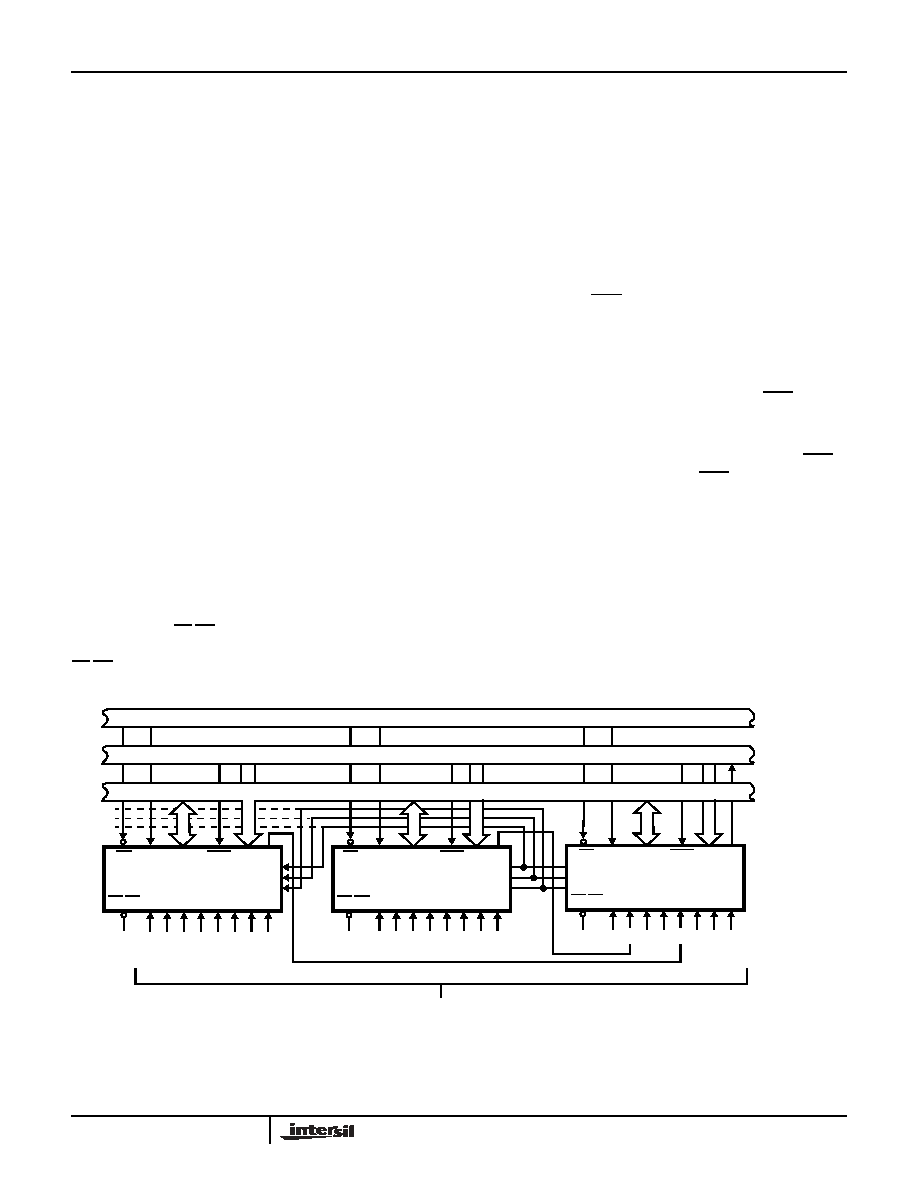

Cascade Mode

The 82C59A can be easily interconnected in a system of one

master with up to eight slaves to handle up to 64 priority

levels.

The master controls the slaves through the 3 line cascade

bus (CAS2 - 0). The cascade bus acts like chip selects to the

slaves during the INTA sequence.

In a cascade configuration, the slave interrupt outputs (INT)

are connected to the master interrupt request inputs. When a

slave request line is activated and afterwards acknowledged,

the master will enable the corresponding slave to release the

device routine address during bytes 2 and 3 of INTA. (Byte 2

only for 80C86/88/286).

The cascade bus lines are normally low and will contain the

slave address code from the leading edge of the first INTA

pulse to the trailing edge of the last INTA pulse. Each

82C59A in the system must follow a separate initialization

sequence and can be programmed to work in a different

mode. An EOI command must be issued twice: once for the

master and once for the corresponding slave. Chip select

decoding is required to activate each 82C59A.

NOTE: Auto EOI is supported in the slave mode for the 82C59A.

The cascade lines of the Master 82C59A are activated only

for slave inputs, non-slave inputs leave the cascade line

inactive (low). Therefore, it is necessary to use a slave

address of 0 (zero) only after all other addresses are used.

FIGURE 11. CASCADING THE 82C59A

CS

82C59A

SLAVE A

CAS 0

CAS 1

CAS 2

INT

A0 D7 - D0 INTA

SP

/EN 75

6

4 3 210

GND

75

6

4 3 210

CS

82C59A

SLAVE B

CAS 0

CAS 1

CAS 2

INT

A0 D7 - D0 INTA

SP

/EN 75

6

432 10

GND

75

6

432 10

CS

MASTER 82C59A

CAS 0

CAS 1

CAS 2

INT

A0 D7 - D0 INTA

SP

/EN 75

6

4 3210

VCC

75 42 1 0

3

6

INT REQ

DATA BUS (8)

CONTROL BUS

ADDRESS BUS (16)

INTERRUPT REQUESTS

82C59A

相关PDF资料 |

PDF描述 |

|---|---|

| PIC18F23K20-E/MV | IC MCU 8BIT 8KB FLASH 28UQFN |

| V375A8C400BF2 | CONVERTER MOD DC/DC 8V 400W |

| IS82C59A-12Z96 | IC CTRLR INTERRPT 12.5MHZ 28PLCC |

| IS82C59A-12Z | IC CTRLR INTERRPT 12.5MHZ 28PLCC |

| PIC16LF1936-I/SP | IC PIC MCU FLASH 512KX14 28SPDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS82C59AZ | 功能描述:接口-I/O扩展器 PERIPH INT CNTRLR 5V 8MHZ 28PLCC IND RoHS:否 制造商:NXP Semiconductors 逻辑系列: 输入/输出端数量: 最大工作频率:100 kHz 工作电源电压:1.65 V to 5.5 V 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:HVQFN-16 封装:Reel |

| IS82C59AZX96 | 功能描述:接口-I/O扩展器 PERIPH INT CNTRLR 5V 8MHZ 28PLCC IND RoHS:否 制造商:NXP Semiconductors 逻辑系列: 输入/输出端数量: 最大工作频率:100 kHz 工作电源电压:1.65 V to 5.5 V 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:HVQFN-16 封装:Reel |

| IS82C600 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRAILBLAZER High-Speed SRAM with Address Decoding and Ready Logic |

| IS82C82 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Harris Corporation 功能描述: |

| IS82C83H | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Octal Latching Inverting Bus Driver |

发布紧急采购,3分钟左右您将得到回复。