- 您现在的位置:买卖IC网 > PDF目录176103 > ISD5104X (WINBOND ELECTRONICS CORP) 240 SEC, SPEECH SYNTHESIZER WITH RCDG, UUC27 PDF资料下载

参数资料

| 型号: | ISD5104X |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | 音频合成 |

| 英文描述: | 240 SEC, SPEECH SYNTHESIZER WITH RCDG, UUC27 |

| 封装: | LEAD FREE, DIE-27 |

| 文件页数: | 70/89页 |

| 文件大小: | 600K |

| 代理商: | ISD5104X |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页当前第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

ISD5100 SERIES

- 72 -

10.5. I

2C PROTOCOL

Since the I2C protocol allows multiple devices on the bus, each device must have an address. This

address is known as a “Slave Address”. A Slave Address consists of 7 bits, followed by a single bit

that indicates the direction of data flow. This single bit is 1 for a Write cycle, which indicates the data is

being sent from the current bus master to the device being addressed. This single bit is a 0 for a Read

cycle, which indicates that the data is being sent from the device being addressed to the current bus

master. For example, the valid Slave Addresses for the ISD5100 Series device, for both Write and

Read cycles, are shown in section 7.3.1 on page 13 of this datasheet.

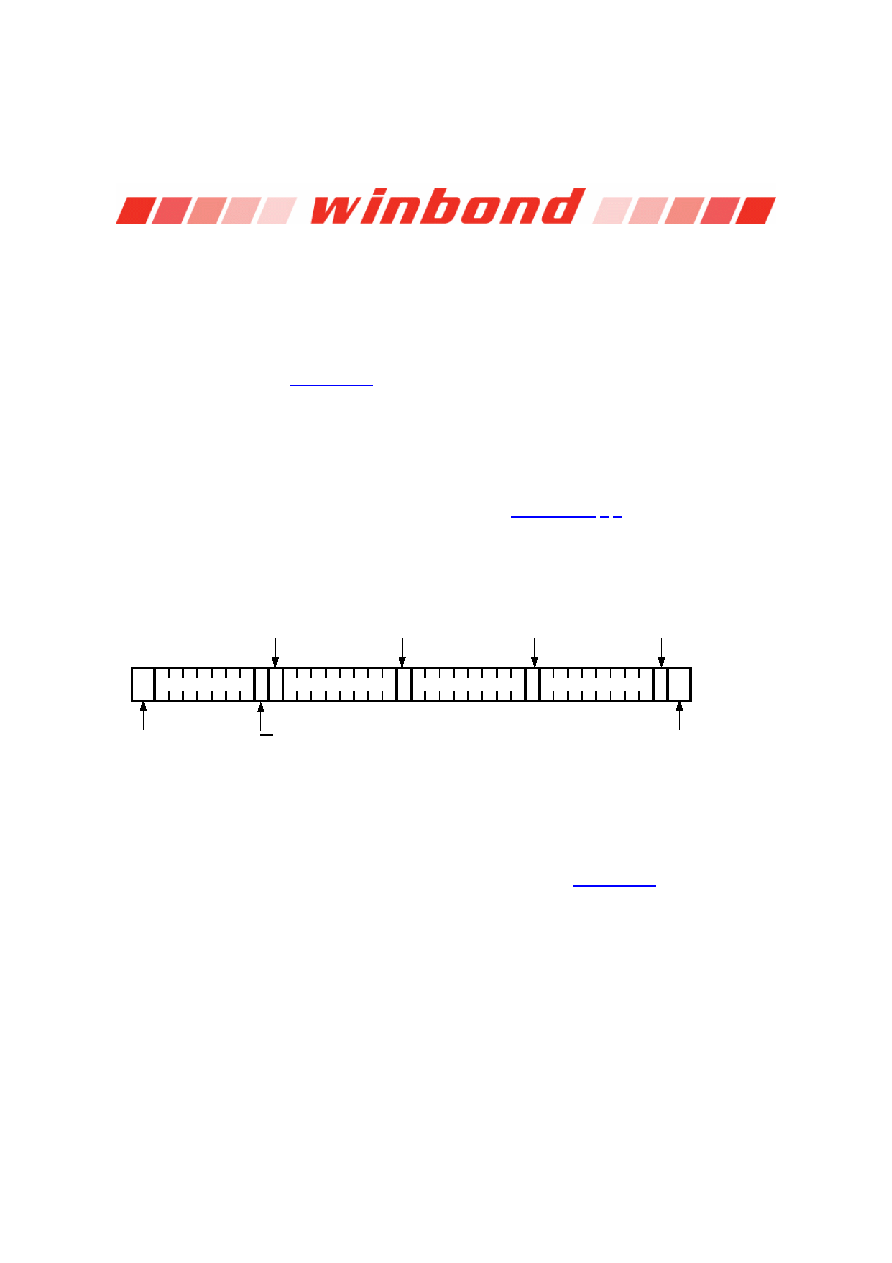

Before any data is transmitted on the I2C interface, the current bus master must address the slave it

wishes to transfer data to or from. The Slave Address is always sent out as the 1

st byte following the

Start Condition sequence. An example of a Master transmitting an address to a ISD5100 Series slave

is shown below. In this case, the Master is writing data to the slave and the R/W bit is “0”, i.e. a Write

cycle. All the bits transferred are from the Master to the Slave, except for the indicated Acknowledge

bits. The following example details the transfer explained in section 7.3.1-2-3 on pages 13-20 of this

datasheet.

Master Transmits to Slave Receiver (Write) Mode

S

W AAAA

P

SLAVE ADDRESS

COMMAND BYTE

High ADDR. BYTE

Low ADDR. BYTE

acknowledgement

from slave

acknowledgement

from slave

acknowledgement

from slave

acknowledgement

from slave

R/W

Start Bit

Stop Bit

A common procedure in the ISD5100 Series is the reading of the Status Bytes. The Read Status

condition in the ISD5100 Series is triggered when the Master addresses the chip with its proper Slave

Address, immediately followed by the R/W bit set to a “1” and without the Command Byte being sent.

This is an example of the Master sending to the Slave, immediately followed by the Slave sending

data back to the Master. The “N” not-acknowledge cycle from the Master ends the transfer of data

from the Slave. The following example details the transfer explained in section 7.3.1 on page 13 of this

datasheet.

相关PDF资料 |

PDF描述 |

|---|---|

| ISD5108EYI | 480 SEC, SPEECH SYNTHESIZER WITH RCDG, PDSO28 |

| ISD5108EY | 480 SEC, SPEECH SYNTHESIZER WITH RCDG, PDSO28 |

| ISD5108SYI | 480 SEC, SPEECH SYNTHESIZER WITH RCDG, PDSO28 |

| ISD5108SY | 480 SEC, SPEECH SYNTHESIZER WITH RCDG, PDSO28 |

| ISD5108X | 480 SEC, SPEECH SYNTHESIZER WITH RCDG, UUC27 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISD5108EY | 功能描述:IC VOICE REC/PLAY 4-8MN 28-TSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5100 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD5108EYI | 功能描述:IC VOICE REC/PLAY 4-8MN 28-TSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5100 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD5108EYIR | 功能描述:IC VOICE REC/PLAY 4-8MN 28-TSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5100 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD5108EYR | 功能描述:IC VOICE REC/PLAY 4-8MN 28-TSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5100 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD5108SY | 功能描述:IC VOICE REC/PLAY 4-8MN 28-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5100 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

发布紧急采购,3分钟左右您将得到回复。