参数资料

| 型号: | ISL12032IVZ |

| 厂商: | Intersil |

| 文件页数: | 7/26页 |

| 文件大小: | 0K |

| 描述: | IC RTC LP BATT BACK SRAM 14TSSOP |

| 产品培训模块: | Solutions for Industrial Control Applications |

| 标准包装: | 960 |

| 类型: | 时间事件记录器 |

| 特点: | 警报器,SRAM,涓流充电器 |

| 存储容量: | 128B |

| 时间格式: | HH:MM:SS:hh(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | I²C,2 线串口 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电压 - 电源,电池: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 管件 |

15

FN6618.3

May 5, 2011

Event Count (EVTCNT)

The EVTCNT register increments automatically each time an

event occurs. The register is set to 00h on initial power-up.

The maximum count is 255, and will stay at that value until

set to zero via an I2C write.

Performing a write of 00h to this register will clear the

contents of this register and all levels of the TSEVT section.

A clear to this register should be done with care. Write event

index register zero only selects first event time stamp. Write

event count EVNTCNT zero will both clear event counter

and all time stamps.

Control Registers

Addresses [0Ch to 14h]

The control registers (INT, FO, EVIC, EVIX, TRICK,

PWRVDD, PWRBAT, AC, and FTR) contain all the bits

necessary to control the parametric functions on the

ISL12032.

Interrupt Control Register (INT)

AUTOMATIC RESET BIT (ARST)

This bit enables/disables the automatic reset of the ALM0,

ALM1, LVDD, LBAT85, and LBAT75 status bits only. When

ARST bit is set to “1”, these status bits are reset to “0” after a

valid read of the SRDC Register (with a valid STOP

condition). When the ARST is cleared to “0”, the user must

manually reset the ALM0, ALM1, LVDD, LBAT85, and

LBAT75 bits.

WRITE RTC ENABLE BIT (WRTC)

The WRTC bit enables or disables write capability into the

RTC Register section. The factory default setting of this bit is

“0”. Upon initialization or power-up, the WRTC must be set

to “1” to enable the RTC. Upon the completion of a valid

write (STOP), the RTC starts counting. The RTC internal

1Hz signal is synchronized to the STOP condition during a

valid write cycle. This bit will remain set until reset to “0” or a

complete power-down occurs (VDD = VBAT = 0.0V)

ALARM INTERRUPT MODE BIT (IM)

This bit enables/disables the interrupt mode of the alarm

function. When the IM bit is set to “1”, the alarms will operate

in the interrupt mode, where an active low pulse width of

250ms will appear at the IRQ pin when the RTC is triggered

by either alarm as defined by the Alarm0 section (1Dh to

22h) or the Alarm1 section (23h to 28h). When the IM bit is

cleared to “0”, the alarm will operate in standard mode,

where the IRQ pin will be set LOW until both the

ALM0/ALM1 status bits are cleared to “0”.

ALARM 1 (ALE 1)

This bit enables the Alarm1 function. When ALE1 = “1”, a

match of the RTC section with the Alarm1 section will result

is setting the ALM1 status bit to “1” and the IRQ output LOW.

When set to “0”, the Alarm1 function is disabled.

ALARM 0 (ALE 0)

This bit enables the Alarm0 function. When ALE0 = 1, a

match of the RTC section with the Alarm1 section will result

is setting the ALM0 status bit to “1” and the IRQ output LOW.

When set to “0”, the Alarm0 function is disabled.

Frequency Out Register (FO)

FREQUENCY OUTPUT AND INTERRUPT BIT (FOBATB)

This bit enables/disables FOUT during battery backup mode

(i.e. VBAT power source active). When the FOBATB is set to

“1” the FOUT pin is disabled during battery backup mode. When

the FOBATB is cleared to “0”, the FOUT pin is enabled during

battery backup mode (default). Note that FOUT is a CMOS

output and needs no pull-up resistor. Note also that battery

current drain will be higher with FOUT enabled in battery

backup mode.

FREQUENCY OUT CONTROL BITS (FO <2:0>)

These bits enable/disable the frequency output function and

frequency selection. Note that frequencies from 4096Hz to

32768Hz are derived from the Crystal Oscillator, and the 1.0,

10, and 50/60Hz frequencies are derived from the AC clock

input. The exception to this is when the AC input qualification

has failed, and the crystal oscillator is used for the 1.0Hz

FOUT.

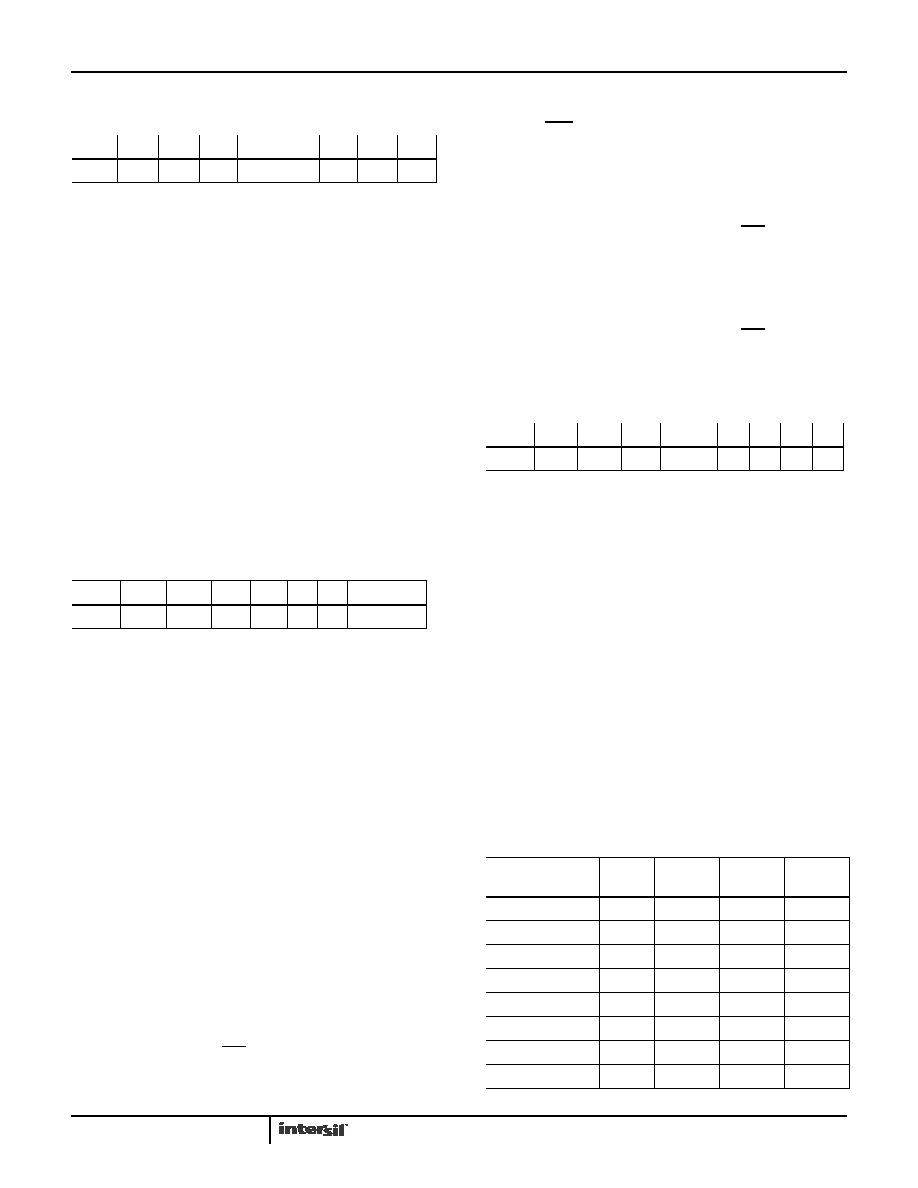

TABLE 5. EVENT COUNTER REGISTER (EVTCNT)

ADDR

7

6

5

4

3

2

1

0

0Bh

EVC7 EVC6 EVC5 EVC4 EVC3 EVC2 EVC1 EVC0

TABLE 6. INTERRUPT CONTROL REGISTER (INT)

ADDR

7

6

5

4

3

2

1

0

0Ch

ARST

WRTC

IM

X

ALE1 ALE0

TABLE 7. FREQUENCY OUT REGISTER (FO)

ADDR

7

6

5

4

3210

0Dh

X

FOBATB

X

FO2 FO1 FO0

TABLE 8. FREQUENCY SELECTION OF FOUT PIN

FREQUENCY,

FOUT

UNITS

FO2

FO1

FO0

32768

Hz

0

16372

Hz

0

1

8192

Hz

0

1

0

4096

Hz

0

1

50/60

Hz

1

0

1

Hz

101

Low

Hz

1

0

High

Hz

1

ISL12032

相关PDF资料 |

PDF描述 |

|---|---|

| ISL12057IUZ | IC RTC/CALENDAR I2C 8-MSOP |

| ISL12058IUZ | IC RTC/CALENDAR I2C-BUS 8-MSOP |

| ISL12059IBZ | IC RTC/CALENDAR I2C-BUS 8-SOIC |

| ISL12082IUZ | IC RTC I2C LO-POWER 10-MSOP |

| ISL1208IU8-TK | IC RTC/CALENDAR I2C 8-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL12032IVZ-T | 功能描述:实时时钟 REAL TIME CLK W/ EEPROM 14LD RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12057 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Cost and Low Power I2C RTC Real Time Clock/Calendar |

| ISL12057IBZ | 功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12057IBZ-T | 功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12057IRUZ-T | 功能描述:实时时钟 REAL TIME CLK W/ ALARM DS1337 COMP RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。