参数资料

| 型号: | ISL3333IRZ-T7A |

| 厂商: | Intersil |

| 文件页数: | 11/26页 |

| 文件大小: | 0K |

| 描述: | IC TXRX RS232/485 DL 2PRT 40QFN |

| 产品培训模块: | Solutions for Industrial Control Applications |

| 标准包装: | 250 |

| 类型: | 收发器 |

| 驱动器/接收器数: | 2/2 |

| 规程: | RS232,RS422,RS485 |

| 电源电压: | 3.15 V ~ 3.45 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 带卷 (TR) |

19

FN6362.0

May 27, 2008

ON/OFF) being driven to the low input state. The worst case

through the ON/OFF pin pull-up resistor when that pin is

driven low. IIL through an input pull-up resistor is ~11A (6A

22A (at VL = 3.3V) when the two SP inputs are high versus

low (next to bottom vs. top curve). SHDN IL is lowest in the

RS-232 mode, because only the DEN pins and/or the

ON/OFF pin should be driven low. When all the inputs with

pull-downs are driven high, IL drops to <<1A (see Figure

20), so to minimize power dissipation drive these inputs high

when unneeded (e.g., SP inputs aren’t used in RS-232

mode, and DEN inputs aren’t used in RS-485 mode, so drive

them high in those modes).

QFN logic input pins that are externally tied high in an

application, should use the VL supply for the high voltage

level.

RS-232 Mode Tx Enable/Disable (DEN)

The ISL3333 also adds an RS-232 mode Tx enable pin

(DENX) for each port. Driving one of these pins low disables

both drivers in the corresponding port. Because RS-232 is a

point-to-point (only one Tx allowed on the bus) standard, the

main use for this disable function is to reduce power by

eliminating the load current (approximately 1mA per Tx

output) through the 5k

Ω resistor in the Rx at the cable’s far

end. The ICC in this mode is still considerably higher than in

SHDN, but the enable time from Tx disable is much faster

(1.5s vs. 25s) than the enable time from SHDN due to the

charge pumps remaining on during Tx disable.

The DENX pin is ignored if the corresponding port is set for

RS-485 mode, and it is internally pulled high.

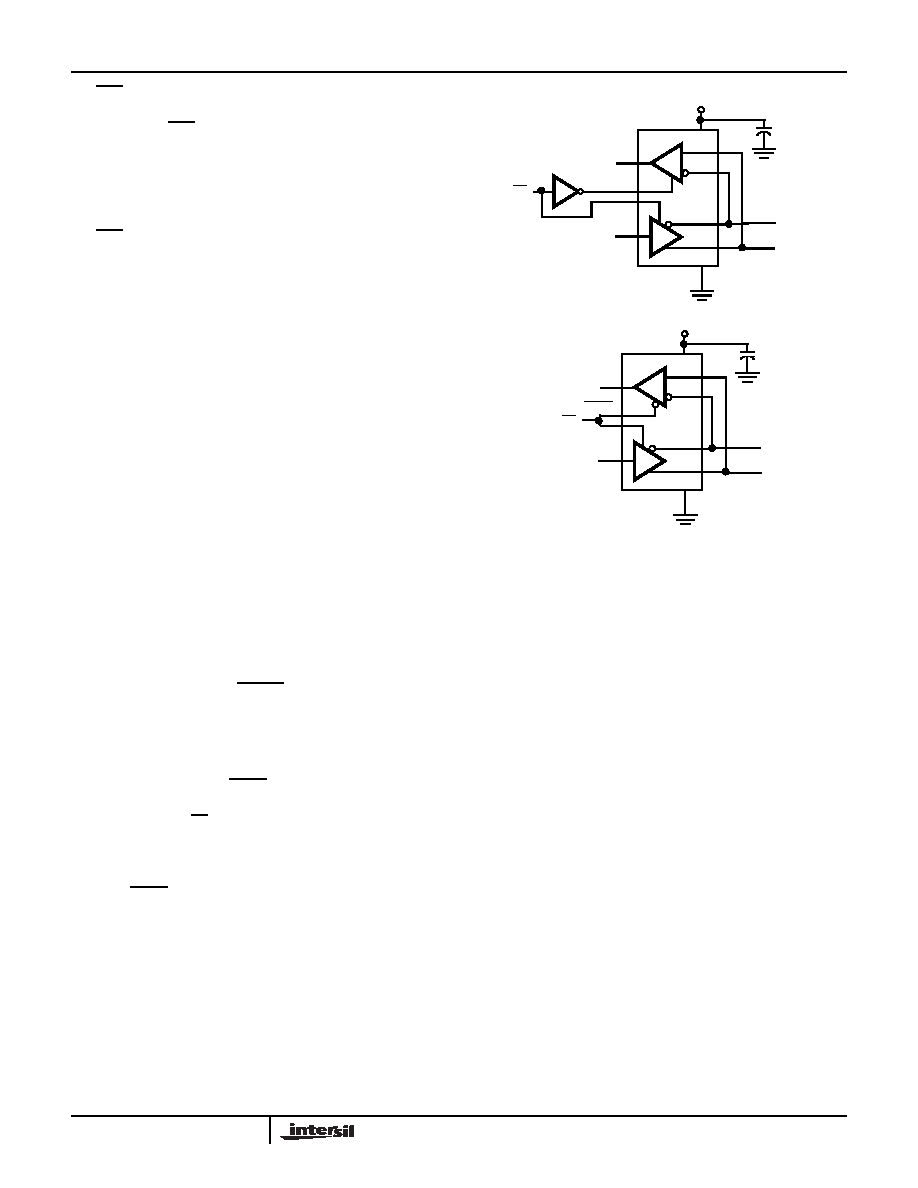

Active Low Rx Enable (RXEN)

In many RS-485 applications, especially half duplex

configurations, users like to accomplish “echo cancellation”

by disabling the corresponding receiver while its driver is

transmitting data. This function is available on the QFN

package via an active low RXEN pin for each port. The

active low function also simplifies direction control, by

allowing a single Tx/Rx direction control line. If an active high

RXEN were used, either two valuable I/O pins would be

used for direction control, or an external inverter is required

between DE and RXEN. Figure 13 details the advantage of

using the RXEN pin.

RS-485 Slew Rate Limited Data Rates

The SSOP version of this IC operates with Tx output

transitions optimized for a 20Mbps data rate. These fast

edges may increase EMI and reflection issues, even though

fast transitions aren’t required at the lower data rates used

by many applications. The ISL3333 (QFN version) solves

this problem by offering two additional, slew rate limited,

data rates that are optimized for speeds of 115kbps, and

460kbps.The slew limited edges permit longer unterminated

networks, or longer stubs off terminated busses, and help

minimize EMI and reflections. Nevertheless, for the best jitter

performance when driving long cables, the faster speed

options may be preferable, even at lower data rates. The

faster output transitions deliver less variability (jitter) when

loaded with the large capacitance associated with long

cables. Of course, faster transitions require more attention to

ensuring short stub lengths and quality terminations, so

there are trade-offs to be made. Assuming a jitter budget of

10%, it is likely better to go with the slow speed option for

data rates of 115kbps or less, to minimize fast edge effects.

Likewise, the medium speed option is a good choice for data

rates between 115kbps and 460kbps. For higher data rates,

or when the absolute best jitter is required, use the high

speed option. Speed selection is via the SPA and SPB pins

(see Table 3), and the selection pertains to each port

programmed for RS-485 mode.

Evaluation Board

An evaluation board, part number ISL3333EVAL1Z, is

available to assist in assessing the dual protocol IC’s

performance. The evaluation board contains a QFN

packaged device, but because the same die is used in all

packages, the board is also useful for evaluating the

functionality of the other versions. The board’s design allows

for evaluation of all standard features, plus the QFN specific

features. Refer to the eval board application note for details,

and contact your sales rep for ordering information.

FIGURE 13. USING ACTIVE LOW vs ACTIVE HIGH RX

ENABLE

0.1F

+

D

R

VCC

GND

RA

RXEN

DEN

DY

+3.3V

ISL3330

Tx/Rx

ACTIVE HIGH RX ENABLE

0.1F

+

D

R

VCC

GND

RA

RXEN *

DE

DY

+3.3V

ISL3333

Tx/Rx

* QFN ONLY

ACTIVE LOW RX ENABLE

Y

Z

A

B

Y

Z

A

B

ISL3332, ISL3333

相关PDF资料 |

PDF描述 |

|---|---|

| ISL34321INZ | IC SER/DESER LVDS SERDES 48TQFP |

| ISL34340INZ | IC LNG-RCH VID SERDES 64-EPTQFP |

| ISL34341INZ | IC VIDEO SERDES LONG 64-EPTQFP |

| ISL35111DRZ-TS | IC DE-EMP DRIVER SGL 16QFN |

| ISL35411DRZ-T7 | IC DVR QUAD 46QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL34321 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:16-Bit Long-Reach Video SERDES with Bi-directional Side-Channel |

| ISL34321INZ | 功能描述:串行器/解串器 - Serdes ISL34321INZ16:1 LVDS SERDES W/BCK CH EPAD RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| ISL34321INZ-T13 | 功能描述:串行器/解串器 - Serdes ISL34321INZ16:1 LVDS SERDES W/BCK CH EPAD RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| ISL34340 | 制造商:Intersil Corporation 功能描述: |

| ISL34340_0806 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:WSVGA 24-Bit Long-Reach Video SERDES with Bidirectional Side-Channel |

发布紧急采购,3分钟左右您将得到回复。