- 您现在的位置:买卖IC网 > PDF目录383129 > ISL3873AIK (INTERSIL CORP) RES 0805 1/8W 5% 1.2KOHM PDF资料下载

参数资料

| 型号: | ISL3873AIK |

| 厂商: | INTERSIL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | RES 0805 1/8W 5% 1.2KOHM |

| 中文描述: | 1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PBGA192 |

| 封装: | 14 X 14 MM, PLASTIC, BGA-192 |

| 文件页数: | 17/42页 |

| 文件大小: | 778K |

| 代理商: | ISL3873AIK |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

17

When using a 48MHz CLKIN, as is typical for 802.11 or

802.11b controllers with a USB host interface, common

divisors are 4 (12MHz) or 6 (8MHz)

The MCLK prescaler is set to divide by 16 at hardware reset

to allow initialization firmware to be executed from slow

memory devices at any CLKIN frequency. The MCLK

prescaler generates glitch free output when the divisor is

changed. This allows firmware to change the MCLK

frequency during operation, which is especially useful to

selectively reduce operating speed, thereby conserving

power, when full speed processing is not required.

Power On Reset Configuration

Power On Reset is issued to the ISL3873A with the RESET

pin or via the soft reset bit, SRESET, in the Configuration

Option Register (COR, bit 7). RESET originates from the

HOST system which applies RESET for at least 0.01ms after

V

CC

has reached 90% of its end value (see PC-Card

standard, Vol. 2, Ch. 4.12.1).

The MD[15:8] pin values are sampled during RESET or

Software Reset (SRESET). These pins have internal 50K

resistors. External pull-up or pull-down resistors (typically

10k

) are used for bits which need to be configured

differently than the default.

Table 3 summarizes the effect per pin. Table 4 provides the

MD15 and MD14 bit values required to allow the ISL3873A

to use Serial EEPROM option.

MD[11], StrIdle, has no equivalent functionality in any control

register. When asserted at reset, it will inhibit firmware

execution. This is used to allow the initial download of

firmware in “Genesis Mode”. See the Hardware Reference

Manual for more details. The latch is cleared when the

Software Reset, SRESET, COR(7) is active.

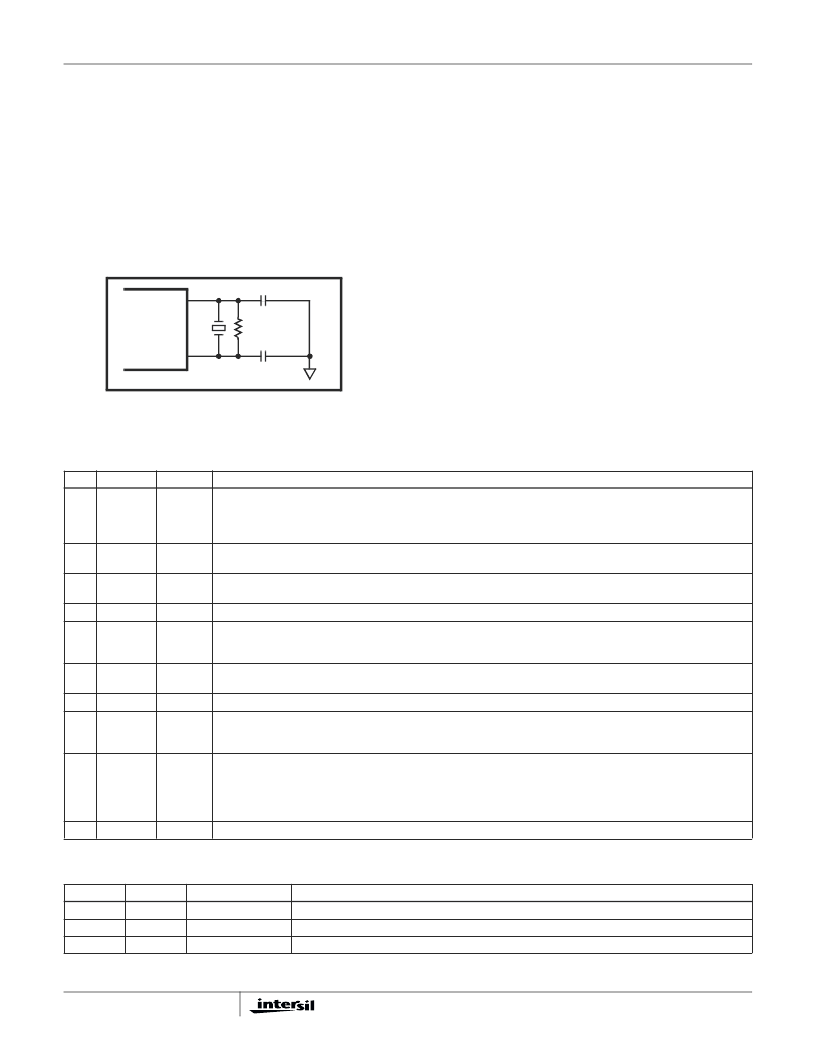

XTALIN

XTALOUT

X1

C1

C2

FIGURE 11. 32.768kHz CRYSTAL

10M

22pF

4700pF

TABLE 3. INITIALIZATION STRAPPING OPTIONS ON MBUS DATA PINS

BITS

15:14 NVtype[1:0]

NAME

DEFAULT

30

FUNCTION

Indicates type of serial NV memory to be read by initialization firmware in on-chip ROM.

Up to 8 NV device types can be encoded with (StrIdle or NVtype). If StrIdle = 0, NV memory holdsa firmware image,

and NVtype identifies 1 of 4 “large” (. = 128Kb) types. If StrIdle = 1, the NV memory just holds the CIS, and NVtype

identifies 1 of 4 “small” (< = 8Kb) types.

Use the Serial Host Interface (USB), and disable all PC Card functions except attribute space, for access to the

COR and HCR for firmware debugging support. When = 0, use the Parallel Host Interface (PC Card or ISA).

Use 4-wire interface to SRAM(CS-, OE-, WEH-, WEL-) the ISL3873A x8 SRAMs. When = 0 selects 5-wire interface

for use with x16 SRAM (CS-, OE-, WE-, UBE-, LBE-).

Start idle (wait for download from PC Card host interface).

RAM and NV space at startup is x 16. When = 0 RAM and NV space at startup is x 8. If starting from off-chip NV

memory this setting must indicate the width of the startup Flash Memory. During initialization, firmware can set

separate widths or RAM and NV space in the Memory Control Register.

Disable mapping of off-chip control store to NV space (hence map off-chip control store to RAM space). When = 0

off-chip control store is mapped to NV memory

Disable on-chip control store ROM. When = 0 enable on-chip control store ROM.

Set host interface control signals and address decoding for PC card. When = 1 set host interface signals and

address decoding is for ISA bus, with all registers in I/O space and attribute space disabled. To use ISA mode,

PHIenable must be = 1 to enable a parallel host interface.

Enable I/O space decoding for the physical FCRs. When = 1, the COR, CSR, and PRR registers are accessible at

I/O space offsets 0x40, 0x42, and 0x44 respectively. When = 0 these registers are only accessible in attribute

space. This bit is ignored when PHIenable = 0, and is overridden (forced = 1) when ISAmode =1. FCRinIO = 1 is

useful for PC Card operation (PHIenable = 1, ISAmode = 0) to allow non-OS software to access the COR/HCR in

OS environments where the system software does not permit application software to access attribute space.

b

Not assigned.

a. FCRinIO = 1 forces HAMASK [0] = 1 to expand I/O space decoding from 0 x 40 to 0 x 80 bytes.

13

SHIenable

0

12

4Wire

1

11

10

StrIdle

Mem16

0

0

9

NVds

0

8

7

ROMds

ISAmode

1

0

6

FCRinIO

0

5:0

Spare

0 x 00

TABLE 4. SERIAL EEPROM SELECTION

MD15

0

0

1

MD14

0

1

X

DEVICE TYPE

AT45DB011

24C08 (Note)

None

FUNCTION

Large Serial Device used to transfer firmware to SRAM

Small Serial Device which contains only CIS. MAC goes idle after loading CIS and waits for host.

Modes not supported in firmware at this time. Consult factory for additional device types added.

NOTE: The operating frequency of the serial port is 400kHz with a voltage of 3.3V.

ISL3873A

相关PDF资料 |

PDF描述 |

|---|---|

| ISL3874IK96 | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL3874 | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL3874IK | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL39300A-DAPDK-CD | PRISM 54Mbps Wireless Local Area Network Access Point |

| ISL39300A-DAPDK | PRISM 54Mbps Wireless Local Area Network Access Point |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL3873AIK-TK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3873BIK | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intersil Corporation 功能描述: |

| ISL3873BIK-TK | 制造商:Intersil Corporation 功能描述:1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PBGA192 |

| ISL3873IK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3873IK96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。