参数资料

| 型号: | ISL5927INZ |

| 厂商: | Intersil |

| 文件页数: | 3/13页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT CMOS DUAL 48LQFP |

| 标准包装: | 250 |

| 位数: | 14 |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 275 mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 托盘 |

| 输出数目和类型: | * |

| 采样率(每秒): | * |

11

lines, then 50

termination resistors should be placed as

close to the converter inputs as possible connected to the

digital ground plane (if separate grounds are used). These

termination resistors are not likely needed as long as the

digital waveform source is within a few inches of the DAC.

For pattern drivers with very high speed edge rates, it is

recommended that the user consider series termination (50-

200

) prior to the DAC’s inputs in order to reduce the

amount of noise.

Power Supply

Separate digital and analog power supplies are

recommended. The allowable supply range is +2.7V to

+3.6V. The recommended supply range is +3.0 to 3.6V

(nominally +3.3V) to maintain optimum SFDR. However,

operation down to +2.7V is possible with some degradation

in SFDR. Reducing the analog output current can help the

SFDR at +2.7V. The SFDR values stated in the table of

specifications were obtained with a +3.3V supply.

Ground Planes

Separate digital and analog ground planes should be used.

All of the digital functions of the device and their

corresponding components should be located over the

digital ground plane and terminated to the digital ground

plane. The same is true for the analog components and the

analog ground plane.

Noise Reduction

To minimize power supply noise, 0.1

F capacitors should be

placed as close as possible to the converter’s power supply

pins, AVDD and DVDD. Also, the layout should be designed

using separate digital and analog ground planes and these

capacitors should be terminated to the digital ground for

DVDD and to the analog ground for AVDD. Additional

filtering of the power supplies on the board is recommended.

Voltage Reference

The internal voltage reference of the device has a nominal

value of +1.23V with a

±40ppm/°C drift coefficient over the

full temperature range of the converter. It is recommended

that a 0.1

F capacitor be placed as close as possible to the

REFIO pin, connected to the analog ground. The REFLO pin

selects the reference. The internal reference can be selected

if REFLO is tied low (ground). If an external reference is

desired, then REFLO should be tied high (the analog supply

voltage) and the external reference driven into REFIO. The

full scale output current of the converter is a function of the

voltage reference used and the value of RSET. IOUT should

be within the 2mA to 22mA range, though operation below

2mA is possible, with performance degradation.

If the internal reference is used, VFSADJ will equal

approximately 1.2V. If an external reference is used, VFSADJ

will equal the external reference. The calculation for IOUT

(Full Scale) is:

IOUT(Full Scale) = (VFSADJ/RSET) X 32.

If the full scale output current is set to 20mA by using the

internal voltage reference (1.23V) and a 1.91k

RSET

resistor, then the input coding to output current will resemble

the following:

Analog Output

IOUTA and IOUTB are complementary current outputs. The

sum of the two currents is always equal to the full scale

output current minus one LSB. If single ended use is

desired, a load resistor can be used to convert the output

current to a voltage. It is recommended that the unused

output be either grounded or equally terminated. The voltage

developed at the output must not violate the output voltage

compliance range of -1.0V to 1.25V. ROUT (the impedance

loading each current output) should be chosen so that the

desired output voltage is produced in conjunction with the

output full scale current. If a known line impedance is to be

driven, then the output load resistor should be chosen to

match this impedance. The output voltage equation is:

VOUT = IOUT X ROUT.

The most effective method for reducing the power

consumption is to reduce the analog output current, which

dominates the supply current. The maximum recommended

output current is 20mA.

Differential Output

IOUTA and IOUTB can be used in a differential-to-single-

ended arrangement to achieve better harmonic rejection.

will provide a 500mV (-2.5dBm) signal at the output of the

transformer if the full scale output current of the DAC is set

to 20mA (used for the electrical specifications table). Values

of RDIFF = 100 and RLOAD = 50 were used for the typical

performance curves to increase the output power and the

dynamic range. The center tap in Figure 13 must be

grounded.

In the circuit in Figure 14, the user is left with the option to

ground or float the center tap. The DC voltage that will exist

at either IOUTA or IOUTB if the center tap is floating is

IOUTDC x (RA//RB) V because RDIFF is DC shorted by the

transformer. If the center tap is grounded, the DC voltage is

0V. Recommended values for the circuit in Figure 14 are

RA = RB = 50, RDIFF = 100, assuming RLOAD = 50.

same, however leaving the center tap of Figure 14 floating

allows the circuit to find a more balanced virtual ground,

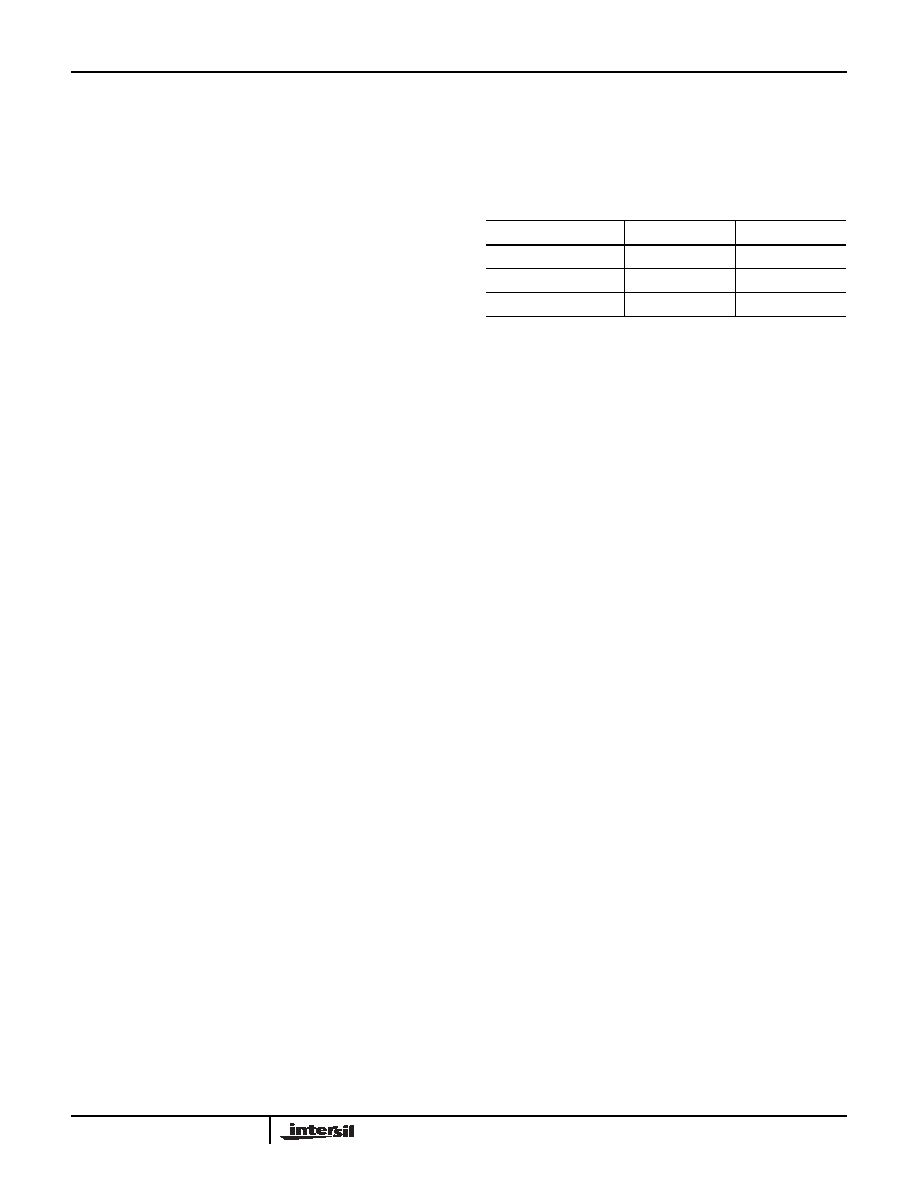

TABLE 1. INPUT CODING vs OUTPUT CURRENT WITH

INTERNAL REFERENCE (1.23V TYP) AND

RSET = 1.91k

INPUT CODE (D13-D0)

IOUTA (mA)

IOUTB (mA)

11 1111 1111 1111

20.6

0

10 0000 0000 0000

10.3

00 0000 0000 0000

0

20.6

ISL5927

相关PDF资料 |

PDF描述 |

|---|---|

| ISL5929INZ | IC DAC 14BIT CMOS DUAL 48LQFP |

| ISL5957IBZ | CONV D/A 14-BIT 3.3V 28-SOIC |

| ISL5961/2IBZ | CONV D/A 14-BIT 3.3V 28-SOIC |

| ISL59911IRZ | IC RCVR/EQUALZR TRPL DIFF 32QFN |

| ISL59913IRZ-T7 | IC RCVR/EQUALZR TRPL DIFF 28-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL5929 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, +3.3V, 130/210MSPS, CommLink TM High Speed D/A Converter |

| ISL5929/2IN | 功能描述:IC DAC DUAL 14BIT 3.3V 48-MQFP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:2,400 系列:- 设置时间:- 位数:18 数据接口:串行 转换器数目:3 电压电源:模拟和数字 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:36-TFBGA 供应商设备封装:36-TFBGA 包装:带卷 (TR) 输出数目和类型:* 采样率(每秒):* |

| ISL59292IN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, +3.3V, 130/210MSPS, CommLink TM High Speed D/A Converter |

| ISL5929EVAL1 | 功能描述:ISL5929 HIGH SPEED D/A EVALUA RoHS:否 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:CommLink™ 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| ISL5929IN | 功能描述:IC DAC DUAL 14BIT 3.3V 48-MQFP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:2,400 系列:- 设置时间:- 位数:18 数据接口:串行 转换器数目:3 电压电源:模拟和数字 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:36-TFBGA 供应商设备封装:36-TFBGA 包装:带卷 (TR) 输出数目和类型:* 采样率(每秒):* |

发布紧急采购,3分钟左右您将得到回复。