参数资料

| 型号: | ISL6334IRZ-T |

| 厂商: | Intersil |

| 文件页数: | 19/31页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM 4PHASE BUCK 40-QFN |

| 标准包装: | 4,000 |

| 应用: | 控制器,Intel VR11.1 |

| 输入电压: | 3 V ~ 12 V |

| 输出数: | 1 |

| 输出电压: | 0.5 V ~ 1.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘 |

| 供应商设备封装: | 40-QFN(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

�� �

�

�

�ISL6334,� ISL6334A�

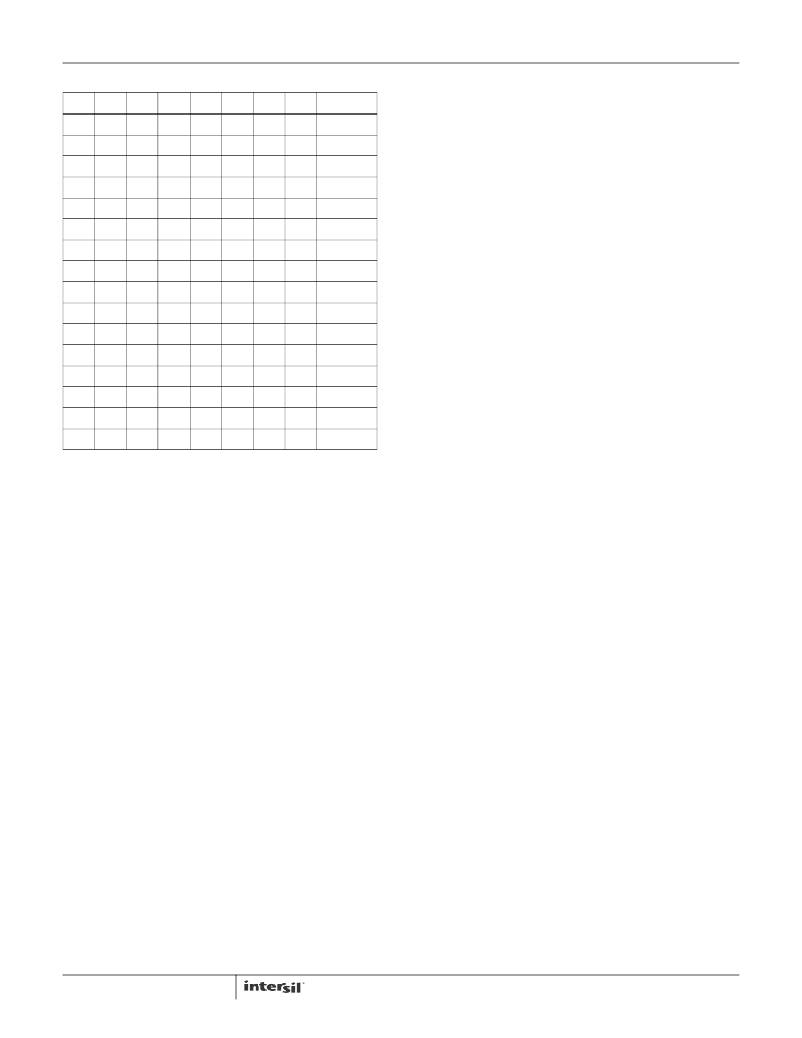

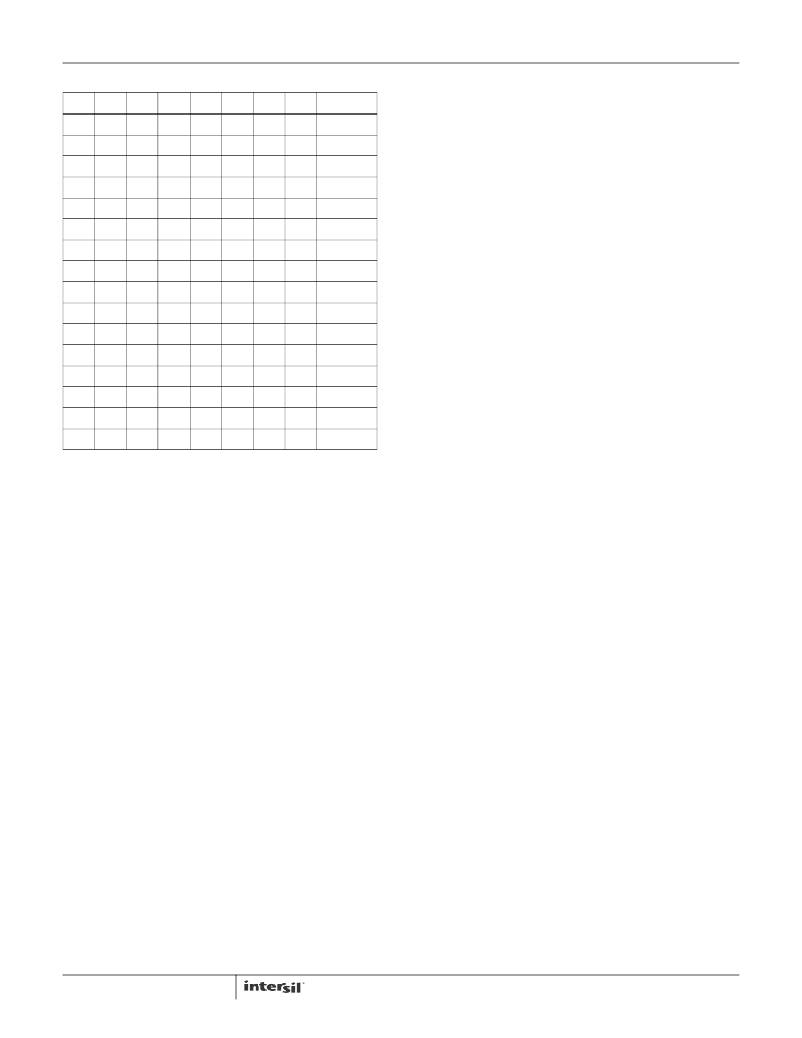

�TABLE� 2.� VR11� VID� 8� BIT� (Continued)�

�VID7� VID6� VID5� VID4� VID3� VID2� VID1� VID0� VOLTAGE�

�V� DROOP� .� The� output� voltage� as� a� function� of� load� current� is�

�derived� by� combining� Equation� 8� with� the� appropriate�

�1�

�0�

�1�

�0�

�0�

�1�

�0�

�1�

�0.58125�

�sample� current� expression� defined� by� the� current� sense�

�method� employed,� as� shown� in� Equation� 9:�

�V� OUT� =� V� REF� –� V� OFS� –� ?� -----------------� ------------------� R� FB� ?�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�1�

�0.57500�

�0.56875�

�?� I� LOAD� R� X� ?�

�?� N� R� ISEN� ?�

�(EQ.� 9)�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�0.56250�

�0.55625�

�0.55000�

�0.54375�

�0.53750�

�0.53125�

�0.52500�

�where� V� REF� is� the� reference� voltage,� V� OFS� is� the�

�programmed� offset� voltage,� I� LOAD� is� the� total� output� current�

�of� the� converter,� R� ISEN� is� the� sense� resistor� connected� to�

�the� ISEN+� pin,� and� R� FB� is� the� feedback� resistor,� N� is� the�

�active� channel� number,� and� R� X� is� the� DCR,� or� R� SENSE�

�depending� on� the� sensing� method.�

�Therefore,� the� equivalent� loadline� impedance,� i.e.� Droop�

�impedance,� is� equal� to� Equation� 10:�

�R� LL� =� ------------� ------------------�

�R� ISEN�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�0.51875�

�0.51250�

�N�

�R� FB� R� X�

�(EQ.� 10)�

�1�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�1�

�1�

�1�

�0�

�0�

�1�

�0.50625�

�0.50000�

�OFF�

�OFF�

�Output-Voltage� Offset� Programming�

�The� ISL6334,� ISL6334A� allows� the� designer� to� accurately�

�adjust� the� offset� voltage.� When� a� resistor,� R� OFS� ,� is�

�connected� between� OFS� to� VCC,� the� voltage� across� it� is�

�regulated� to� 1.6V.� This� causes� a� proportional� current� (I� OFS� )�

�to� flow� into� OFS.� If� R� OFS� is� connected� to� ground,� the� voltage�

�Load-Line� Regulation�

�Some� microprocessor� manufacturers� require� a� precisely�

�controlled� output� resistance.� This� dependence� of� output�

�voltage� on� load� current� is� often� termed� “droop”� or� “load� line”�

�regulation.� By� adding� a� well� controlled� output� impedance,�

�the� output� voltage� can� effectively� be� level� shifted� in� a�

�direction,� which� works� to� achieve� the� load-line� regulation�

�required� by� these� manufacturers.�

�across� it� is� regulated� to� 0.4V,� and� I� OFS� flows� out� of� OFS.� A�

�resistor� between� DAC� and� REF,� R� REF� ,� is� selected� so� that�

�the� product� (I� OFS� x� R� OFS� )� is� equal� to� the� desired� offset�

�voltage.� These� functions� are� shown� in� Figure� 7.�

�Once� the� desired� output� offset� voltage� has� been� determined,�

�use� Equations� 11� and� 12� to� calculate� R� OFS� :�

�For� Positive� Offset� (connect� R� OFS� to� VCC):�

�R� OFS� =� ------------------------------�

�R� OFS� =� ------------------------------�

�In� other� cases,� the� designer� may� determine� that� a� more�

�cost-effective� solution� can� be� achieved� by� adding� droop.�

�Droop� can� help� to� reduce� the� output-voltage� spike� that�

�results� from� fast� load-current� demand� changes.�

�The� magnitude� of� the� spike� is� dictated� by� the� ESR� and� ESL�

�of� the� output� capacitors� selected.� By� positioning� the� no-load�

�voltage� level� near� the� upper� specification� limit,� a� larger�

�negative� spike� can� be� sustained� without� crossing� the� lower�

�limit.� By� adding� a� well� controlled� output� impedance,� the�

�output� voltage� under� load� can� effectively� be� level� shifted�

�down� so� that� a� larger� positive� spike� can� be� sustained� without�

�crossing� the� upper� specification� limit.�

�As� shown� in� Figure� 6,� a� current� proportional� to� the� average�

�current� of� all� active� channels,� I� AVG� ,� flows� from� FB� through� a�

�load-line� regulation� resistor� R� FB� .� The� resulting� voltage� drop�

�across� R� FB� is� proportional� to� the� output� current,� effectively�

�creating� an� output� voltage� droop� with� a� steady-state� value�

�defined� as� shown� in� Equation� 8:�

�V� DROOP� =� I� AVG� R� FB�

�(EQ.� 8)�

�The� regulated� output� voltage� is� reduced� by� the� droop� voltage�

�19�

�1.6� � R� REF�

�V� OFFSET�

�For� Negative� Offset� (connect� R� OFS� to� GND):�

�0.4� � R� REF�

�V� OFFSET�

�(EQ.� 11)�

�(EQ.� 12)�

�FN6482.2�

�February� 1,� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| RCA30DRSZ-S273 | CONN EDGECARD 60POS DIP .125 SLD |

| AMM15DRKH-S13 | CONN EDGECARD 30POS .156 EXTEND |

| GCA30DTMT-S273 | CONN EDGECARD 60POS R/A .125 SLD |

| GSM43DSEN | CONN EDGECARD 86POS .156 EYELET |

| GCA30DTBT-S273 | CONN EDGECARD 60POS R/A .125 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6336ACRZ | 功能描述:IC CTRLR PWM 6PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6336ACRZ-T | 功能描述:IC CTRLR PWM 6PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6336AIRZ | 功能描述:IC CTRLR PWM 6PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6336AIRZ-T | 功能描述:IC CTRLR PWM 6PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6336BCRZ | 功能描述:IC CTRLR PWM SYNC BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。