- 您现在的位置:买卖IC网 > PDF目录20558 > ISL6612BIRZ (Intersil)IC MOSFET DRVR SYNC BUCK 10-DFN PDF资料下载

参数资料

| 型号: | ISL6612BIRZ |

| 厂商: | Intersil |

| 文件页数: | 8/12页 |

| 文件大小: | 0K |

| 描述: | IC MOSFET DRVR SYNC BUCK 10-DFN |

| 标准包装: | 100 |

| 配置: | 高端和低端,同步 |

| 输入类型: | PWM |

| 延迟时间: | 10ns |

| 电流 - 峰: | 1.25A |

| 配置数: | 1 |

| 输出数: | 2 |

| 高端电压 - 最大(自引导启动): | 36V |

| 电源电压: | 7 V ~ 13.2 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-VFDFN 裸露焊盘 |

| 供应商设备封装: | 10-DFN(3x3) |

| 包装: | 管件 |

�� �

�

�

�ISL6612B,� ISL6613B�

�This� feature� helps� prevent� a� negative� transient� on� the� output�

�voltage� when� the� output� is� shut� down,� eliminating� the�

�Schottky� diode� that� is� used� in� some� systems� for� protecting�

�the� load� from� reversed� output� voltage� events.�

�In� addition,� more� than� 400mV� hysteresis� also� incorporates�

�into� the� three-state� shutdown� window� to� eliminate� PWM�

�input� oscillations� due� to� the� capacitive� load� seen� by� the�

�PWM� input� through� the� body� diode� of� the� controller� ’s� PWM�

�output� when� the� power-up� and/or� power-down� sequence� of�

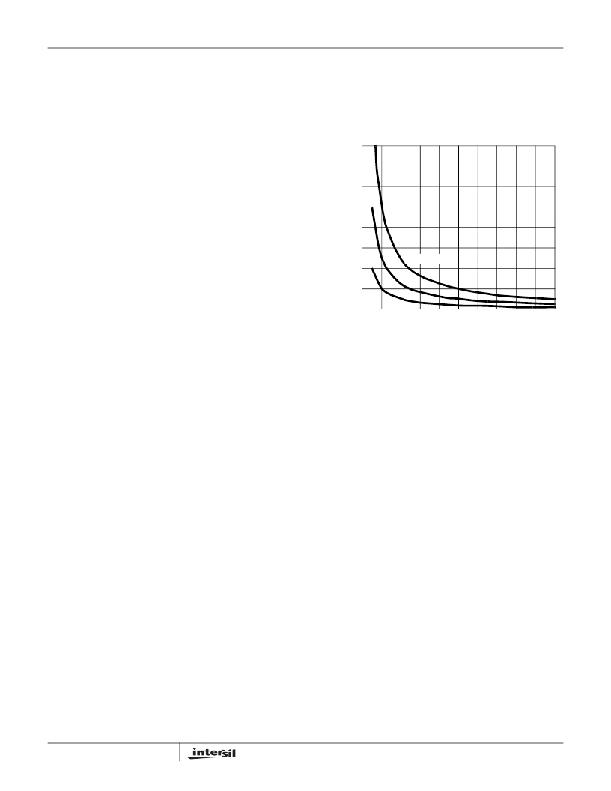

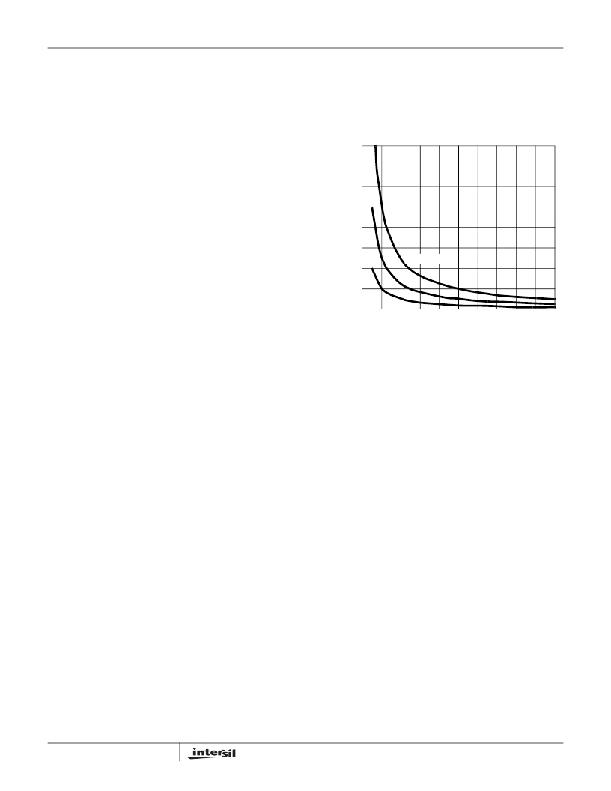

�As� an� example,� suppose� two� IRLR7821� FETs� are� chosen� as�

�the� upper� MOSFETs.� The� gate� charge,� Q� G� ,� from� the� data�

�sheet� is� 10nC� at� 4.5V� (V� GS� )� gate-source� voltage.� Then� the�

�Q� GATE� is� calculated� to� be� 53nC� for� UVCC� (i.e.� PVCC� in�

�ISL6613B,� VCC� in� ISL6612B)� =12V.� We� will� assume� a�

�200mV� droop� in� drive� voltage� over� the� PWM� cycle.� We� find�

�that� a� bootstrap� capacitance� of� at� least� 0.267� μ� F� is� required.�

�1.6�

�1.4�

�bias� supplies� of� the� driver� and� PWM� controller� are� required.�

�1.2�

�Power-On� Reset� (POR)� Function�

�During� initial� start-up,� the� VCC� voltage� rise� is� monitored.�

�Once� the� rising� VCC� voltage� exceeds� 6.9V� (typically),�

�operation� of� the� driver� is� enabled� and� the� PWM� input� signal�

�takes� control� of� the� gate� drives.� If� VCC� drops� below� the�

�falling� threshold� of� 5.6V� (typically),� operation� of� the� driver� is�

�disabled.�

�1.�

�0.8�

�0.6�

�0.4�

�Q� GATE� = 100nC�

�50nC�

�Pre-POR� Overvoltage� Protection�

�0.2�

�20nC�

�Prior� to� VCC� exceeding� its� POR� level,� the� upper� gate� is� held�

�low� and� the� lower� gate� is� controlled� by� the� overvoltage�

�0.0�

�0.0�

�0.1�

�0.2�

�0.3�

�0.4�

�0.5�

�0.6�

�0.7�

�0.8�

�0.9�

�1.0�

�protection� circuits� during� initial� startup.� The� PHASE� is�

�connected� to� the� gate� of� the� low� side� MOSFET� (LGATE),�

�which� provides� some� protection� to� the� microprocessor� if� the�

�upper� MOSFET(s)� is� shorted� during� initial� start-up.� For�

�complete� protection,� the� low� side� MOSFET� should� have� a�

�gate� threshold� well� below� the� maximum� voltage� rating� of� the�

�load/microprocessor.�

�When� VCC� drops� below� its� POR� level,� both� gates� pull� low�

�and� the� Pre-POR� overvoltage� protection� circuits� are� not�

�activated� until� VCC� resets.�

�Internal� Bootstrap� Device�

�Both� drivers� feature� an� internal� bootstrap� schottky� diode.�

�Simply� adding� an� external� capacitor� across� the� BOOT� and�

�PHASE� pins� completes� the� bootstrap� circuit.� The� bootstrap�

�function� is� also� designed� to� prevent� the� bootstrap� capacitor�

�from� overcharging� due� to� the� large� negative� swing� at� the�

�trailing-edge� of� the� PHASE� node.� This� reduces� voltage�

�stress� on� the� boot� to� phase� pins.�

�The� bootstrap� capacitor� must� have� a� maximum� voltage�

�rating� above� UVCC� +� 5V� and� its� capacitance� value� can� be�

�chosen� from� the� following� equation:�

�Δ� V� BOOT_CAP� (V)�

�FIGURE� 2.� BOOTSTRAP� CAPACITANCE� vs� BOOT� RIPPLE�

�VOLTAGE�

�Gate� Drive� Voltage� Versatility�

�The� ISL6612B� and� ISL6613B� provide� the� user� flexibility� in�

�choosing� the� gate� drive� voltage� for� efficiency� optimization.�

�The� ISL6612B� upper� gate� drive� can� be� driven� above� VCC�

�rising� POR� (7V)� to� 12V,� but� the� lower� drive� rail� can� range�

�from� 12V� down� to� 5V� depending� on� what� voltage� is� applied�

�to� PVCC.� The� ISL6613B� ties� the� upper� and� lower� drive� rails�

�together.� Simply� applying� a� voltage� from� 5V� up� to� 12V� on�

�PVCC� sets� both� gate� drive� rail� voltages� simultaneously.�

�Power� Dissipation�

�Package� power� dissipation� is� mainly� a� function� of� the�

�switching� frequency� (F� SW� ),� the� output� drive� impedance,� the�

�external� gate� resistance,� and� the� selected� MOSFET’s�

�internal� gate� resistance� and� total� gate� charge.� Calculating�

�the� power� dissipation� in� the� driver� for� a� desired� application� is�

�critical� to� ensure� safe� operation.� Exceeding� the� maximum�

�allowable� power� dissipation� level� will� push� the� IC� beyond� the�

�maximum� recommended� operating� junction� temperature� of�

�C� BOOT_CAP� ≥� --------------------------------------�

�Q� GATE�

�Δ� V� BOOT_CAP�

�(EQ.� 1)�

�+125°C.� The� maximum� allowable� IC� power� dissipation� for�

�the� SO8� package� is� approximately� 800mW� at� room�

�temperature,� while� the� power� dissipation� capacity� in� the�

�Q� GATE� =� ------------------------------------� ?� N� Q1�

�Q� G1� ?� UVCC�

�V� GS1�

�where� Q� G1� is� the� amount� of� gate� charge� per� upper� MOSFET�

�at� V� GS1� gate-source� voltage� and� N� Q1� is� the� number� of�

�control� MOSFETs.� The� Δ� V� BOOT_CAP� term� is� defined� as� the�

�allowable� droop� in� the� rail� of� the� upper� gate� drive.�

�8�

�EPSOIC� and� DFN� packages,� with� an� exposed� heat� escape�

�pad,� is� more� than� 2W� and� 1.5W,� respectively.� Both� EPSOIC�

�and� DFN� packages� are� more� suitable� for� high� frequency�

�applications.� See� Layout� Considerations� paragraph� for�

�thermal� transfer� improvement� suggestions.� When� designing�

�the� driver� into� an� application,� it� is� recommended� that� the�

�following� calculation� is� used� to� ensure� safe� operation� at� the�

�FN9205.4�

�May� 1,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| M7VXK-3706J | D-SUB CABLE - MMU37K/MC37G/X |

| M7VXK-2506R | D-SUB CABLE - MMU25K/MC26M/X |

| VE-2NF-CY-B1 | CONVERTER MOD DC/DC 72V 50W |

| T95V335K020CSAL | CAP TANT 3.3UF 20V 10% 1410 |

| VE-2NB-CY-B1 | CONVERTER MOD DC/DC 95V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6612BIRZ-T | 功能描述:IC MOSFET DRVR SYNC BUCK 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

| ISL6612CB | 功能描述:IC MOSFET DRVR SYNC BUCK 8-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:50 系列:- 配置:低端 输入类型:非反相 延迟时间:40ns 电流 - 峰:9A 配置数:1 输出数:1 高端电压 - 最大(自引导启动):- 电源电压:4.5 V ~ 35 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:TO-263-6,D²Pak(5 引线+接片),TO-263BA 供应商设备封装:TO-263 包装:管件 |

| ISL6612CB-T | 功能描述:IC MOSFET DRVR SYNC BUCK 8-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:50 系列:- 配置:低端 输入类型:非反相 延迟时间:40ns 电流 - 峰:9A 配置数:1 输出数:1 高端电压 - 最大(自引导启动):- 电源电压:4.5 V ~ 35 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:TO-263-6,D²Pak(5 引线+接片),TO-263BA 供应商设备封装:TO-263 包装:管件 |

| ISL6612CBZ | 功能描述:IC DRVR MOSF SYNC BUCK OTP 8SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

| ISL6612CBZA | 功能描述:IC MOSFET DRVR SYNC BUCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - MOSFET,电桥驱动器 - 外部开关 系列:- 标准包装:6,000 系列:* |

发布紧急采购,3分钟左右您将得到回复。