参数资料

| 型号: | ISL80101IRAJZ-TK |

| 厂商: | Intersil |

| 文件页数: | 8/11页 |

| 文件大小: | 0K |

| 描述: | IC REG LDO ADJ 1A 10DFN |

| 产品培训模块: | Patient Monitoring and Diagnostic Equipment Solutions Solutions for Test and Measurement Equipment |

| 标准包装: | 1 |

| 稳压器拓扑结构: | 正,可调式 |

| 输出电压: | 0.8 V ~ 5 V |

| 输入电压: | 2.2 V ~ 6 V |

| 电压 - 压降(标准): | 0.13V @ 1A |

| 稳压器数量: | 1 |

| 电流 - 输出: | 1A(最小值) |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-VFDFN 裸露焊盘 |

| 供应商设备封装: | 10-DFN(3x3) |

| 包装: | 标准包装 |

| 其它名称: | ISL80101IRAJZ-TKDKR |

�� �

�

�

�ISL80101�

�Typical� Operating� Performance�

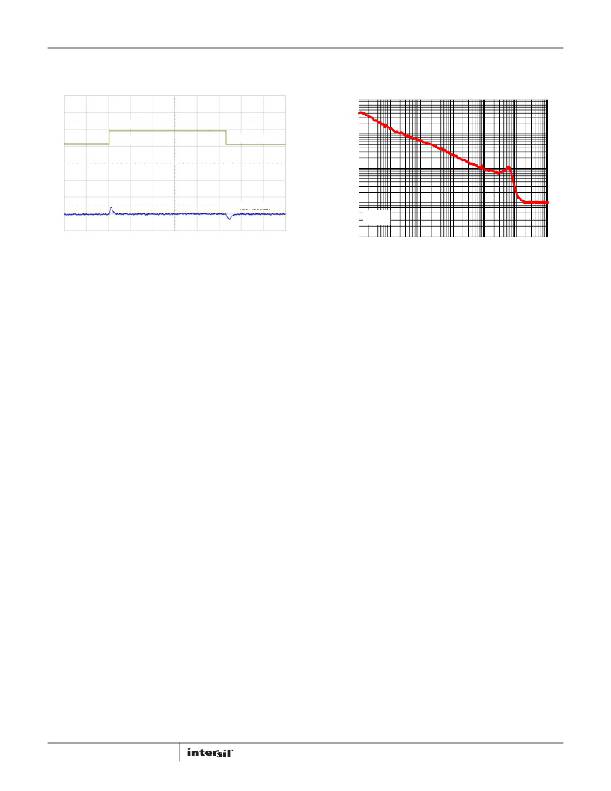

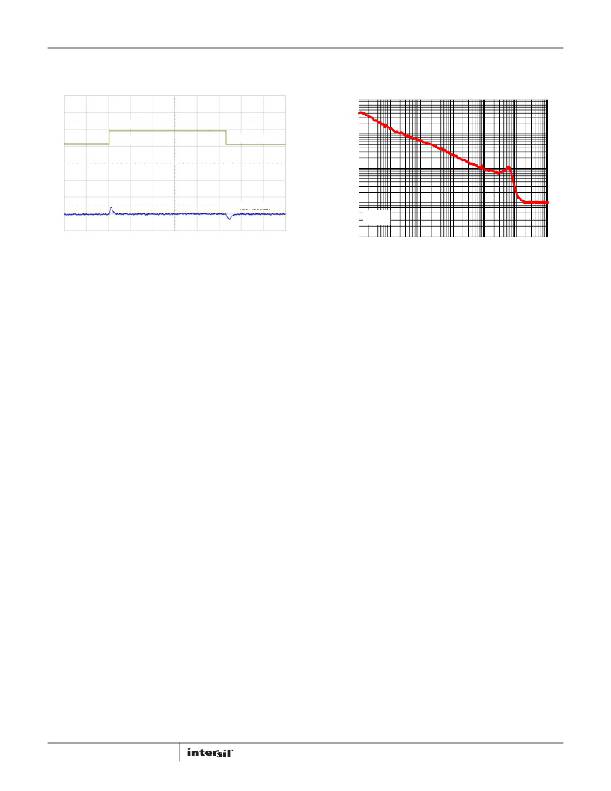

�Unless� otherwise� noted:� V� IN� =� 2.2V,� V� OUT� =� 1.8V,� C� IN� =� C� OUT� =� 10μF,� T� J� =� +25°C,� I� L� =� 0A.� (Continued)�

�10�

�V� IN� =� 3.8V�

�V� IN� =� 2.25V�

�V� IN� =� 2V/DIV�

�V� OUT� =� 5mV/DIV�

�1�

�0.1�

�0.01�

�I� L� =� 1A�

�TIME� (200μs/DIV)�

�0.001�

�10�

�100�

�1k�

�10k�

�100k�

�1M�

�10M�

�FREQUENCY� (Hz)�

�FIGURE� 14.� LINE� TRANSIENT� RESPONSE�

�Applications� Information�

�FIGURE� 15.� OUTPUT� NOISE� SPECTRAL� DENSITY�

�C� SS� and� the� feedback� reference� voltage� is� clamped� to� the�

�voltage� across� it.� The� start-up� time� is� set� by� Equation� 1.�

�Input� Voltage� Requirements�

�The� ISL80101� is� capable� of� delivering� the� following� fixed� output�

�2� μ� A�

�C� SS� x0.5�

�t� start� =� ----------------------�

�(EQ.� 1)�

�V� OUT� xC� OUT� x2� μ� A�

�C� SS� =� ---------------------------------------------�

�voltages:� 1.8V,� 2.5V,� 3.3V,� 5.0V.� Due� to� the� nature� of� an� LDO,� V� IN�

�must� be� some� margin� higher� than� V� OUT� plus� dropout� at� the�

�maximum� rated� current� of� the� application� if� active� filtering�

�(PSRR)� is� expected� from� V� IN� to� V� OUT� .� The� generous� dropout�

�specification� of� this� family� of� LDOs� allows� applications� to� design�

�a� level� of� efficiency.�

�Enable� Operation�

�The� ENABLE� turn-on� threshold� is� typically� 800mV� with� 80mV� of�

�hysteresis.� An� internal� pull-up� or� pull-down� resistor� to� change�

�these� values� is� available� upon� request.� As� a� result,� this� pin� must�

�not� be� left� floating,� and� should� be� tied� to� V� IN� if� not� used.� A� 1k� Ω� to�

�10k� Ω� pull-up� resistor� is� required� for� applications� that� use� open�

�collector� or� open� drain� outputs� to� control� the� ENABLE� pin.� The�

�ENABLE� pin� may� be� connected� directly� to� V� IN� for� applications�

�with� outputs� that� are� always� on.�

�Power-Good� Operation�

�PG� is� a� logic� output� that� indicates� the� status� of� V� OUT� and� V� IN� .� The�

�PG� flag� is� an� open-drain� NMOS� that� can� sink� up� to� 10mA� during� a�

�fault� condition.� The� PG� pin� requires� an� external� pull-up� resistor�

�typically� connected� to� the� V� OUT� pin.� The� PG� pin� should� not� be�

�pulled� up� to� a� voltage� source� greater� than� V� IN� .� PG� goes� low� when�

�the� output� voltage� drops� below� 84%� of� the� nominal� output� voltage� or�

�if� the� part� is� disabled.� PG� functions� during� current� limit� and� thermal�

�shutdown.� For� applications� not� using� this� feature,� connect� this� pin� to�

�ground.�

�Soft-Start� Operation�

�The� soft-start� circuit� controls� the� rate� at� which� the� output� voltage�

�rises� up� to� regulation� at� power-up� or� LDO� enable.� This� start-up�

�ramp� time� can� be� set� by� adding� an� external� capacitor� from� the�

�SS� pin� to� ground.� An� internal� 2μA� current� source� charges� up� this�

�8�

�Equation� 2� determines� the� C� SS� required� for� a� specific� start-up�

�in-rush� current,� where� V� OUT� is� the� output� voltage,� C� OUT� is� the�

�total� capacitance� on� the� output� and� I� INRUSH� is� the� desired� in-rush�

�current.�

�(EQ.� 2)�

�I� INRUSH� x0.5V�

�The� external� capacitor� is� always� discharged� to� ground� at� the�

�beginning� of� start-up� or� enabling.�

�External� Capacitor� Requirements�

�External� capacitors� are� required� for� proper� operation.� Careful�

�attention� must� be� paid� to� the� layout� guidelines� and� selection� of�

�capacitor� type� and� value� to� ensure� optimal� performance.�

�OUTPUT� CAPACITOR�

�The� ISL80101� applies� state-of-the-art� internal� compensation� to�

�keep� the� selection� of� the� output� capacitor� simple� for� the�

�customer.� Stable� operation� over� full� temperature,� V� IN� range,�

�V� OUT� range� and� load� extremes� are� guaranteed� for� all� capacitor�

�types� and� values� assuming� a� minimum� of� 10μF� X5R/X7R� is� used�

�for� local� bypass� on� V� OUT� .� This� output� capacitor� must� be�

�connected� to� the� V� OUT� and� GND� pins� of� the� LDO� with� PCB� traces�

�no� longer� than� 0.5cm.�

�There� is� a� growing� trend� to� use� very-low� ESR� multilayer� ceramic�

�capacitors� (MLCC)� because� they� can� support� fast� load� transients�

�and� also� bypass� very� high� frequency� noise� from� other� sources.�

�However,� the� effective� capacitance� of� MLCCs� drops� with� applied�

�voltage,� age,� and� temperature.� X7R� and� X5R� dieletric� ceramic�

�capacitors� are� strongly� recommended� as� they� typically� maintain�

�a� capacitance� range� within� ±20%� of� nominal� voltage� over� full�

�operating� ratings� of� temperature� and� voltage.�

�FN6931.1�

�August� 31,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL80103IRAJZ | IC REG LDO ADJ 3A 10DFN |

| ISL8010IUZ | IC REG BUCK SYNC ADJ 0.6A 10MSOP |

| ISL80113IRAJZ | IC REG LDO ADJ 3A 10-DFN |

| ISL8011IRZ-T | IC REG BUCK SYNC ADJ 1.2A 10DFN |

| ISL80121IR50Z | IC REG LDO 5V 1A 10DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL80102 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Performance 2A and 3A LDOs |

| ISL80102_10 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Performance 2A and 3A Linear Regulators |

| ISL80102_11 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Performance 2A and 3A Linear Regulators |

| ISL80102_13 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Performance 2A and 3A Linear Regulators |

| ISL80102EVAL2Z | 功能描述:EVAL BOARD FOR ISL80102 RoHS:是 类别:编程器,开发系统 >> 评估板 - 线性稳压器 (LDO) 系列:- 产品变化通告:1Q2012 Discontinuation 30/Mar/2012 设计资源:NCP590MNDPTAGEVB Gerber Files 标准包装:1 系列:- 每 IC 通道数:2 - 双 输出电压:1.8V,2.8V 电流 - 输出:300mA 输入电压:2.1 ~ 5.5 V 稳压器类型:正,固定式 工作温度:-40°C ~ 85°C 板类型:完全填充 已供物品:板 已用 IC / 零件:NCP590MNDP 其它名称:NCP590MNDPTAGEVB-NDNCP590MNDPTAGEVBOS |

发布紧急采购,3分钟左右您将得到回复。