- 您现在的位置:买卖IC网 > PDF目录15162 > ISL8120CRZ-T (Intersil)IC REG CTRLR BUCK PWM VM 32-QFN PDF资料下载

参数资料

| 型号: | ISL8120CRZ-T |

| 厂商: | Intersil |

| 文件页数: | 27/35页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 32-QFN |

| 标准包装: | 6,000 |

| PWM 型: | 电压模式 |

| 输出数: | 2 |

| 频率 - 最大: | 1.5MHz |

| 占空比: | 90% |

| 电源电压: | 3 V ~ 22 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页

�� �

�

�

�ISL8120�

�The� signal� I� AVG� is� then� subtracted� from� the� individual�

�channel’s� scaled� current� (I� CS1� or� I� CS2� )� to� produce� a� current�

�correction� signal� for� each� channel.� The� current� correction�

�undershoot/overshoot� during� load� transient� and� start-up.� C� is�

�typically� set� to� 0.1μF� or� higher,� while� R� is� calculated� with�

�Equation� 5.�

�R� =� ------------------------�

�signal� keeps� each� channel’s� output� current� contribution�

�balanced� relative� to� the� other� active� channel.�

�L�

�C� ?� DCR�

�(EQ.� 5)�

�For� multiphase� operation,� the� share� bus� (V� ISHARE� )�

�represents� the� average� current� of� all� active� channels� and�

�compares� with� each� IC’s� average� current� (I� AVG_CS� equals� to�

�I� AVG� or� I� CS1� depending� upon� the� configuration,� represented�

�by� V� ISET� )� to� generate� current� share� error� signal� (I� CS_ERR� )�

�for� each� individual� channel.� Each� current� correction� signal� is�

�then� subtracted� from� the� error� amplifier� output� and� fed� to� the�

�individual� channel� PWM� circuits.�

�When� both� channels� operate� independently,� the� average�

�function� is� disabled� and� generates� zero� average� current�

�(I� AVG� =� 0),� and� the� current� correction� block� of� Channel� 2� is�

�also� disabled.� The� I� AVG_CS� is� the� Channel� 1� current� I� CS1� .�

�The� Channel� 1� makes� any� necessary� current� correction� by�

�comparing� its� channel� current� (represented� by� V� ISET� )� with�

�the� share� bus� (V� ISHARE� ).� When� the� share� bus� does� not�

�connect� to� other� ICs,� the� ISET� and� ISHARE� pins� can� be�

�shorted� together� and� grounded� via� a� single� resistor� to�

�ensure� zero� share� error.�

�Note� that� the� common� mode� input� voltage� range� of� the�

�current� sense� amplifiers� is� VCC� -� 1.8V.� Therefore,� the�

�r� DS(ON)� sensing� should� be� used� for� applications� with� output�

�voltage� greater� than� VCC� -� 1.8V.� For� example,� an�

�application� of� 3.3V� output� is� suggested� to� use� r� DS(ON)�

�sensing.�

�In� addition,� the� R-C� network� components� (for� DCR� sensing)�

�are� selected� such� that� the� RC� time� constant� matches� the�

�inductor� L/DCR� time� constant.� Otherwise,� it� could� cause�

�ERROR�

�AMP� 1�

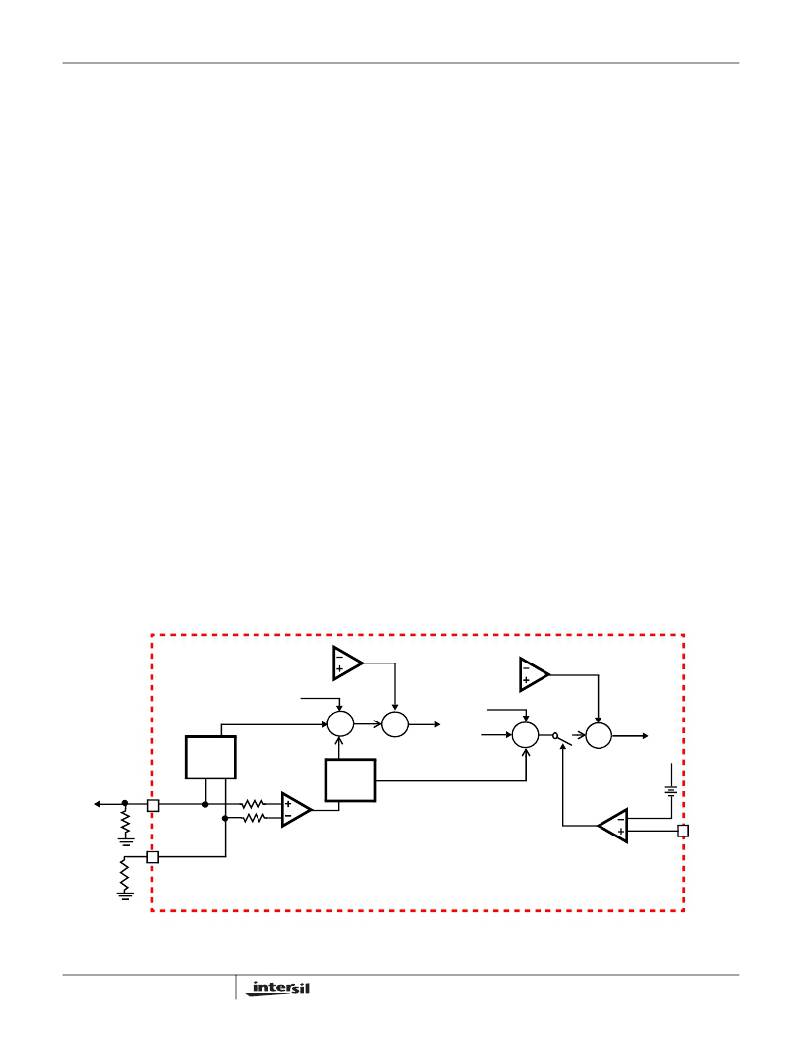

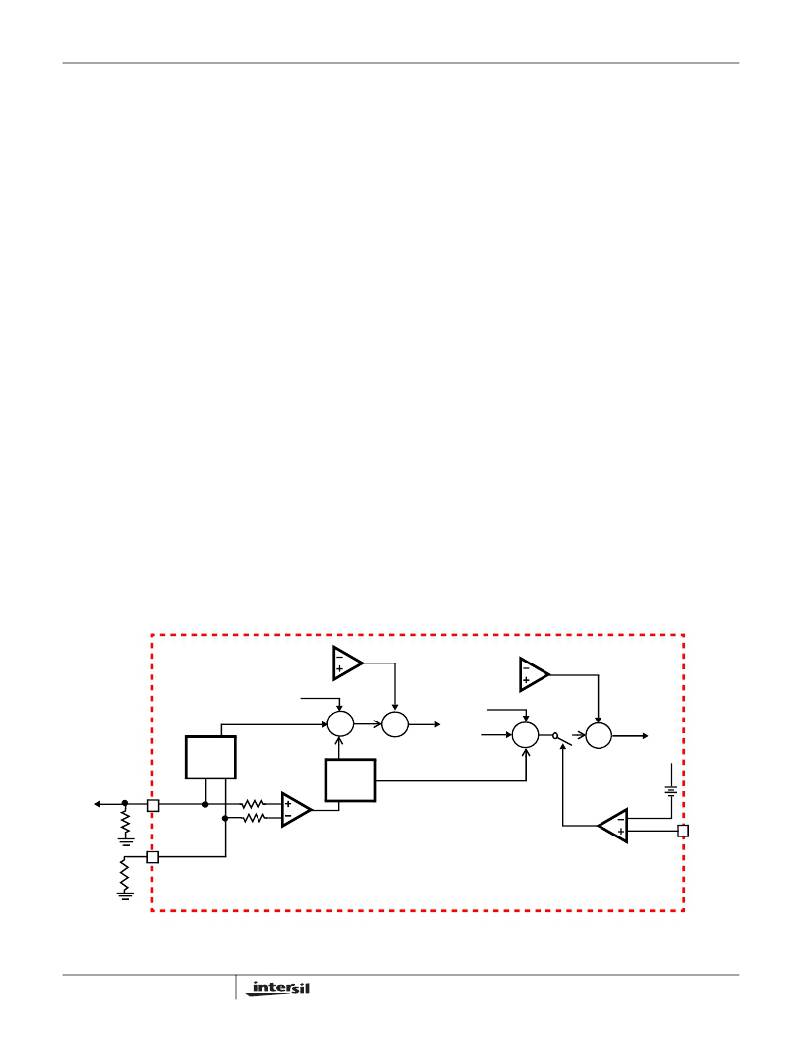

�Figure� 13� shows� a� simple� and� flexible� configuration� for� both�

�r� DS(ON)� and� DCR� sensing.�

�Current� Share� Control� in� Multiphase� Single� Output�

�The� I� AVG_CS� is� the� average� current� of� both� channels� (I� AVG,�

�2-phase� mode)� or� only� Channel� 1� (I� CS1,� any� other� modes).�

�ISHARE� and� ISET� pins� source� a� copy� of� I� AVG_CS� with� 15μA�

�offset,� for� example,� the� full-scale� will� be� 123μA.� If� one� single�

�external� resistor� is� used� as� R� ISHARE� connecting� the�

�ISHARE� bus� to� ground� for� all� the� ICs� in� parallel,� R� ISHARE�

�should� be� set� equal� to� R� ISET� /N� CTRL� (where� N� CNTL� is� the�

�number� of� the� ISL8120� controllers� in� parallel� or� multiphase�

�operations),� and� the� share� bus� voltage� (V� ISHARE� )� set� by� the�

�R� ISHARE� represents� the� average� current� of� all� active�

�channels.� Another� way� to� set� R� ISHARE� is� to� put� one� resistor�

�in� each� IC’� s� ISHARE� pin� and� use� the� same� value� with�

�R� ISET� (� R� ISHARE� =� R� ISET� ),� in� which� case� the� total�

�equivalent� resistance� value� is� also� R� ISET� /N� CTRL� .� The�

�voltage� (V� ISET� )� set� by� R� ISET� represents� the� average� current�

�of� the� corresponding� device� and� compared� with� the� share�

�bus� (V� ISHARE� ).� The� current� share� error� signal� (I� CSH_ERR� )� is�

�then� fed� into� the� current� correction� block� to� adjust� each�

�channel’s� PWM� pulse� accordingly.�

�The� current� share� function� provides� at� least� 10%� overall�

�accuracy� between� ICs,� 5%� within� the� IC� when� using� a� 1%�

�resistor� to� sense� a� 10mV� signal.� The� current� share� bus�

�works� for� up� to� 12-phase.�

�ERROR�

�AMP� 2�

�I� CS1�

�+�

�-� ∑�

�-�

�CURRENT�

�MIRROR�

�BLOCK�

�I� AVG_CS�

�-�

�∑�

�I� CSH_ERR�

�CURRENT�

�+�

�V� ERROR1� I� CS2�

�I� AVG_CS�

�I� CSH_ERR�

�-�

�-�

�∑�

�+�

�+�

�-� ∑�

�V� ERROR2�

�VCC�

�MIRROR�

�SHARE� BUS�

�R� ISHARE�

�ISHARE�

�ISET�

�BLOCK�

�I� AVG� =� (I� CS1� +� I� CS2� )� /� 2�

�I� AVG_CS� =� I� AVG� or� I� CS1�

�700mV�

�VSEN2-�

�I� DROOP� +� 15μA� =� I� AVG_CS� +� 15μA� =� ISET� =� ISHARE�

�R� ISET�

�R� ISHARE� =R� ISET� /N� CTRL�

�FIGURE� 14.� SIMPLIFIED� CURRENT� SHARE� AND� INTERNAL� BALANCE� IMPLEMENTATION�

�27�

�March� 20,� 2009�

�FN6641.0�

�相关PDF资料 |

PDF描述 |

|---|---|

| CAT1026YI-42-GT3 | IC SUPERVISOR CPU 2K EEPR 8TSSOP |

| ISL6401CRZ | IC REG CTRLR BST FLYBK ISO 16QFN |

| CAT1026YI-30-GT3 | IC SUPERVISOR CPU 2K EEPR 8TSSOP |

| ISL6740IVZ | IC REG CTRLR PWM VM 16-TSSOP |

| B41043A3228M | 2200UF 10V 12.5X25 SINGLE END |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL8120CRZ-TS2568 | 制造商:Intersil Corporation 功能描述:INTEL, ISL8120CRZ-T W/BARCODE LABELS, 12 MONTH D/C RESTRICTI - Tape and Reel |

| ISL8120EVAL3Z | 功能描述:EVALUATION BOARD FOR ISL8120 RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL8120EVAL4Z | 功能描述:BOARD EVALUATION FOR ISL8120 RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL8120IRZ | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8120IRZEC | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。