参数资料

| 型号: | ISL90726WIE627Z-TK |

| 厂商: | Intersil |

| 文件页数: | 4/8页 |

| 文件大小: | 0K |

| 描述: | IC POT DGTL 10K OHM SC70-6 |

| 产品培训模块: | Digitally Controlled Potentiometers Solutions for Industrial Control Applications |

| 标准包装: | 1 |

| 系列: | XDCP™ |

| 接片: | 128 |

| 电阻(欧姆): | 10k |

| 电路数: | 1 |

| 温度系数: | 标准值 ±45 ppm/°C |

| 存储器类型: | 易失 |

| 接口: | I²C |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 6-TSSOP,SC-88,SOT-363 |

| 供应商设备封装: | SC-70-6 |

| 包装: | 标准包装 |

| 产品目录页面: | 1237 (CN2011-ZH PDF) |

| 其它名称: | ISL90726WIE627Z-TKDKR |

4

FN8244.4

August 26, 2008

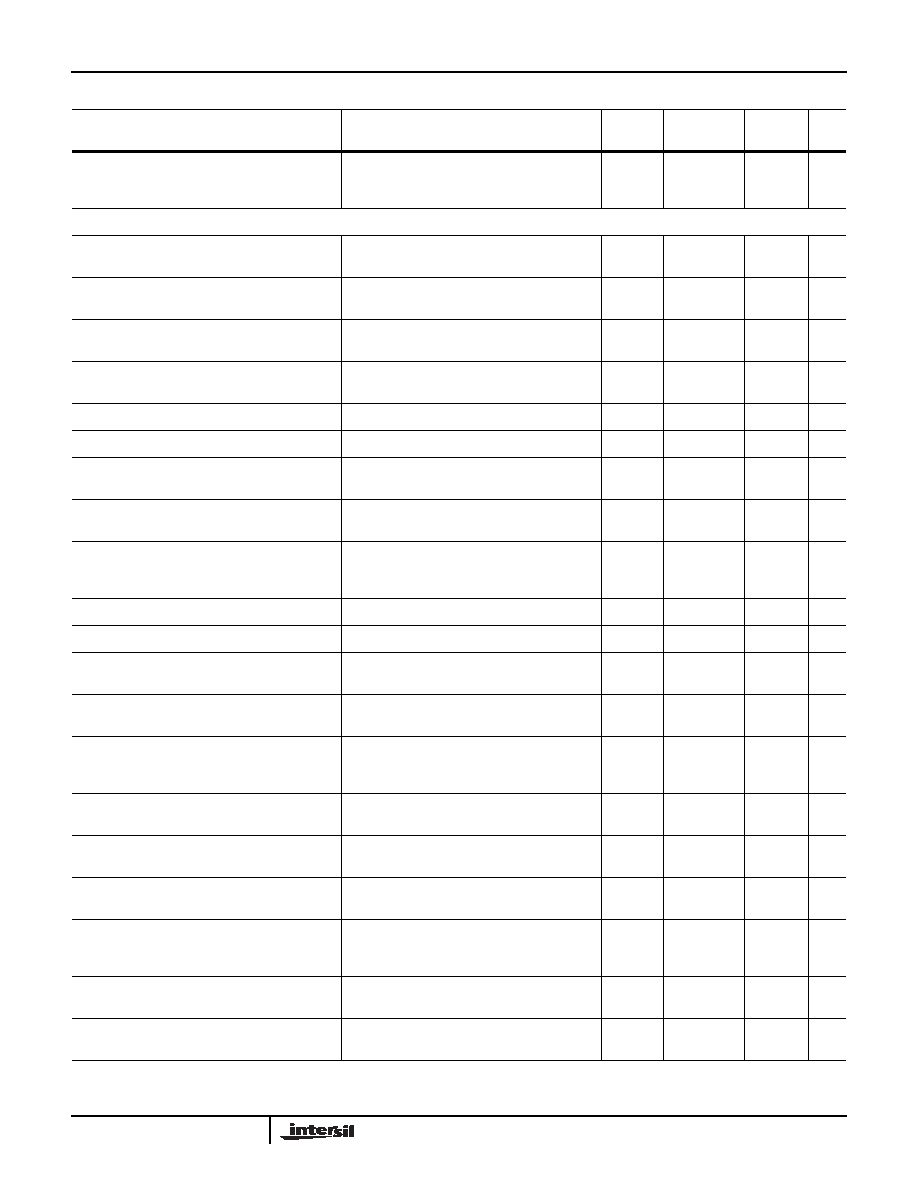

tD

Power-up Delay

VCC above VPOR, to DCP Initial Value Register

recall completed, and I2C Interface in standby

state

3ms

SERIAL INTERFACE SPECIFICATIONS

SDA, and SCL Input Buffer LOW

Voltage

-0.3

0.3*VCC

V

HIGH Voltage

0.7*VCC

VCC + 0.3

V

Hysteresis

SDA and SCL Input Buffer

Hysteresis

0.05*VCC

V

VOL

SDA Output Buffer LOW

Voltage, Sinking 4mA

00.4

V

Cpin (Note 9)

SDA, and SCL Pin Capacitance

10

pF

fSCL

SCL Frequency

400

kHz

tIN

Pulse Width Suppression Time

at SDA and SCL Inputs

Any pulse narrower than the max spec is

suppressed.

50

ns

tAA

SCL Falling Edge to SDA Output

Data Valid

SCL falling edge crossing 30% of VCC, until

SDA exits the 30% to 70% of VCC window.

900

ns

tBUF

Time the Bus Must be Free

Before the Start of a New

Transmission

SDA crossing 70% of VCC during a STOP

condition, to SDA crossing 70% of VCC during

the following START condition.

1300

ns

tLOW

Clock LOW Time

Measured at the 30% of VCC crossing.

1300

ns

tHIGH

Clock HIGH Time

Measured at the 70% of VCC crossing.

600

ns

tSU:STA

START Condition Setup Time

SCL rising edge to SDA falling edge. Both

crossing 70% of VCC.

600

ns

tHD:STA

START Condition Hold Time

From SDA falling edge crossing 30% of VCC to

SCL falling edge crossing 70% of VCC.

600

ns

tSU:DAT

Input Data Setup Time

From SDA exiting the 30% to 70% of VCC

window, to SCL rising edge crossing 30% of

VCC

100

ns

tHD:DAT

Input Data Hold Time

From SCL rising edge crossing 70% of VCC to

SDA entering the 30% to 70% of VCC window.

0ns

tSU:STO

STOP Condition Setup Time

From SCL rising edge crossing 70% of VCC, to

SDA rising edge crossing 30% of VCC.

600

ns

tHD:STO

STOP Condition Hold Time for

Read, or Volatile Only Write

From SDA rising edge to SCL falling edge. Both

crossing 70% of VCC.

600

ns

tDH

Output Data Hold Time

From SCL falling edge crossing 30% of VCC,

until SDA enters the 30% to 70% of VCC

window.

0ns

SDA and SCL Rise Time

From 30% to 70% of VCC

20 +

0.1*Cb

250

ns

SDA and SCL Fall Time

From 70% to 30% of VCC

20 +

0.1*Cb

250

ns

Operating Specifications

(Continued)

SYMBOL

PARAMETER

TEST CONDITIONS

MIN

(Note 12)

TYP

(Note 2)

MAX

(Note 12) UNIT

ISL90726

相关PDF资料 |

PDF描述 |

|---|---|

| MS27656E17B6P | CONN RCPT 6POS WALL MNT W/PINS |

| VI-23L-MY-F1 | CONVERTER MOD DC/DC 28V 50W |

| VI-23K-MY-F4 | CONVERTER MOD DC/DC 40V 50W |

| VI-23K-MY-F2 | CONVERTER MOD DC/DC 40V 50W |

| MS3100A36-7P | CONN RCPT 47POS WALL MNT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL90726WIE6Z | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Digitally Controlled Potentiometer (XDCP) |

| ISL90726WIE6Z-TK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Digitally Controlled Potentiometer (XDCP) |

| ISL90727 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Digitally Controlled Potentiometer XDCP |

| ISL90727_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Digitally Controlled Potentiometer |

| ISL90727UIE627Z | 功能描述:IC XDCP 128-TAP 50KOHM SC70-6 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:XDCP™ 标准包装:2,500 系列:XDCP™ 接片:256 电阻(欧姆):100k 电路数:1 温度系数:标准值 ±300 ppm/°C 存储器类型:非易失 接口:I²C(设备位址) 电源电压:2.7 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:14-TSSOP(0.173",4.40mm 宽) 供应商设备封装:14-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。