- 您现在的位置:买卖IC网 > PDF目录16549 > KSZ8031RNL-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ8031RNL PDF资料下载

参数资料

| 型号: | KSZ8031RNL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 11/43页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR KSZ8031RNL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网 PHY |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8031RNL |

| 已供物品: | 板 |

| 相关产品: | 576-3843-6-ND - TXRX PHY 100BASE TX 3.3V 24QFN 576-3843-1-ND - TXRX PHY 100BASE TX 3.3V 24QFN 576-3788-ND - TXRX PHY 10/100 3.3V 24-QFN 576-3843-2-ND - TXRX PHY 100BASE TX 3.3V 24QFN 576-3741-5-ND - TXRX PHY 100BASE TX 3.3V 24QFN |

| 其它名称: | 576-3862 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

Micrel, Inc.

KSZ8021RNL / KSZ8031RNL

August 2010

19

M9999-082710-1.0

MII Management (MIIM) Interface

The KSZ8021/31RNL supports the IEEE 802.3 MII Management Interface, also known as the Management Data Input /

Output (MDIO) Interface. This interface enables upper-layer device, like a MAC processor, to monitor and control the state

of the KSZ8021/31RNL. An external device with MIIM capability is used to read the PHY status and/or configure the PHY

settings. Further details on the MIIM interface can be found in Clause 22.2.4 of the IEEE 802.3 Specification.

The MIIM interface consists of the following:

A physical connection that incorporates the clock line (MDC) and the data line (MDIO).

A specific protocol that operates across the aforementioned physical connection that allows the external controller

to communicate with one or more PHY devices.

A set of 16-bit MDIO registers. Registers [0:8] are standard registers, and their functions are defined per the IEEE

802.3 Specification. The additional registers are provided for expanded functionality. See “Register Map” section

for details.

The KSZ8021/31RNL supports only two unique PHY addresses, 0x0h and 0x3h. The PHYAD[1:0] strapping pin is used to

select either 0x0h or 0x3h as the unique PHY address for the KSZ8021/31RNL device.

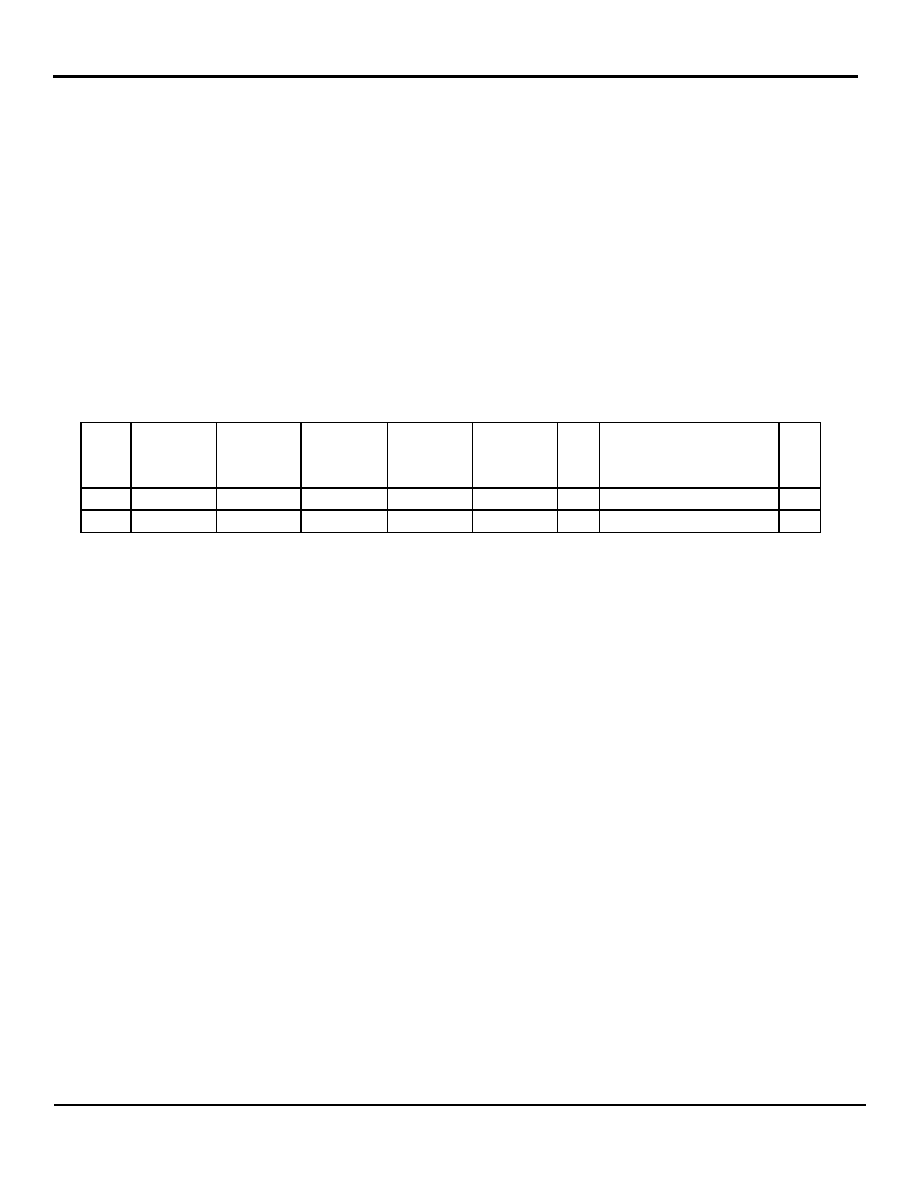

Table 3 shows the MII Management frame format for the KSZ8021/31RNL.

Preamble

Start of

Frame

Read/Write

OP Code

PHY

Address

Bits [4:0]

REG

Address

Bits [4:0]

TA

Data

Bits [15:0]

Idle

Read

32 1’s

01

10

000AA

RRRRR

Z0

DDDDDDDD_DDDDDDDD

Z

Write

32 1’s

01

000AA

RRRRR

10

DDDDDDDD_DDDDDDDD

Z

Table 3. MII Management Frame Format – for KSZ8021/31RNL

Interrupt (INTRP)

The INTRP (pin 18) is an optional interrupt signal that is used to inform the external controller that there has been a status

update to the KSZ8021/31RNL PHY register. Register 1Bh, bits [15:8] are the interrupt control bits to enable and disable

the conditions for asserting the INTRP signal. Register 1Bh, bits [7:0] are the interrupt status bits to indicate which

interrupt conditions have occurred. The interrupt status bits are cleared after reading register 1Bh.

Register 1Fh, bit 9 sets the interrupt level to active high or active low. The default is active low.

The MII management bus option gives the MAC processor complete access to the KSZ8021/31RNL control and status

registers. Additionally, an interrupt pin eliminates the need for the processor to poll the PHY for status change.

HP Auto MDI/MDI-X

The HP Auto MDI/MDI-X configuration eliminates the confusion of whether to use a straight cable or a crossover cable

between the KSZ8021/31RNL and its link partner. This feature allows the KSZ8021/31RNL to use either type of cable to

connect with a link partner that is in either MDI or MDI-X mode. The auto-sense function detects transmit and receive

pairs from the link partner, and then assigns transmit and receive pairs of the KSZ8021/31RNL accordingly.

HP Auto MDI/MDI-X is enabled by default. It is disabled by writing a one to register 1Fh, bit [13]. MDI and MDI-X mode is

selected by register 1Fh, bit [14] if HP Auto MDI/MDI-X is disabled.

An isolation transformer with symmetrical transmit and receive data paths is recommended to support auto MDI/MDI-X.

The IEEE 802.3 Standard defines MDI and MDI-X in Table 4.

相关PDF资料 |

PDF描述 |

|---|---|

| HBM10DRTF | CONN EDGECARD 20POS DIP .156 SLD |

| H3BKH-5006G | IDC CABLE - HSR50H/AE50G/HPK50H |

| GCM25DTKN | CONN EDGECARD 50POS DIP .156 SLD |

| ESC10DRYI-S13 | CONN EDGECARD 20POS .100 EXTEND |

| GCM25DTKH | CONN EDGECARD 50POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8031RNLI | 功能描述:TXRX PHY 10/100 3.3V 24-QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8031RNLI TR | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ RMII Support (24-QFN, Industrial Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8031RNLITR | 制造商:Micrel Inc 功能描述:Ethernet transceiver,PHY,RMII,QFN24 |

| KSZ8031RNLI-TR | 功能描述:1/1 Transceiver Full RMII 24-QFN (4x4) 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:过期 类型:收发器 协议:RMII 驱动器/接收器数:1/1 双工:全 接收器滞后:- 数据速率:- 电压 - 电源:1.8V,2.5V,3.3V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商器件封装:24-QFN(4x4) 标准包装:1 |

| KSZ8031RNL-TR | 功能描述:1/1 Transceiver Full RMII 24-QFN (4x4) 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:过期 类型:收发器 协议:RMII 驱动器/接收器数:1/1 双工:全 接收器滞后:- 数据速率:- 电压 - 电源:1.8V,2.5V,3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商器件封装:24-QFN(4x4) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。