- 您现在的位置:买卖IC网 > PDF目录16860 > KSZ8051MLL-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ8051MLL PDF资料下载

参数资料

| 型号: | KSZ8051MLL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 13/48页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR KSZ8051MLL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网 PHY |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8051MLL |

| 已供物品: | 板 |

| 相关产品: | 576-3888-6-ND - TXRX PHY 10/T100 3.3V MII 48LQFP 576-3888-1-ND - TXRX PHY 10/T100 3.3V MII 48LQFP 576-3888-2-ND - TXRX PHY 10/T100 3.3V MII 48LQFP KSZ8051MLL TR-ND - TXRX PHY 10/T100 3.3V MII 48LQFP 576-3731-ND - TXRX PHY 10/T100 3.3V MII 48LQFP |

| 其它名称: | 576-3864 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Micrel, Inc.

KSZ8051MLL

July 2010

20

M9999-071210-1.0

MII Management (MIIM) Interface

The KSZ8051MLL supports the IEEE 802.3 MII Management Interface, also known as the Management Data Input /

Output (MDIO) Interface. This interface enables upper-layer device, like a MAC processor, to monitor and control the state

of the KSZ8051MLL. An external device with MIIM capability is used to read the PHY status and/or configure the PHY

settings. Further details on the MIIM interface can be found in Clause 22.2.4 of the IEEE 802.3 Specification.

The MIIM interface consists of the following:

A physical connection that incorporates the clock line (MDC) and the data line (MDIO).

A specific protocol that operates across the aforementioned physical connection that allows the external controller

to communicate with one or more PHY devices.

A set of 16-bit MDIO registers. Registers [0:8] are standard registers, and their functions are defined per the IEEE

802.3 Specification. The additional registers are provided for expanded functionality. See “Register Map” section

for details.

As the default, the KSZ8051MLL supports unique PHY addresses 1 to 7, and broadcast PHY address 0. The latter is

defined per the IEEE 802.3 Specification, and can be used to read/write to a single KSZ8051MLL device, or write to

multiple KSZ8051MLL devices simultaneously.

Optionally, PHY address 0 can be disabled as the broadcast address by either hardware pin strapping (B-CAST_OFF, pin

28) or software (register 16h, bit 9), and assigned as a unique PHY address.

The PHYAD[2:0] strapping pins are used to assign a unique PHY address between 0 and 7 to each KSZ8051MLL device.

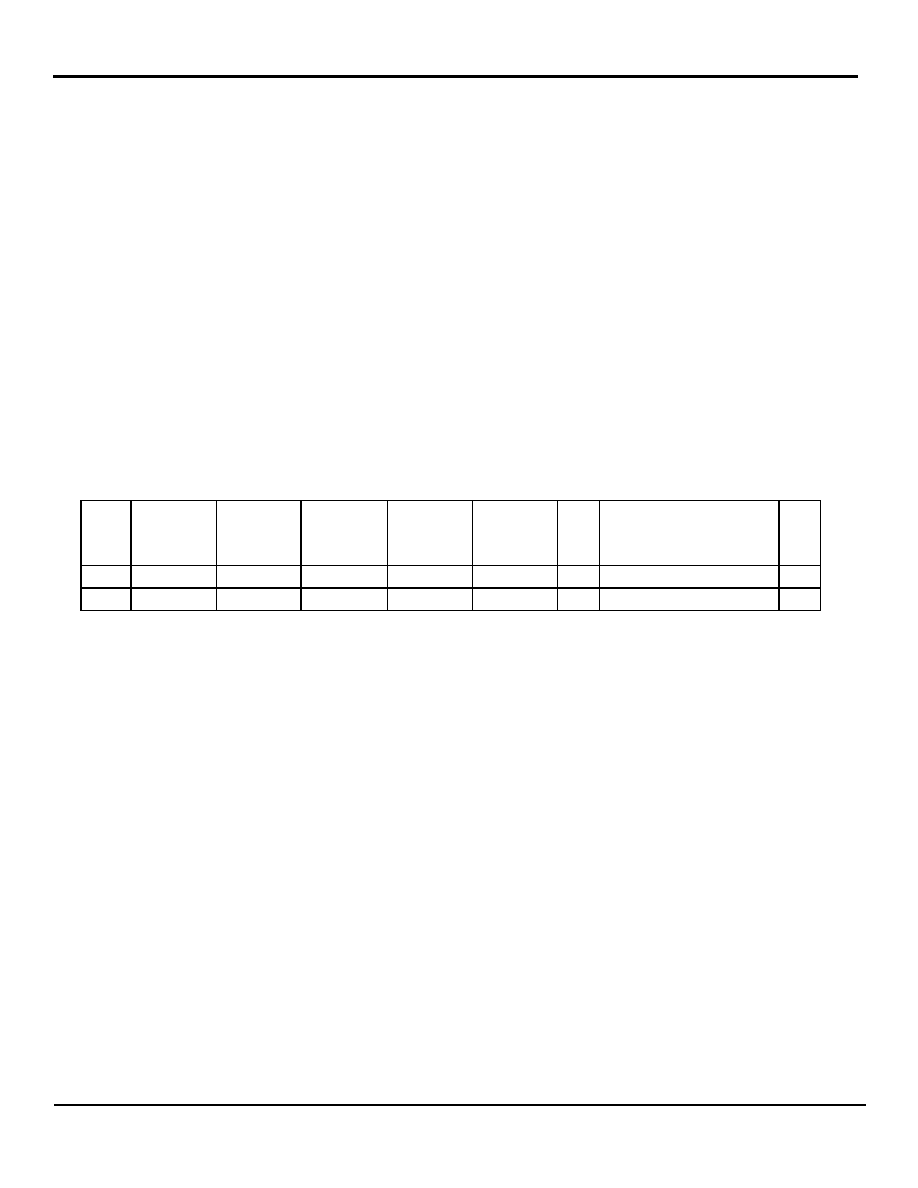

Table 3 shows the MII Management frame format for the KSZ8051MLL.

Preamble

Start of

Frame

Read/Write

OP Code

PHY

Address

Bits [4:0]

REG

Address

Bits [4:0]

TA

Data

Bits [15:0]

Idle

Read

32 1’s

01

10

00AAA

RRRRR

Z0

DDDDDDDD_DDDDDDDD

Z

Write

32 1’s

01

00AAA

RRRRR

10

DDDDDDDD_DDDDDDDD

Z

Table 3. MII Management Frame Format – for KSZ8051MLL

Interrupt (INTRP)

INTRP (pin 32) is an optional interrupt signal that is used to inform the external controller that there has been a status

update to the KSZ8051MLL PHY register. Register 1Bh, bits [15:8] are the interrupt control bits to enable and disable the

conditions for asserting the INTRP signal. Register 1Bh, bits [7:0] are the interrupt status bits to indicate which interrupt

conditions have occurred. The interrupt status bits are cleared after reading register 1Bh.

Register 1Fh, bit 9 sets the interrupt level to active high or active low. The default is active low.

The MII management bus option gives the MAC processor complete access to the KSZ8051MLL control and status

registers. Additionally, an interrupt pin eliminates the need for the processor to poll the PHY for status change.

相关PDF资料 |

PDF描述 |

|---|---|

| MLG0603S2N7S | INDUCTOR MULTILAYER 2.7NH 0201 |

| EV-ADF4002SD1Z | BOARD EVAL FOR ADF4002 |

| EVAL-AD7280AEDZ | BOARD EVAL FOR AD7280 |

| V110C24C100B3 | CONVERTER MOD DC/DC 24V 100W |

| MLG0603S2N0S | INDUCTOR MULTILAYER 2.0NH 0201 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8051MLLI | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ MII Support (48-LQFP, Industrial Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8051MLLI TR | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ MII Support (48-LQFP, Industrial Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8051MLLI-TR | 功能描述:1/1 Transceiver Full MII 48-LQFP (7x7) 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:过期 类型:收发器 协议:MII 驱动器/接收器数:1/1 双工:全 接收器滞后:- 数据速率:- 电压 - 电源:1.8V,2.5V,3.3V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商器件封装:48-LQFP(7x7) 标准包装:1 |

| KSZ8051MNL | 功能描述:TXRX PHY 10/T100 3.3V MII 32-QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8051MNL TR | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ MII Support (32-QFN) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。