- 您现在的位置:买卖IC网 > PDF目录16860 > KSZ8051MLL-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ8051MLL PDF资料下载

参数资料

| 型号: | KSZ8051MLL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 2/48页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR KSZ8051MLL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网 PHY |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8051MLL |

| 已供物品: | 板 |

| 相关产品: | 576-3888-6-ND - TXRX PHY 10/T100 3.3V MII 48LQFP 576-3888-1-ND - TXRX PHY 10/T100 3.3V MII 48LQFP 576-3888-2-ND - TXRX PHY 10/T100 3.3V MII 48LQFP KSZ8051MLL TR-ND - TXRX PHY 10/T100 3.3V MII 48LQFP 576-3731-ND - TXRX PHY 10/T100 3.3V MII 48LQFP |

| 其它名称: | 576-3864 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Micrel, Inc.

KSZ8051MLL

July 2010

10

M9999-071210-1.0

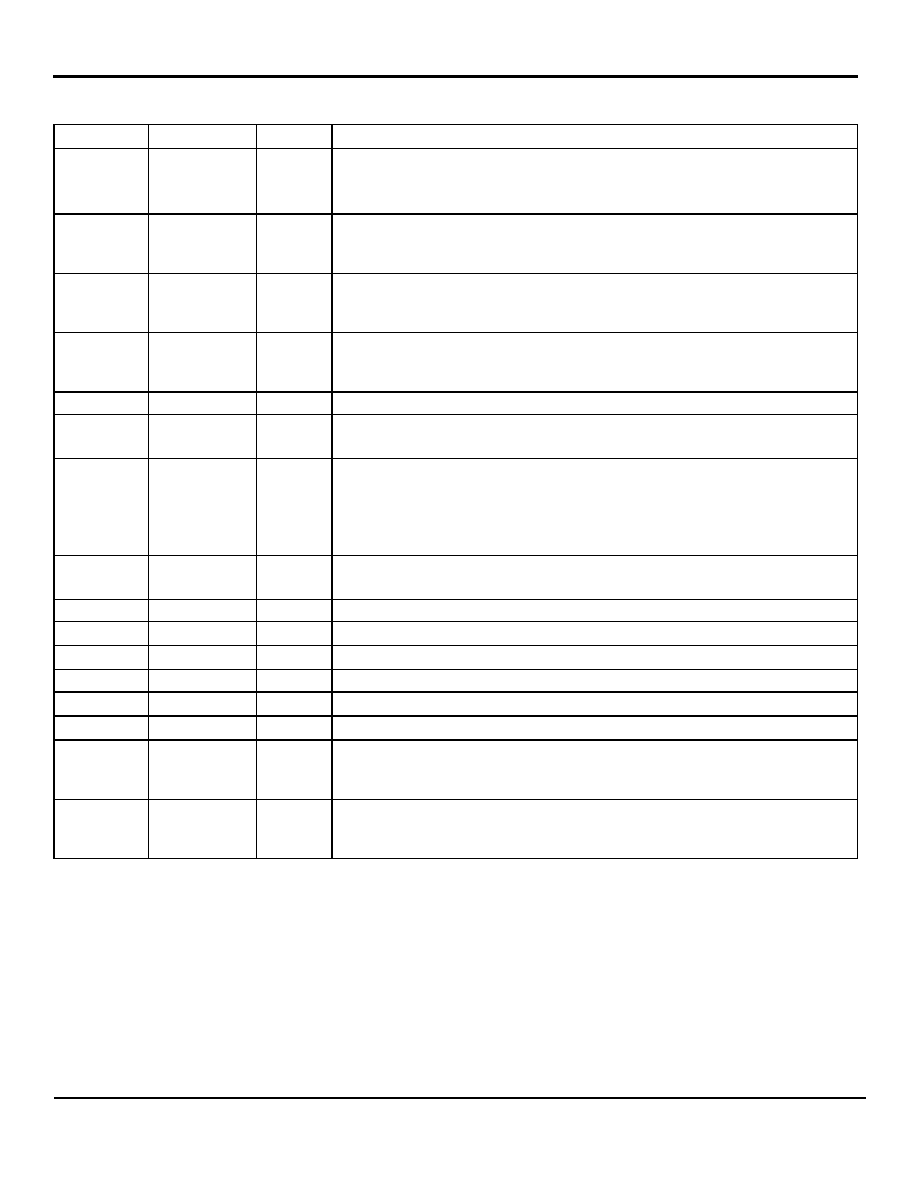

Pin Description – KSZ8051MLL (Continued)

Pin Number

Pin Name

Type

(1)

Pin Function

26

NC

-

No connect

27

RXDV /

CONFIG2

Ipd/O

MII Mode:

MII Receive Data Valid Output /

Config Mode:

The pull-up/pull-down value is latched as CONFIG2 at the

de-assertion of reset. See Strapping Options section for details.

28

RXC /

B-CAST_OFF

Ipd/O

MII Mode:

MII Receive Clock Output

Config Mode:

The pull-up/pull-down value is latched as B-CAST_OFF at the

de-assertion of reset. See Strapping Options section for details.

29

RXER /

ISO

Ipd/O

MII Mode:

MII Receive Error Output /

Config Mode:

The pull-up/pull-down value is latched as ISOLATE at the

de-assertion of reset. See Strapping Options section for details.

30

GND

Gnd

Ground

31

VDD_1.2

P

1.2V core VDD

(power supplied by KSZ8051MLL)

Decouple with 0.1uF capacitor to ground, and join with pin 4 by power trace or plane.

32

INTRP /

NAND_Tree#

Ipu/Opu

Interrupt Output: Programmable Interrupt Output

This pin has a weak pull-up, is open-drain like, and requires an external 1.0K

Ω

pull-up resistor.

Config Mode:

The pull-up/pull-down value is latched as NAND Tree# at the

de-assertion of reset. See Strapping Options section for details.

33

TXC

I/O

MII Mode:

MII Transmit Clock Output

MII Back-to-Back Mode:

MII Transmit Clock Input

34

TXEN

I

MII Mode:

MII Transmit Enable Input

35

TXD0

I

MII Mode:

MII Transmit Data Input[0]

(3)

36

TXD1

I

MII Mode:

MII Transmit Data Input[1]

(3)

37

GND

Gnd

Ground

38

TXD2

I

MII Mode:

MII Transmit Data Input[2]

(3)

39

TXD3

I

MII Mode:

MII Transmit Data Input[3]

(3)

40

COL /

CONFIG0

Ipd/O

MII Mode:

MII Collision Detect Output /

Config Mode:

The pull-up/pull-down value is latched as CONFIG0 at the

de-assertion of reset. See Strapping Options section for details.

41

CRS /

CONFIG1

Ipd/O

MII Mode:

MII Carrier Sense Output /

Config Mode:

The pull-up/pull-down value is latched as CONFIG1 at the

de-assertion of reset. See Strapping Options section for details.

相关PDF资料 |

PDF描述 |

|---|---|

| MLG0603S2N7S | INDUCTOR MULTILAYER 2.7NH 0201 |

| EV-ADF4002SD1Z | BOARD EVAL FOR ADF4002 |

| EVAL-AD7280AEDZ | BOARD EVAL FOR AD7280 |

| V110C24C100B3 | CONVERTER MOD DC/DC 24V 100W |

| MLG0603S2N0S | INDUCTOR MULTILAYER 2.0NH 0201 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8051MLLI | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ MII Support (48-LQFP, Industrial Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8051MLLI TR | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ MII Support (48-LQFP, Industrial Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8051MLLI-TR | 功能描述:1/1 Transceiver Full MII 48-LQFP (7x7) 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:过期 类型:收发器 协议:MII 驱动器/接收器数:1/1 双工:全 接收器滞后:- 数据速率:- 电压 - 电源:1.8V,2.5V,3.3V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商器件封装:48-LQFP(7x7) 标准包装:1 |

| KSZ8051MNL | 功能描述:TXRX PHY 10/T100 3.3V MII 32-QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KSZ8051MNL TR | 功能描述:以太网 IC 3.3V, 10Base-T/100Base-TX Physical Layer Transceiver w/ MII Support (32-QFN) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。