- 您现在的位置:买卖IC网 > PDF目录80297 > LC72121 PLL FREQUENCY SYNTHESIZER, 160 MHz, PDIP22 PDF资料下载

参数资料

| 型号: | LC72121 |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDIP22 |

| 封装: | DIP-22 |

| 文件页数: | 19/23页 |

| 文件大小: | 377K |

| 代理商: | LC72121 |

No. 5815-5/23

LC72121, 72121M, 72121V

Parameter

Symbol

Conditions

Ratings

Unit

min

typ

max

VOL1

PD: IO = 1 mA

1.0

V

VOL2

BO1 to BO4, IO1, IO2: IO = 1 mA

0.2

V

Output low-level voltage

BO1 to BO4, IO1, IO2: IO = 8 mA

1.6

V

VOL3

DO: IO = 1 mA

0.2

V

DO: IO = 5 mA

1.0

V

VOL4

AOUT: IO = 1 mA, AIN = 1.3 V

0.5

V

IIH1

CE, DI, CL: VI = 6.5 V

5.0

A

IIH2

IO1, IO2: VI = 13 V

5.0

A

Input high-level current

IIH3

XIN: VI = VDD

1.3

8

A

IIH4

FMIN, AMIN: VI = VDD

2.5

15

A

IIH5

IFIN: VI = VDD

5.0

30

A

IIH6

AIN: VI = 6.5 V

200

nA

IIL1

CE, DI, CL: VI = 0 V

5.0

A

IIL2

IO1, IO2: VI = 0 V

5.0

A

Input low-level current

IIL3

XIN: VI = 0 V

1.3

8

A

IIL4

FMIN, AMIN: VI = 0 V

2.5

15

A

IIL5

IFIN: VI = 0 V

5.0

30

A

IIL6

AIN: VI = 0 V

200

nA

Output off leakage current

IOFF1

BO1 to BO4, IO1, IO2, AOUT: VO = 13 V

5.0

A

IOFF2

DO: VO = 6.5 V

5.0

A

High-level 3-state off leakage current

IOFFH

PD: VO = VDD

0.01

200

nA

Low-level 3-state off leakage current

IOFFL

PD: VO = 0 V

0.01

200

nA

Input capacitance

CIN

FMIN

6

pF

IDD1

VDD: Xtal = 7.2 MHz, fIN2 = 130 MHz,

2.5

6

mA

VIN2 = 20 mVrms

Supply current

VDD: PLL block stopped (PLL inhibit mode)

IDD2

Crystal oscillator operating

0.3

mA

(crystal frequency: 7.2 MHz)

IDD3

VDD: PLL block stopped, crystal oscillator

10

A

stopped

Continued from preceding page.

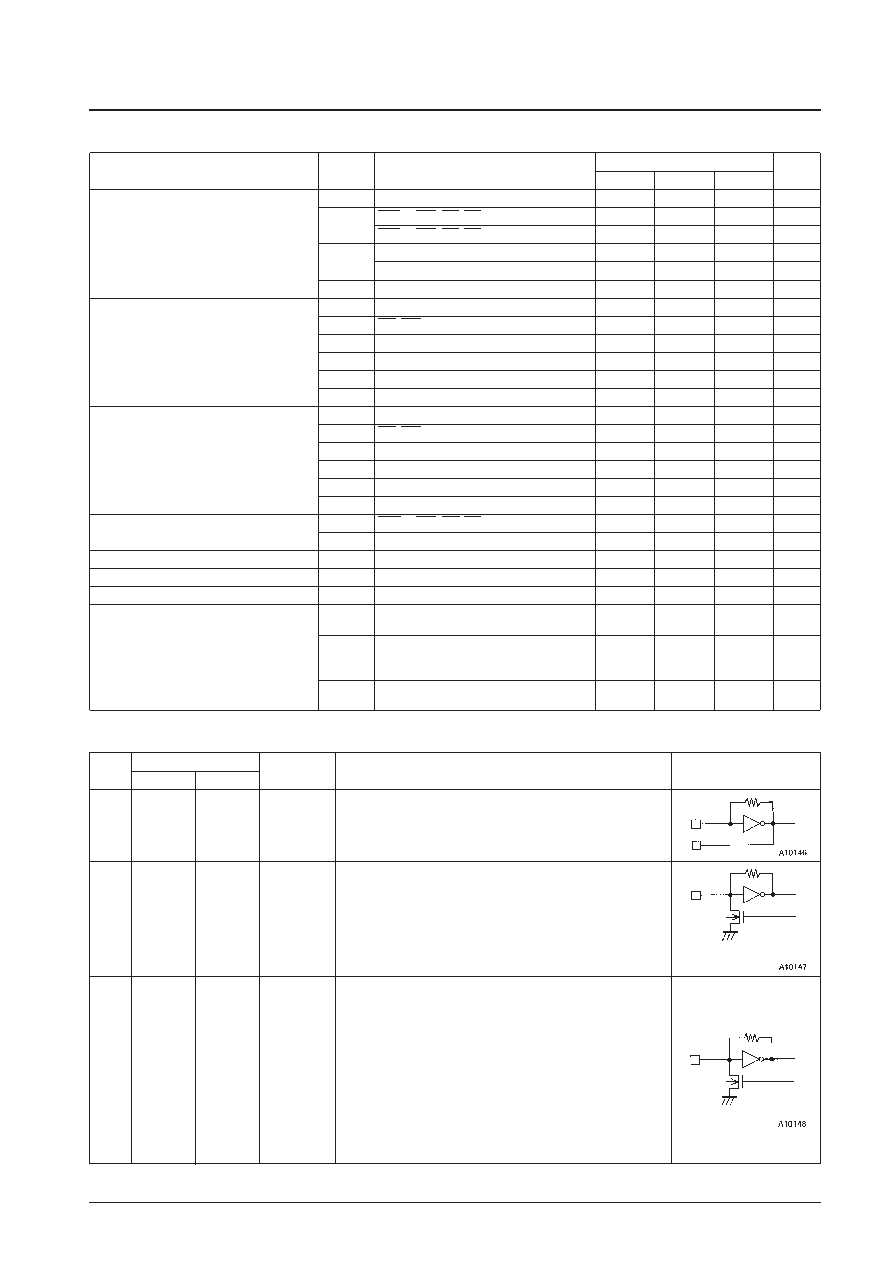

Pin Descriptions

Pin

Pin No.

Type

Function

Equivalent circuit

name

LC72121

Xtal

Crystal oscillator element connections (4.5 or 7.2 MHz)

XIN

XOUT

1

22

1

24

LC72121M

LC72121V

Local

oscillator

signal input

FMIN is selected when DVS in the serial data is set to 1.

Input frequency: 10 to 160 MHz

The signal is passed through an internal divide-by-two prescaler and

then input to the swallow counter.

The divisor can be set to a value in the range 272 to 65535. Since

the internal divide-by-two prescaler is used, the actual divisor will be

twice the set value.

FMIN

16

17

Local

oscillator

signal input

AMIN is selected when DVS in the serial data is set to 0.

When SNS in the serial data is set to 1:

Input frequency: 2 to 40 MHz

The signal is input to the swallow counter directly.

The divisor can be set to a value in the range 272 to 65535. The

set value becomes the actual divisor.

When SNS in the serial data is set to 0:

Input frequency: 0.5 to 10 MHz

The signal is input to a 12-bit programmable divider directly.

The divisor can be set to a value in the range 4 to 4095. The set

value becomes the actual divisor.

AMIN

15

16

Continued on next page.

相关PDF资料 |

PDF描述 |

|---|---|

| LTC6909HMS#TRPBF | SPECIALTY ANALOG CIRCUIT, PDSO16 |

| LSM-1.5/10-D5 | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| LS4601-9RD5T | 1-OUTPUT 100 W AC-DC PWR FACTOR CORR MODULE |

| LS4601-9RD5TB1 | 1-OUTPUT 100 W AC-DC PWR FACTOR CORR MODULE |

| LH0070-0H#PBF | 1-OUTPUT THREE TERM VOLTAGE REFERENCE, 10 V, MBCY3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC72121_03 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers for Electronic Tuning |

| LC72121-D-E | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Ammo Pack 制造商:ON Semiconductor 功能描述:PLL FREQ SYNTHESIZER 制造商:ON Semiconductor 功能描述:FNFLD / PLL FREQUENCY SYNTHESIZER |

| LC72121M | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers for Electronic Tuning |

| LC72121MA | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:CMOS IC PLL Frequency Synthesizers for Electronic Tuning |

| LC72121MA-AH | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。