- 您现在的位置:买卖IC网 > PDF目录80205 > LC72121V PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 PDF资料下载

参数资料

| 型号: | LC72121V |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 |

| 封装: | SSOP-24 |

| 文件页数: | 2/23页 |

| 文件大小: | 377K |

| 代理商: | LC72121V |

No.

Control block/data

Function

Related data

No. 5815-10/23

LC72121, 72121M, 72121V

Continued from preceding page.

4

I/O port setup data

IOC1,IOC2

Specifies input or output for the shared function I/O pins (IO1 and IO2).

Data = 0: Input port

Data = 1: Output port

5

Output port data

BO1 to BO4

IO1,IO2

Determines the output state of the BO1 through BO4, IO1, and IO2 output ports.

Data = 0: Open

Data = 1: Low level

The data is reset to 0, setting the pins to the open state, after a power on reset.

IOC1

IOC2

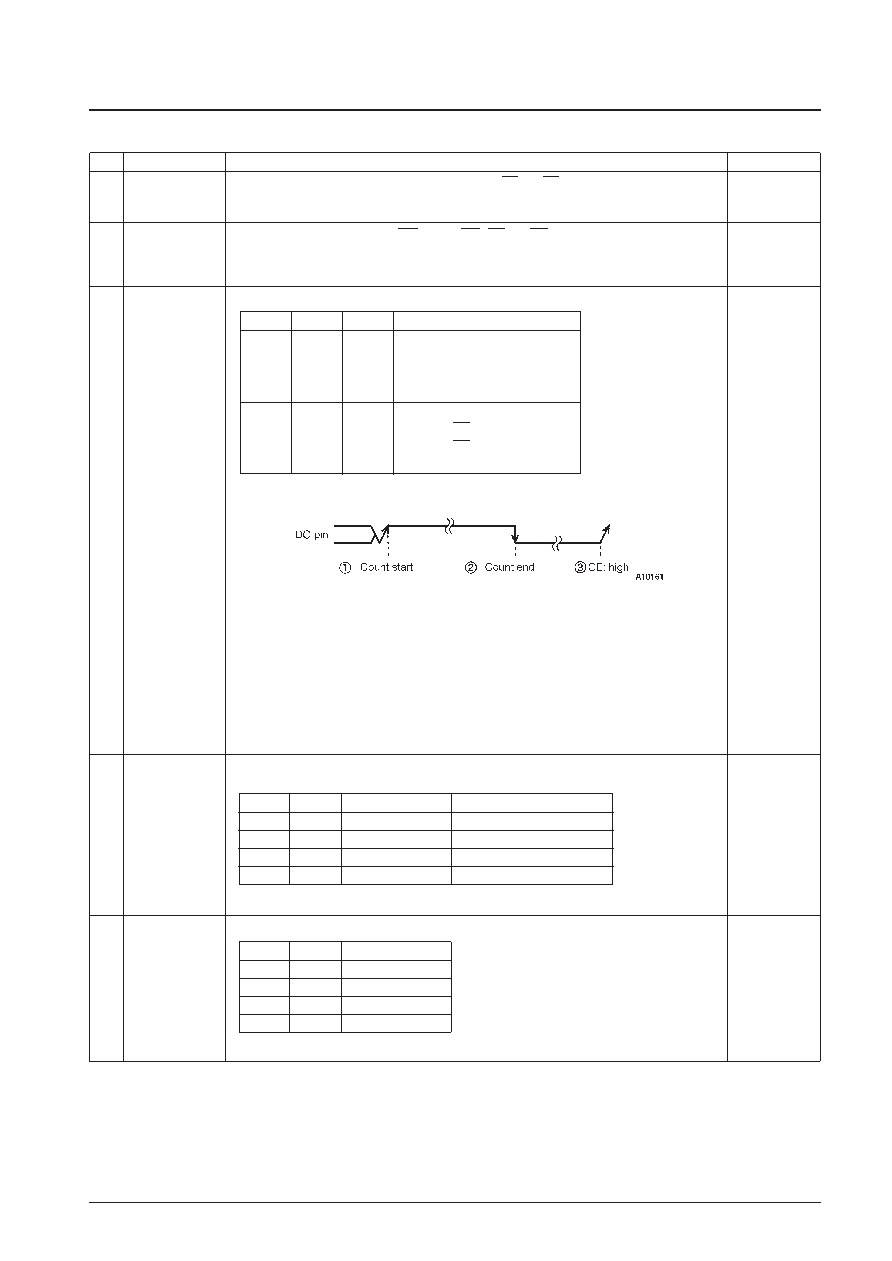

6

DO pin control data

DOC0

DOC1

DOC2

Determines the DO pin output.

The open state is selected after a power on reset.

*1. end-UC: IF counter measurement end check

(1)When end-UC is selected and an IF count is started (by switching CTE from 0 to 1), the DO pin

automatically goes to the open state.

(2)When the IF counter measurement period completes, the DO pin goes to the low level, allowing

applications to test for the completion of the count period.

(3)The DO pin is set to the open state by performing a serial data input or output operation (when the CE

pin is set high).

*2. The DO pin will go to the open state if the corresponding IO pin is set up to be an output port.

Note: During the data input period (the period that CE is high in IN1 or IN2 mode), the DO pin goes to the

open state regardless of the DO pin control data (DOC0 to DOC2). During the data output period (the

period that CE is high in OUT mode) the DO pin state reflects the internal DO serial data in

synchronization with the CL clock, regardless of the DO pin control data (DOC0 to DOC2).

UL0, UL1

CTE

IOC1

IOC2

7

Unlocked state

detection data

UL0, UL1

Selects the width of the phase error (E) detected for PLL lock state discrimination. The state is taken to

be unlocked if a phase error in excess of the detection width occurs.

* When the PLL is unlocked, the DO pin goes low and UL in the serial data output is set to 0.

Dead zone width: DZA < DZB < DZC < DZD

DOC0

DOC1

DOC2

8

Phase comparator

control data

DZ0, DZ1

Controls the phase comparator dead zone

DOC2

DOC1

DOC0

DO pin state

0

Open

0

1

Low when the PLL is unlocked

0

1

0

end-UC *1

0

1

Open

1

0

Open

1

0

1

The IO1 pin state *2

1

0

The IO2 pin state *2

1

Open

UL1

UL0

E detection width

Detection output

0

Stopped

Open

0

1

0

E is output directly

1

0

±0.55 s

E is extended by 1 to 2 ms

1

±1.11 s

E is extended by 1 to 2 ms

DZ1

DZ

Dead zone mode

0

DZA

0

1

DZB

1

0

DZC

1

DZD

Continued on next page.

相关PDF资料 |

PDF描述 |

|---|---|

| LES25A48-3V3RS | 1-OUTPUT 82.5 W DC-DC REG PWR SUPPLY MODULE |

| LES40A48-2V5S | 1-OUTPUT 100 W DC-DC REG PWR SUPPLY MODULE |

| LES25A48-1V2RA | 1-OUTPUT 30 W DC-DC REG PWR SUPPLY MODULE |

| L6926D013TR | 1.4 A SWITCHING REGULATOR, 600 kHz SWITCHING FREQ-MAX, PDSO8 |

| LNBP9V7V | 0.8 A SWITCHING REGULATOR, PZFM7 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC72121V-D-MPB-E | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Ammo Pack |

| LC72121V-D-TLM-E | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Tape and Reel |

| LC72121V-TLM-E | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| LC72122V | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Portable Equipment Electronic Tuning |

| LC72122V-MPB-E | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Ammo Pack |

发布紧急采购,3分钟左右您将得到回复。