- 您现在的位置:买卖IC网 > PDF目录67755 > LC72137 (SANYO SEMICONDUCTOR CO LTD) PLL FREQUENCY SYNTHESIZER, 40 MHz, PDIP22 PDF资料下载

参数资料

| 型号: | LC72137 |

| 厂商: | SANYO SEMICONDUCTOR CO LTD |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDIP22 |

| 封装: | SDIP-22 |

| 文件页数: | 13/22页 |

| 文件大小: | 348K |

| 代理商: | LC72137 |

No. 5743-20/22

LC72137, 72137M

Schemes in which a dead zone is present (OFF/OFF) have good loop stability, but have the problem that acquiring a

high C/N ratio can be difficult. On the other hand, although it is easy to acquire a high C/N ratio with schemes in

which there is no dead zone, it is difficult to achieve high loop stability. Therefore, it can be effective to select DZA

or DZB, which have no dead zone, in applications which require an FM S/N ratio in excess of 90 to 100 dB, or in

which an increased AM stereo pilot margin is desired. On the other hand, we recommend selecting DZC or DZD,

which provide a dead zone, for applications which do not require such a high FM signal-to-noise ratio and in which

either AM stereo is not used or an adequate AM stereo pilot margin can be achieved.

Dead Zone

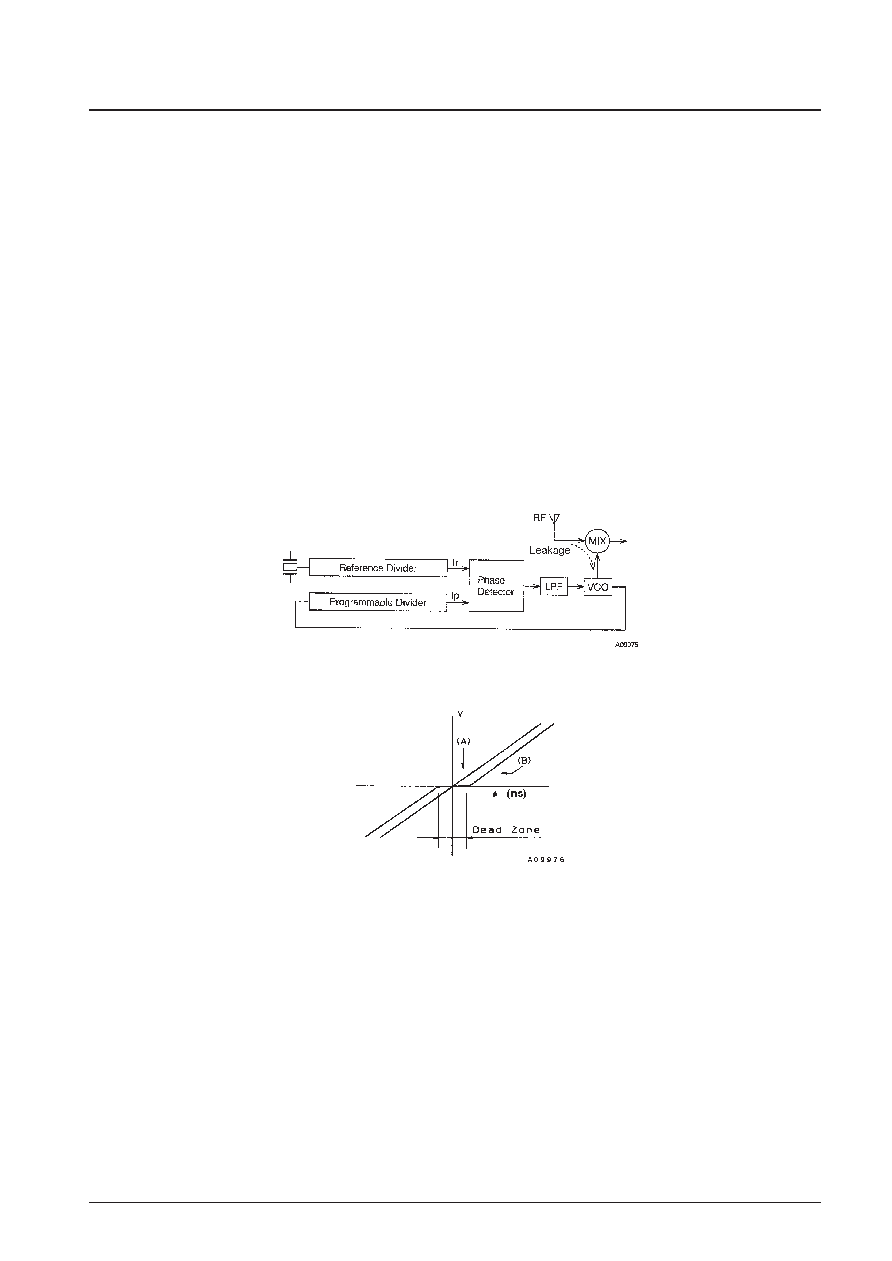

The phase comparator compares fp to a reference frequency (fr) as shown in Figure 4. Although the characteristics of

this circuit (see Figure 5) are such that the output voltage is proportional to the phase difference (line A), a region

(the dead zone) in which it is not possible to compare small phase differences occurs in actual ICs due to internal

circuit delays and other factors (line B). A dead zone as small as possible is desirable for products that must provide

a high S/N ratio.

However, since a larger dead zone makes this circuit easier to use, a larger dead zone is appropriate for popularly-

priced products. This is because it is possible for RF signals to leak from the mixer to the VCO and modulate the

VCO in popularly-priced products in the presence of strong RF inputs. When the dead zone is narrow, the circuit

outputs correction pulses and this output can further modulate the VCO and generate beat frequencies with the RF

signal.

Figure 4

Figure 5

2. Notes on the FMIN, AMIN, and IFIN Pins

Coupling capacitors must be placed as close as possible to their respective pin. A capacitance of about 100 pF is

desirable. In particular, if a capacitance of 1000 pF or over is used for the IF pin, the time to reach the bias level will

increase and incorrect counting may occur due to the relationship with the wait time.

3. Notes on IF Counting

→ SD must be used in conjunction with the IF counting time

When using IF counting, always implement IF counting by having the microprocessor determine the presence of the

IF-IC SD (station detect) signal and turn on the IF counter buffer only if the SD signal is present. Schemes in which

auto-searches are performed with only IF counting are not recommended, since they can stop at points where there is

no signal due to leakage output from the IF counter buffer.

相关PDF资料 |

PDF描述 |

|---|---|

| LC72137M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC99403 | SPECIALTY ANALOG CIRCUIT, BGA180 |

| LGDS-300-0-K/S | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| LGDS-300-0-K/T | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| LM10506TMX | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PBGA34 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC72137_11 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer |

| LC72137M | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

| LC72137MA-AE | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| LC72140 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers |

| LC72140M | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers |

发布紧急采购,3分钟左右您将得到回复。