- 您现在的位置:买卖IC网 > PDF目录30743 > LM1267NA/NOPB (NATIONAL SEMICONDUCTOR CORP) 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 PDF资料下载

参数资料

| 型号: | LM1267NA/NOPB |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 音频/视频放大 |

| 英文描述: | 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 |

| 封装: | PLASTIC, DIP-24 |

| 文件页数: | 11/20页 |

| 文件大小: | 1702K |

| 代理商: | LM1267NA/NOPB |

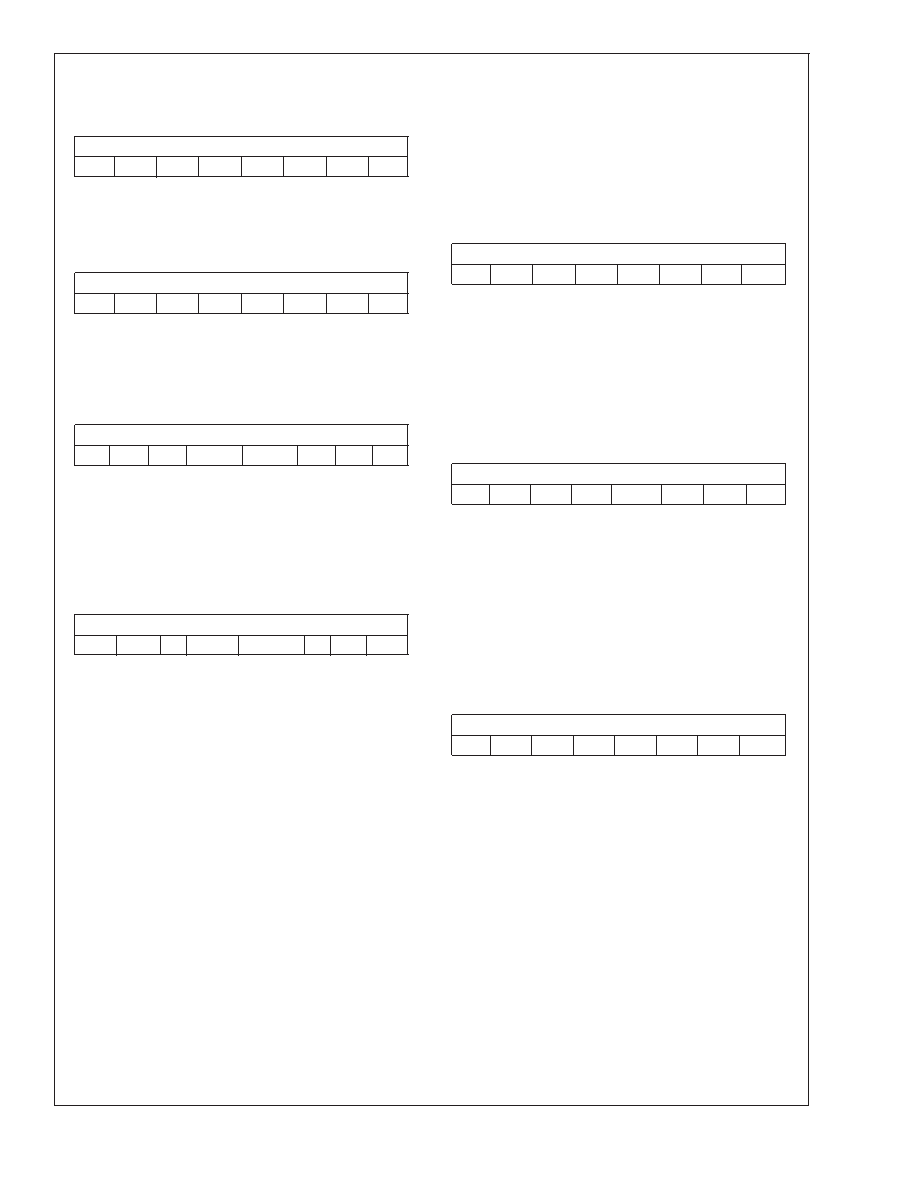

DAC Interface Register Definitions

(Continued)

Register name: DAC 3 (06h)

Bit 7

Bit 0

D3–7 D3–6 D3–5 D3–4 D3–3 D3–2 D3–1 D3–0

Bits 7–0: DAC 3. These eight bits determine the output

voltage of DAC 3.

DAC 4 Register (I

2C address 07h)

Register name: DAC 4 (07h)

Bit 7

Bit 0

D4–7 D4–6 D4–5 D4–4 D4–3 D4–2 D4–1 D4–0

Bits 7–0: DAC 4. These eight bits determine the output

voltage of DAC 4.

DC Offset and OSD Contrast Control Register (I

2C ad-

dress 08h)

Register name: DC Offset/OSD Cont. (08h)

Bit 7

Bit 0

RSV

OSDC1

OSDC0

DC2

DC1

DC0

Bits 2–0: DC Offset Control. These three bits determine the

active video DC offset to all three channels.

Bits 4–3: OSD Contrast Control. These two bits determine

the contrast level of the OSD information.

Bits 7–5: Reserved.

Global Video Control Register (I

2C address 09h)

Register name: Global Control (09h)

Bit 7

Bit 0

RSV

0

DCF4

DCF1–3

0

PS

BV

Bit 0:

Blank Video. When this bit is a one, blank the

video output. When this bit is a zero allow normal

video out.

Bit 1:

Power Save. When this bit is a one, shut down

the analog circuits to support sleep mode. When

this bit is a zero enable the analog circuits for

normal operation.

Bit 2:

MUST BE SET TO “0” FOR PROPER OPERA-

TION.

Bit 3:

DAC1–3 Configuration. When this bit is a zero

the DAC outputs of DAC1–3 are full scale

(0V–4.5V). When this bit is 1, the range of

DAC1–3 are halved (0V–2.25V).

Bit 4:

DAC4 Configuration. When this bit is a zero the

DAC4 output is not mixed with the other DAC

outputs. When the bit is one, 50% of the DAC4

output is added to DAC1–3.

Bit 5:

MUST BE SET TO “0” FOR PROPER OPERA-

TION.

Bits 7–6: Reserved.

Increment Mode Register (I

2C address 0Ah)

Register name: Increment Mode (0Ah)

Bit 7

Bit 0

RSV

TST

INCR

Bit 0:

Increment Enable. When set to a “0”, the default

value, the increment mode is enabled. This al-

lows the registers to be updated sequentially by

sending another block of data.

Bit 1:

MUST BE SET TO “0” FOR PROPER OPERA-

TION.

Bits 7–2: Reserved.

Clamp Polarity and Bandwidth (I

2C address 0Bh)

Register name: Clamp/BW (0Bh)

Bit 7

Bit 0

RSV

CLMP

BW1

BW2

BW0

Bits 2–0: Bandwidth. Used to set the bandwidth of the

preamp. The default is 100. When all bits are set

to “1”, the LM1267 will have maximum bandwidth,

when all bits are set to “0” the LM1267 will have

minimum bandwidth.

Bit 3:

Determines the polarity of the clamp signal used

by the LM1267, “0” (default) is a positive clamp

signal, “1” is a negative going clamp signal.

Bits 7–4: Reserved.

Software Reset Register (I

2C address 0Fh)

Register name: Software Reset (0Fh)

Bit 7

Bit 0

RSV

SRST

Bit 0:

Software Reset. Setting this bit causes a software

reset. All registers (except this one) are loaded

with their default values. All operations currently

in progress are aborted (except for I

2C transac-

tions). This bit automatically clears itself when the

reset has been completed.

Bits 7–1: Reserved.

LM1267

www.national.com

19

相关PDF资料 |

PDF描述 |

|---|---|

| LM1269NA/NOPB | 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 |

| LM1276AAA/NA | 1 CHANNEL, VIDEO PREAMPLIFIER, PDIP28 |

| LM1279AN/NOPB | 3 CHANNEL, VIDEO AMPLIFIER, PDIP20 |

| LM1279N/NOPB | 1 CHANNEL, VIDEO AMPLIFIER, PDIP20 |

| LM136A-2.5MD8 | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 5 V, UUC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LM1269 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:110 MHz I2C Compatible RGB Video Amplifier System with OSD & DACs |

| LM1269DNA | 制造商:Texas Instruments 功能描述: |

| LM1269DNA/NOPB | 功能描述:IC PREAMP CMOS 110MHZ 24-DIP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| LM1269NA | 制造商:Texas Instruments 功能描述:Video Amplifiers 制造商:Texas Instruments 功能描述:-LIFETIME BUYS TIL 05/12 |

| LM1269NA/NOPB | 功能描述:视频放大器 RoHS:否 制造商:ON Semiconductor 通道数量:4 电源类型: 工作电源电压:3.3 V, 5 V 电源电流: 最小工作温度: 最大工作温度: 封装 / 箱体:TSSOP-14 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。