- 您现在的位置:买卖IC网 > PDF目录358886 > LMX2312U (NATIONAL SEMICONDUCTOR CORP) PLLatinum⑩ Ultra Low Power Frequency Synthesizer for RF Personal Communications PDF资料下载

参数资料

| 型号: | LMX2312U |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | XO, clock |

| 英文描述: | PLLatinum⑩ Ultra Low Power Frequency Synthesizer for RF Personal Communications |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 1200 MHz, QCC20 |

| 封装: | THIN, CSP-20 |

| 文件页数: | 22/29页 |

| 文件大小: | 662K |

| 代理商: | LMX2312U |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页

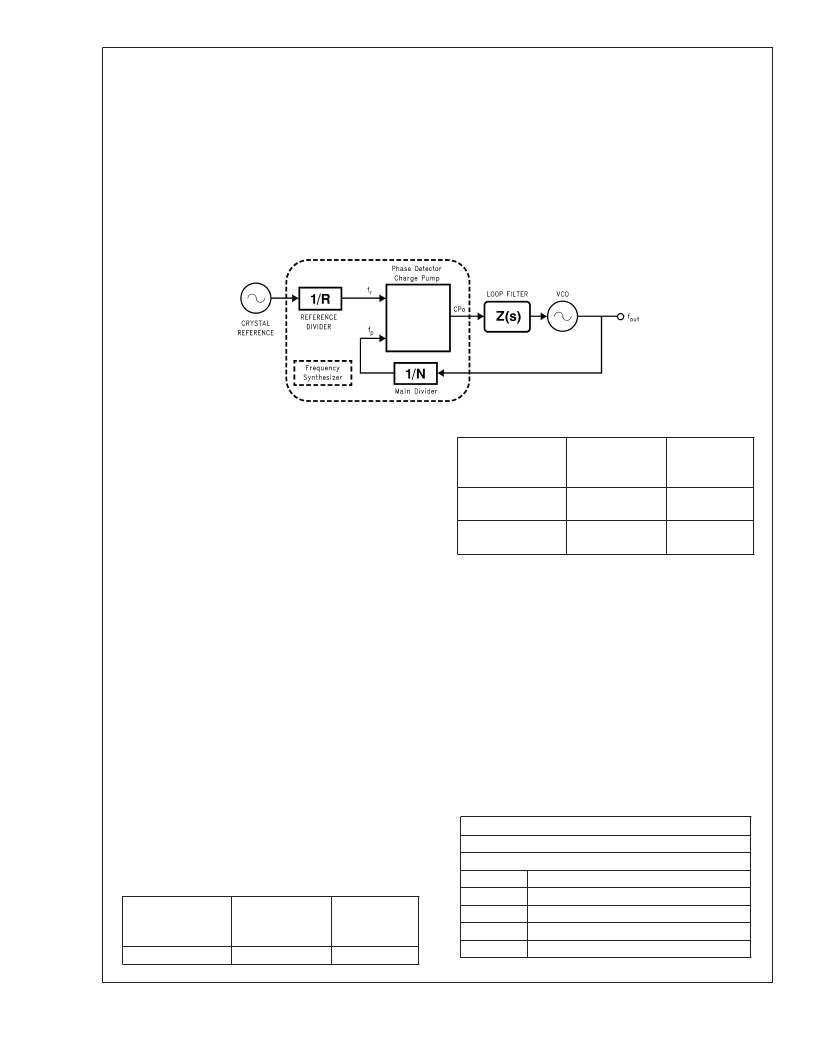

1.0 Functional Description

The basic phase-lock-loop (PLL) configuration consists of a

high-stability crystal reference oscillator, a frequency synthe-

sizer such as the National Semiconductor LMX2310/1/2/3U,

a voltage controlled oscillator (VCO), and a passive loop

filter. The frequency synthesizer includes a phase detector, a

current mode charge pump, as well as a programmable

reference divider and feedback frequency divider. The VCO

frequency is established by dividing the crystal reference

signal down via the reference divider to obtain a frequency

that sets the comparison frequency. This reference signal, f

r

,

is then presented to the input of a phase/frequency detector

and compared with another signal, f

p

, which was obtained by

dividing the VCO frequency down by way of the feedback

counter. The phase/frequency detector measures the phase

error between the f

and f

signals and outputs control sig-

nals that are directly proportional to the phase error. The

charge pump then pumps charge into or out of the loop filter

based on the magnitude and direction of the phase error.

The loop filter converts the charge into a stable control

voltage for the VCO. The phase/frequency detector’s func-

tion is to adjust the voltage presented to the VCO until the

feedback signal’s frequency and phase match that of the

reference signal. When this “phase-locked” condition exists,

the RF VCO frequency will be N times that of the comparison

frequency, where N is the feedback divider ratio.

20043829

1.1 REFERENCE OSCILLATOR

The reference oscillator frequency for the RF PLLis provided

from the external source via the OSC

in

pin. The low noise

reference buffer circuit supports frequencies from 2 MHz to

50 MHz with a minimum input sensitivity of 0.5 V

pp

. The input

can be driven from an external CMOS or TTL logic gate. The

output of this buffer drives the R COUNTER. The output of

the buffer also connects to an oscillator/buffer circuit. Its

output connects to the OSC

pin. The oscillator/buffer cir-

cuit can be used as a buffer to provide the reference fre-

quency to other circuitry. It can also be used as an oscillator

with a crystal/resonator with proper components connected

between OSC

in

and OSC

out

pins to generate a reference

frequency.

1.2 REFERENCE DIVIDER (R COUNTER)

The reference divider is comprised of a 15-bit CMOS binary

counter that supports a continuous integer divide range from

2 to 32,767. The divide ratio should be chosen such that the

maximum phase comparison frequency of 10 MHz is not

exceeded. The reference divider circuit is clocked by the

output of the reference buffer circuit. The output of the

reference divider circuit feeds the reference input of the

phase detector circuit. The frequency of the reference input

to the phase detector (also referred to as the comparison

frequency) is equal to reference oscillator frequency divided

by the reference divider ratio. Refer to Section 3.2.1 for

details on programming the R COUNTER.

1.3 PRESCALERS

The LMX2310/1/2U contains a selectable, dual modulus

32/33 and 16/17 prescaler. The LMX2313U contains a se-

lectable, dual modulus 16/17 and 8/9 prescaler.

PLL

Input

Frequency

F

IN

>

1.2 GHz

PLL

Part

Numbers

LMX2310/1U

Allowable

Prescaler

Values

32/33

PLL

Input

Frequency

F

IN

≤

1.2 GHz

PLL

Part

Numbers

LMX2310/1/2U

Allowable

Prescaler

Values

16/17 or

32/33

8/9 or

16/17

F

IN

≤

600

MHz

LMX2313U

The complimentary F

and F

input pins drive the input of

a bipolar, differential-pair amplifier. The output of the bipolar,

differential-pair amplifier drives a chain of ECL D-type flip-

flops in a dual modulus configuration. The output of the

prescaler is used to clock the subsequent programmable

feedback divider. Refer to Section 3.3.2 for details on pro-

gramming the Prescaler Value.

1.4 FEEDBACK DIVIDER (N COUNTER)

The N COUNTER is clocked by the output of the prescaler.

The N COUNTER is composed of a 13-bit programmable

integer divider. The 5-bit swallow counter is part of the

prescaler. Selecting a 32/33 prescaler provides a minimum

continuous divider range from 992 to 262,143 while selecting

a 16/17 prescaler value allows for continuous divider values

from 240 to 131,071. In the LMX2313U, selecting a 8/9

prescaler provides a minimum continuous divider range from

56 to 65535.

N = (P x NB_CNTR) + NA_CNTR

F

IN

= N x F

φ

Definitions

F

φ

Phase Detector Comparison Frequency

F

IN

RF Input Frequency

P

Prescaler Value

NA_CNTR

A Counter Value

NB_CNTR

B Counter Value

L

www.national.com

22

相关PDF资料 |

PDF描述 |

|---|---|

| LMX2314 | 1.2 GHz Frequency Synthesizer for RF Personal Communications |

| LMX2314M | 1.2 GHz Frequency Synthesizer for RF Personal Communications |

| LMX2314MX | 1.2 GHz Frequency Synthesizer for RF Personal Communications |

| LMX2315 | Frequency Synthesizer for RF Personal Communications |

| LMX2315TM | Frequency Synthesizer for RF Personal Communications |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LMX2312USLDX | 制造商:MAJOR 功能描述: |

| LMX2312USLDX/NOPB | 功能描述:IC FREQ SYNTH 1.2GHZ 20LAMTCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2313U | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PLLatinum⑩ Ultra Low Power Frequency Synthesizer for RF Personal Communications |

| LMX2313USLDX | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PLLatinum⑩ Ultra Low Power Frequency Synthesizer for RF Personal Communications |

| LMX2313USLDX/NOPB | 功能描述:IC FREQ SYNTH 600MHZ 20LAMTCSP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。