- 您现在的位置:买卖IC网 > PDF目录377712 > LT1671CS8 (LINEAR TECHNOLOGY CORP) 60ns, Low Power, Single Supply, Ground-Sensing Comparator PDF资料下载

参数资料

| 型号: | LT1671CS8 |

| 厂商: | LINEAR TECHNOLOGY CORP |

| 元件分类: | 运动控制电子 |

| 英文描述: | 60ns, Low Power, Single Supply, Ground-Sensing Comparator |

| 中文描述: | COMPARATOR, 4000 uV OFFSET-MAX, 85 ns RESPONSE TIME, PDSO8 |

| 封装: | 0.150 INCH, PLASTIC, SOP-8 |

| 文件页数: | 7/12页 |

| 文件大小: | 199K |

| 代理商: | LT1671CS8 |

7

LT1671

APPLICATIO

S I

N

FOR

ATIO

U

Common Mode Considerations

The LT1671 is specified for a common mode range of –5V

to 3.5V on a

±

5V supply or a common mode range of 0V

to 3.5V on a single 5V supply. A more general consider-

ation is that the common mode range is 0V below the

negative supply and 1.5V below the positive supply, inde-

pendent of the actual supply voltage. The criterion for

common mode limit is that the output still responds

correctly to a small differential input signal.

When either input signal falls below the negative common

mode limit, the internal PN diode formed with the sub-

strate can turn on, resulting in significant current flow

through the die. An external Schottky clamp diode

between the input and the negative rail can speed up

recovery from negative overdrive by preventing the sub-

strate diode from turning on.

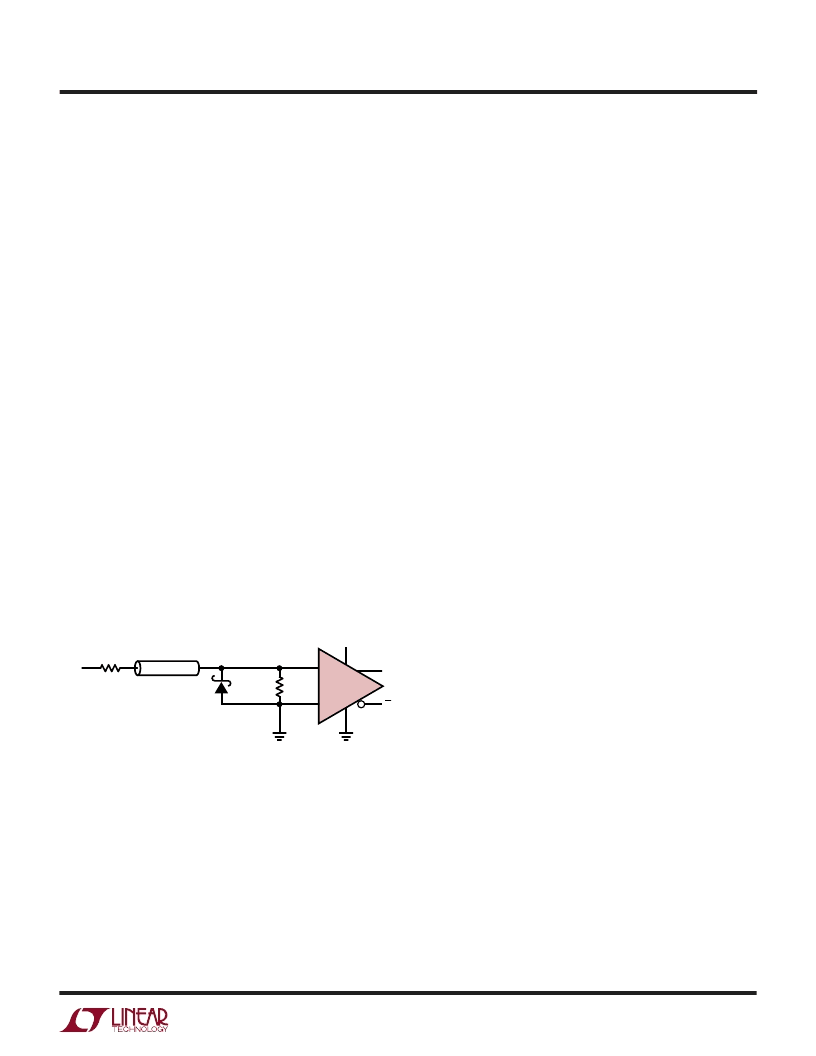

The zero crossing detector in Figure 1 demonstrates the

use of a fast clamp diode. The zero crossing detector

terminates the transmission line at its 50

characteristic

impedance. Negative inputs should not fall below –2V to

keep the signal current within the clamp diode’s maximum

forward rating. Positive inputs should not exceed the

devices absolute maximum ratings nor the power rating

on the terminating resistor.

W

U

5V

1671 F01

–

+

LT1671

Q

Q

CABLE

R

T

50

V

IN

R

S

50

1N5712

Figure 1. Fast Zero Crossing Detector

Either input may go above the positive common mode

limit without damaging the comparator. The upper voltage

limit is determined by an internal diode from each input to

the positive supply. The input may go above the positive

supply as long as it does not go far enough above it to

conduct more than 10mA. Functionality will continue if the

remaining input stays within the allowed common mode

range. There will, however, be an increase in propagation

delay as the input signal switches back into the common

mode range.

Input Bias Current

Input bias current is measured with the output held at

1.4V. As with any PNP differential input stage, the LT1671

bias current flows out of the device. It will go to zero on an

input which is high and double on an input which is low.

LATCH Pin Dynamics

The LATCH pin is intended to retain input data (output

latched) when the LATCH pin goes high. The pin will float

to a high state when disconnected, so a flow-through

condition requires that the LATCH pin be grounded. The

LATCH pin is designed to be driven with either a TTL or

CMOS output. It has no built-in hysteresis.

To guarantee data retention, the input signal must remain

valid at least 35ns after the latch goes high (hold time), and

must be valid at least –15ns before the latch goes high

(setup time). The negative setup time simply means that

the data arriving 15ns after (rather than before) the latch

signal is valid. When the latch signal goes low, new data

will appear at the output in approximately 60ns (latch

propagation delay).

Measuring Response Time

To properly measure the response of the LT1671 requires

an input signal source with very fast rise times and

exceptionally clean settling characteristics. The last

requirement comes about because the standard compara-

tor test calls for an input step size that is large compared

to the overdrive amplitude. Typical test conditions are

100mV step size with 5mV overdrive. This requires an

input signal that settles to within 1% (1mV) of final value

in only a few nanoseconds with no ringing or settling tail.

Ordinary high speed pulse generators are not capable of

generating such a signal, and in any case, no ordinary

oscilloscope is capable of displaying the waveform to

check its fidelity. Some means must be used to inherently

generate a fast, clean edge with known final value. The

circuit shown in Figure 2 is the best electronic means of

generating a fast, clean step to test comparators. It uses

a very fast transistor in a common base configuration. The

transistor is switched off with a fast edge from the genera-

tor and the collector voltage settles to exactly 0V in just a

few nanoseconds. The most important feature of this

相关PDF资料 |

PDF描述 |

|---|---|

| LT1671IS8 | 60ns, Low Power, Single Supply, Ground-Sensing Comparator |

| LT1675CMS8-1 | 250MHz, Triple and Single RGB Multiplexer with Current Feedback Amplifiers |

| LT1675CGN | 250MHz, Triple and Single RGB Multiplexer with Current Feedback Amplifiers |

| LT1675CS8-1 | 250MHz, Triple and Single RGB Multiplexer with Current Feedback Amplifiers |

| LT1676C | RADIATION HARDENED HIGH EFFICIENCY, 5 AMP SWITCHING REGULATORS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LT1671CS8#PBF | 功能描述:IC COMP GRND-SENSNG LOWPWR 8SOIC RoHS:是 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 标准包装:1 系列:- 类型:通用 元件数:1 输出类型:CMOS,开路集电极,TTL 电压 - 电源,单路/双路(±):2.7 V ~ 5.5 V 电压 - 输入偏移(最小值):7mV @ 5V 电流 - 输入偏压(最小值):0.25µA @ 5V 电流 - 输出(标准):84mA @ 5V 电流 - 静态(最大值):120µA CMRR, PSRR(标准):- 传输延迟(最大):600ns 磁滞:- 工作温度:-40°C ~ 85°C 封装/外壳:SC-74A,SOT-753 安装类型:表面贴装 包装:剪切带 (CT) 产品目录页面:1268 (CN2011-ZH PDF) 其它名称:*LMV331M5*LMV331M5/NOPBLMV331M5CT |

| LT1671CS8#PBF | 制造商:Linear Technology 功能描述:Micropower Comparator IC |

| LT1671CS8#TR | 功能描述:IC COMPARATOR 60NS LOW PWR 8SOIC RoHS:否 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 标准包装:25 系列:- 类型:带电压基准 元件数:4 输出类型:CMOS,开路漏极,TTL 电压 - 电源,单路/双路(±):2 V ~ 11 V,±1 V ~ 5.5 V 电压 - 输入偏移(最小值):10mV @ 5V 电流 - 输入偏压(最小值):- 电流 - 输出(标准):0.015mA @ 5V 电流 - 静态(最大值):8.5µA CMRR, PSRR(标准):80dB CMRR,80dB PSRR 传输延迟(最大):12µs 磁滞:50mV 工作温度:0°C ~ 70°C 封装/外壳:16-DIP(0.300",7.62mm) 安装类型:通孔 包装:管件 |

| LT1671CS8#TRPBF | 功能描述:IC COMP GRND-SENSNG LOWPWR 8SOIC RoHS:是 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 标准包装:25 系列:- 类型:带电压基准 元件数:4 输出类型:CMOS,开路漏极,TTL 电压 - 电源,单路/双路(±):2 V ~ 11 V,±1 V ~ 5.5 V 电压 - 输入偏移(最小值):10mV @ 5V 电流 - 输入偏压(最小值):- 电流 - 输出(标准):0.015mA @ 5V 电流 - 静态(最大值):8.5µA CMRR, PSRR(标准):80dB CMRR,80dB PSRR 传输延迟(最大):12µs 磁滞:50mV 工作温度:0°C ~ 70°C 封装/外壳:16-DIP(0.300",7.62mm) 安装类型:通孔 包装:管件 |

| LT1671CS8PBF | 制造商:Linear Technology 功能描述:Comparator 60ns Low Power 5V SOIC8 |

发布紧急采购,3分钟左右您将得到回复。