- 您现在的位置:买卖IC网 > PDF目录1825 > LT3710EFE#TRPBF (Linear Technology)IC REG CTRLR BUCK PWM 16-TSSOP PDF资料下载

参数资料

| 型号: | LT3710EFE#TRPBF |

| 厂商: | Linear Technology |

| 文件页数: | 7/12页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM 16-TSSOP |

| 标准包装: | 2,500 |

| PWM 型: | 电流/电压模式 |

| 输出数: | 2 |

| 频率 - 最大: | 340kHz |

| 占空比: | 90% |

| 电源电压: | 8 V ~ 24 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm)裸露焊盘 |

| 包装: | 带卷 (TR) |

�� �

�

�

�LT3710�

�OPERATIO�

�To� generate� isolated� multiple� outputs,� most� systems� use�

�either� multiple� secondary� windings� or� cascade� regulators�

�for� each� additional� output.� Multiple� secondary� windings�

�sacrifice� regulation� of� the� auxiliary� outputs.� Cascaded�

�regulators� require� a� larger� inductor� for� the� main� output,�

�because� all� of� the� power� is� processed� in� series.�

�By� generating� the� auxiliary� output(s)� from� the� secondary�

�winding� of� the� main� output,� the� LT3710� allows� for� parallel�

�processing� of� the� output� power.� This� minimizes� the� main�

�output� inductor� size� and� directly� regulates� the� auxiliary�

�output.� With� synchronous� rectification,� the� system� effi-�

�ciency� is� greatly� improved.�

�Refering� to� the� Block� Diagram,� the� LT3710� basic� functions�

�include� a� voltage� amplifier,� VA,� to� regulate� the� output�

�until� the� ramp� signal� intersects� the� feedback� error� ampli-�

�fier� output� VA� OUT� .� The� top� MOSFET� M1� turns� on,� pulling�

�the� switch� node� voltage� to� V� S� .� The� inductor� current� of� the�

�LT3710� circuit� is� then� charged� by� V� S� –� V� OUT2� .� The� effective�

�on� time� of� this� buck� circuit� ends� when� the� secondary�

�voltage� becomes� zero.� The� next� cycle� repeats.�

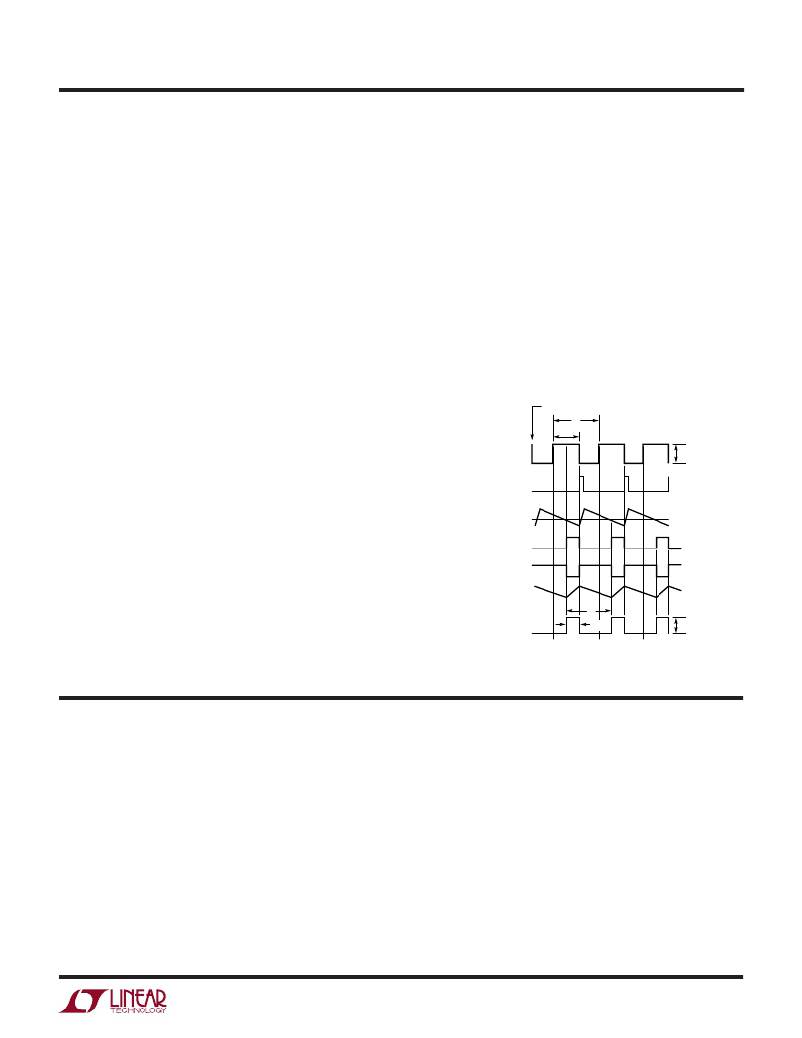

�The� ideal� equation� for� duty� cycle� of� the� LT3710� is:�

�D2� =� V� OUT2� /V� SP�

�where� V� OUT2� is� the� auxiliary� output� voltage,� V� SP� is� the�

�amplitude� of� the� secondary� voltage� and� D2� is� the� duty�

�cycle� of� the� switching� node� voltage� V� SW� ,� as� defined� in�

�Figure� 2.�

�V� RESET�

�voltage� to� within� typically� 1.5%,� a� voltage� mode� PWM� with�

�D� 1� T�

�T�

�trailing� edge� synchronization� and� leading� edge� modula-�

�tion,� a� current� limit� amplifier,� CA1,� and� high� speed� syn-�

�chronous� switch� drivers.�

�During� normal� operation� (see� Figure� 2),� a� switching� cycle�

�begins� at� the� falling� edge� of� the� transformer� secondary�

�voltage� V� S� .� The� internal� oscillator� is� reset,� turning� off� the�

�top� MOSFET� M1� and� turning� on� the� bottom� MOSFET� M2.�

�During� this� portion� of� the� cycle,� the� inductor� current� is�

�discharged� by� the� output� voltage� V� OUT2� .� The� transformer�

�secondary� voltage� V� S� will� go� high� during� this� portion� of� the�

�cycle.� Since� M1� is� off,� the� switch� node� voltage� V� SW�

�TRANSFORMER�

�SECONDARY� VOLTAGE�

�SYNC� SIGNAL� V� RESET�

�RAMP� V� CSET�

�VA� OUT�

�TGATE�

�BGATE�

�I� L�

�SWITCH� NODE� V� SW�

�V� S�

�T�

�D� 2� T�

�V� SP�

�V� SP�

�3710� F02�

�remains� zero.� The� inductor� current� continues� to� be� dis-�

�charged� by� the� output� voltage� V� OUT2� .� This� condition� lasts�

�APPLICATIO� S� I� FOR� ATIO�

�Synchronization� and� Oscillation� Frequency� Setting�

�The� switching� is� synchronized� to� the� secondary� winding�

�falling� edge� and� the� synchronization� threshold� is� typically�

�2.5V.� The� synchronization� falling� edge� triggers� an� internal�

�inverted� ramp� (see� Figure� 2)� and� starts� a� new� switching�

�cycle� for� the� leading� edge� voltage� mode� PWM.� The� reason�

�for� using� leading� edge� modulation� is� to� keep� the� trans-�

�former� primary� side� peak� current� sensing� undisturbed.�

�For� proper� synchronization,� the� oscillator� frequency� should�

�be� set� lower� than� the� system� switching� frequency� with�

�Figure� 2.� Leading� Edge� Modulation,�

�Trailing� Edge� Synchronization�

�f� OSC� <� (f� SL� ?� 0.8)�

�f� SL� is� the� low� limit� of� the� system� switching� frequency� and�

�0.8� is� the� tolerance� of� f� OSC� .�

�For� example,� a� system� of� 200KHz� with� 15%� tolerance,�

�then� f� SL� =� 200k� ?� 85%� =� 170kHz;� and� f� OSC� <� (170k� ?� 0.8),�

�f� OSC� should� be� set� below� 136kHz.�

�Once� f� OSC� is� determined,� CSET� can� be� calculated� by�

�CSET� =� (107250pf/f� OSC(kHz)� )� –� 50pF.�

�For� f� OSC� =� 100kHz,� CSET� =� 1022.5pF.�

�tolerances� taken� into� account.�

�3710f�

�7�

�相关PDF资料 |

PDF描述 |

|---|---|

| LT3724EFE#PBF | IC REG CTRLR BST INV PWM 16TSSOP |

| LT3740EDHC#PBF | IC REG CTRLR BUCK PWM CM 16-DFN |

| LT3741EFE#PBF | IC REG CTRLR BUCK PWM CM 20TSSOP |

| LT3742EUF#PBF | IC REG CTRLR BUCK PWM CM 24-QFN |

| LT3748HMS#PBF | IC REG CTRLR FLYBK ISO CM 16MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LT371LF | 制造商:EDSYN 功能描述: |

| LT3724 | 制造商:LINER 制造商全称:Linear Technology 功能描述:High Voltage, Current Mode Switching Regulator Controller |

| LT3724_1 | 制造商:LINER 制造商全称:Linear Technology 功能描述:High Voltage, Current Mode Switching Regulator Controller Thermal Shutdown |

| LT3724EFE | 制造商:Linear Technology 功能描述:DC DC Cntrlr Single-OUT Step Up/Step Down 4V to 60V Input 16-Pin TSSOP EP |

| LT3724EFE#PBF | 功能描述:IC REG CTRLR BST INV PWM 16TSSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 特色产品:LM3753/54 Scalable 2-Phase Synchronous Buck Controllers 标准包装:1 系列:PowerWise® PWM 型:电压模式 输出数:1 频率 - 最大:1MHz 占空比:81% 电源电压:4.5 V ~ 18 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-5°C ~ 125°C 封装/外壳:32-WFQFN 裸露焊盘 包装:Digi-Reel® 产品目录页面:1303 (CN2011-ZH PDF) 其它名称:LM3754SQDKR |

发布紧急采购,3分钟左右您将得到回复。