- 您现在的位置:买卖IC网 > PDF目录2004 > LTC1750IFW#PBF (Linear Technology)IC ADC 14BIT 80MSPS SMPL 48TSSOP PDF资料下载

参数资料

| 型号: | LTC1750IFW#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 4/20页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 80MSPS SMPL 48TSSOP |

| 标准包装: | 39 |

| 位数: | 14 |

| 采样率(每秒): | 80M |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 1.69W |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 48-TSSOP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,双极;1 个差分,双极 |

12

LTC1750

1750f

In operation, the ADC quantizes the input to the stage and

the quantized value is subtracted from the input by the

DAC to produce a residue. The residue is amplified and

output by the residue amplifier. Successive stages operate

out of phase so that when the odd stages are outputting

their residue, the even stages are acquiring that residue

and visa versa.

When ENC is low, the analog input is sampled differentially

directly onto the input sample-and-hold capacitors, inside

the “Input S/H” shown in the block diagram. At the instant

that ENC transitions from low to high, the sampled input

is held. While ENC is high, the held input voltage is

buffered by the S/H amplifier which drives the first pipelined

ADC stage. The first stage acquires the output of the S/H

during this high phase of ENC. When ENC goes back low,

the first stage produces its residue which is acquired by

the second stage. At the same time, the input S/H goes

back to acquiring the analog input. When ENC goes back

high, the second stage produces its residue which is

acquired by the third stage. An identical process is re-

peated for the third stage, resulting in a third stage residue

that is sent to the fourth stage ADC for final evaluation.

Each ADC stage following the first has additional range to

accommodate flash and amplifier offset errors. Results

from all of the ADC stages are digitally synchronized such

that the results can be properly combined in the correction

logic before being sent to the output buffer.

SAMPLE/HOLD OPERATION AND INPUT DRIVE

Sample/Hold Operation

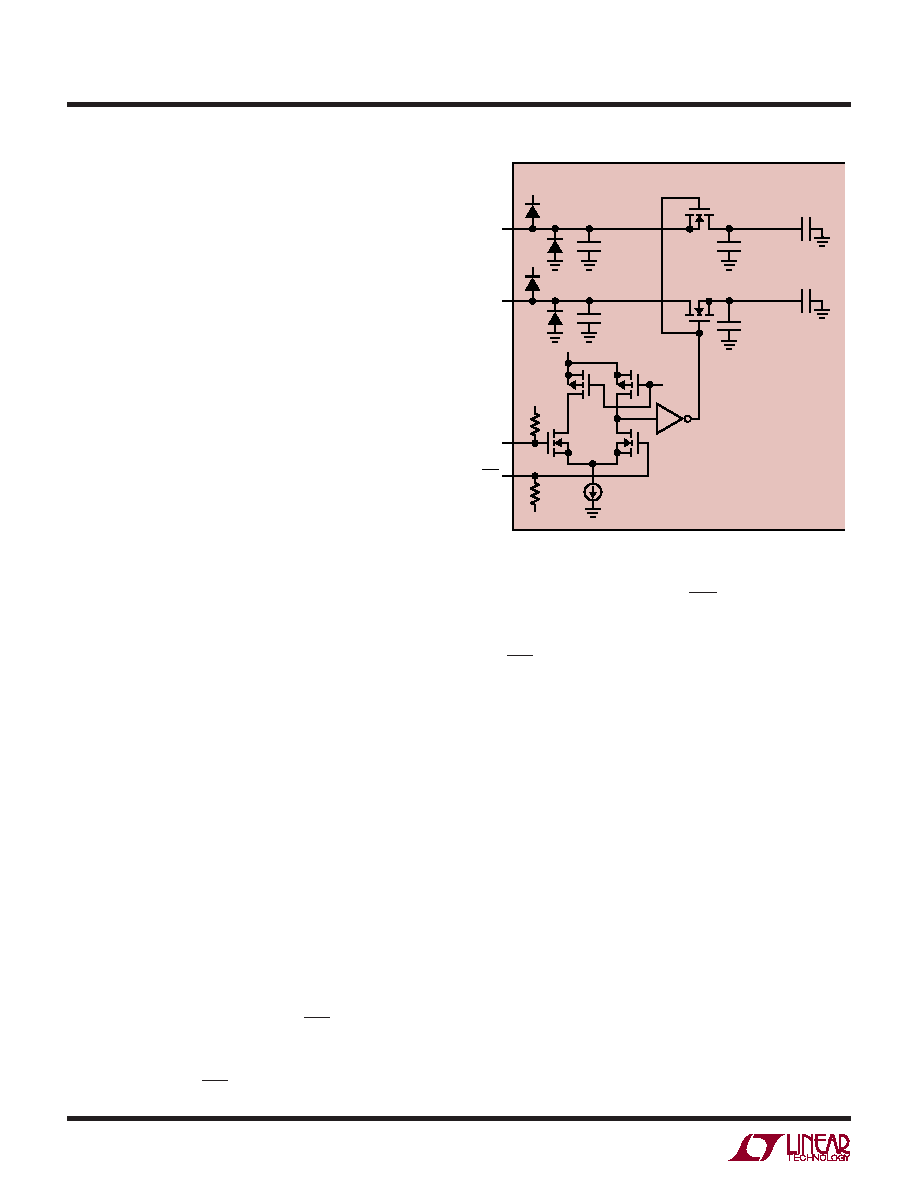

Figure 2 shows an equivalent circuit for the LTC1750

CMOS differential sample-and-hold. The differential ana-

log inputs are sampled directly onto sampling capacitors

(CSAMPLE) through NMOS switches. This direct capacitor

sampling results in lowest possible noise for a given

sampling capacitor size. The capacitors shown attached to

each input (CPARASITIC) are the summation of all other

capacitance associated with each input.

During the sample phase when ENC/ENC is low, the NMOS

switch connects the analog inputs to the sampling capaci-

tors and they charge to, and track the differential input

voltage. When ENC/ENC transitions from low to high the

sampled input voltage is held on the sampling capacitors.

During the hold phase when ENC/ENC is high the sampling

capacitors are disconnected from the input and the held

voltage is passed to the ADC core for processing. As

ENC/ENC transitions from high to low the inputs are

reconnected to the sampling capacitors to acquire a new

sample. Since the sampling capacitors still hold the previ-

ous sample, a charging glitch proportional to the change

in voltage between samples will be seen at this time. If the

change between the last sample and the new sample is

small the charging glitch seen at the input will be small. If

the input change is large, such as the change seen with

input frequencies near Nyquist, then a larger charging

glitch will be seen.

Common Mode Bias

The ADC sample-and-hold circuit requires differential drive

to achieve specified performance. Each input should swing

within the valid input range, around a common mode volt-

age of 2.0V. The VCM output pin (Pin 2) may be used to pro-

vide the common mode bias level. VCM can be tied directly

to the center tap of a transformer to set the DC input level

or as a reference level to an op amp differential driver cir-

cuit. The VCM pin must be bypassed to ground close to the

ADC with a 4.7

F or greater capacitor.

APPLICATIO S I FOR ATIO

WU

UU

Figure 2. Equivalent Input Circuit

CSAMPLE

3.5pF

RON

30

RON

30

VDD

LTC1750

AIN

+

1750 F02

CSAMPLE

3.5pF

BIAS

VDD

5V

AIN

–

ENC

2V

6k

2V

6k

CPARASITIC

2.4pF

CPARASITIC

1pF

CPARASITIC

1pF

CPARASITIC

2.4pF

相关PDF资料 |

PDF描述 |

|---|---|

| LTC1799HS5#TRPBF | IC OSC SILICON 33MHZ TSOT23-5 |

| LTC1821ACGW | IC D/A CONV 16BIT PRECISE 36SSOP |

| LTC1851CFW | IC ADC 12BIT 1.25MSPS 48-TSSOP |

| LTC1853IFW#TRPBF | IC A/D CONV 8CH 12BIT 48-TSSOP |

| LTC1856IG#PBF | IC ADC 16BIT 100KSPS 28-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC1751EMS8 | 功能描述:IC REG SWITCHD CAP DBL ADJ 8MSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 标准包装:2,500 系列:- 类型:升压(升压) 输出类型:可调式 输出数:1 输出电压:1.24 V ~ 30 V 输入电压:1.5 V ~ 12 V PWM 型:电流模式,混合 频率 - 开关:600kHz 电流 - 输出:500mA 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) 供应商设备封装:8-SOIC |

| LTC1751EMS8#PBF | 功能描述:IC REG SWITCHD CAP DBL ADJ 8MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 标准包装:250 系列:- 类型:降压(降压) 输出类型:固定 输出数:1 输出电压:1.2V 输入电压:2.05 V ~ 6 V PWM 型:电压模式 频率 - 开关:2MHz 电流 - 输出:500mA 同步整流器:是 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:6-UFDFN 包装:带卷 (TR) 供应商设备封装:6-SON(1.45x1) 产品目录页面:1032 (CN2011-ZH PDF) 其它名称:296-25628-2 |

| LTC1751EMS8#TR | 功能描述:IC REG SWITCHD CAP DBL ADJ 8MSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 标准包装:2,500 系列:- 类型:升压(升压) 输出类型:可调式 输出数:1 输出电压:1.24 V ~ 30 V 输入电压:1.5 V ~ 12 V PWM 型:电流模式,混合 频率 - 开关:600kHz 电流 - 输出:500mA 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) 供应商设备封装:8-SOIC |

| LTC1751EMS8#TRPBF | 功能描述:IC REG SWITCHD CAP DBL ADJ 8MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 标准包装:2,500 系列:- 类型:升压(升压) 输出类型:可调式 输出数:1 输出电压:1.24 V ~ 30 V 输入电压:1.5 V ~ 12 V PWM 型:电流模式,混合 频率 - 开关:600kHz 电流 - 输出:500mA 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) 供应商设备封装:8-SOIC |

| LTC1751EMS8-3.3 | 功能描述:IC REG SWITCHED CAP DBL 8MSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 产品培训模块:MIC23xxx HyperLight Load™ Regulators 标准包装:5,000 系列:HyperLight Load® 类型:降压(降压) 输出类型:固定 输出数:1 输出电压:1.8V 输入电压:2.7 V ~ 5.5 V PWM 型:混合物 频率 - 开关:4MHz 电流 - 输出:2A 同步整流器:是 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-VFDFN 裸露焊盘,8-MLF? 包装:带卷 (TR) 供应商设备封装:8-MLF?(2x2) 产品目录页面:1094 (CN2011-ZH PDF) 其它名称:576-3303-2 |

发布紧急采购,3分钟左右您将得到回复。