- 您现在的位置:买卖IC网 > PDF目录39413 > LTC2203C#TRPBF (LINEAR TECHNOLOGY CORP) 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 PDF资料下载

参数资料

| 型号: | LTC2203C#TRPBF |

| 厂商: | LINEAR TECHNOLOGY CORP |

| 元件分类: | ADC |

| 英文描述: | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| 封装: | 7 X 7 MM, LEAD FREE, PLASTIC, MO-220-WKKD-2, QFN-48 |

| 文件页数: | 14/26页 |

| 文件大小: | 1118K |

| 代理商: | LTC2203C#TRPBF |

LTC2203/LTC2202

21

22032p

APPLICATIO S I FOR ATIO

W

U

An on-chip clock duty cycle stabilizer may be activated if

the input clock does not have a 50% duty cycle. This circuit

uses the falling edge of CLK pin to sample the analog input.

The rising edge of CLK is ignored and an internal rising

edge is generated by a phase-locked loop. The input clock

duty cycle can vary from 30% to 70% and the clock duty

cycle stabilizer will maintain a constant 50% internal duty

cycle. If the clock is turned off for a long period of time,

the duty cycle stabilizer circuit will require one hundred

clock cycles for the PLL to lock onto the input clock. To

use the clock duty cycle stabilizer, the MODE pin must be

connected to 1/3VDD or 2/3VDD using external resistors.

The lower limit of the LTC2203/LTC2202 sample rate is

determined by droop of the sample and hold circuits. The

pipelined architecture of this ADC relies on storing analog

signals on small valued capacitors. Junction leakage will

dischargethecapacitors.Thespeciedminimumoperating

frequency for the LTC2203/LTC2202 is 1Msps.

DIGITAL OUTPUTS

Digital Output Buffers

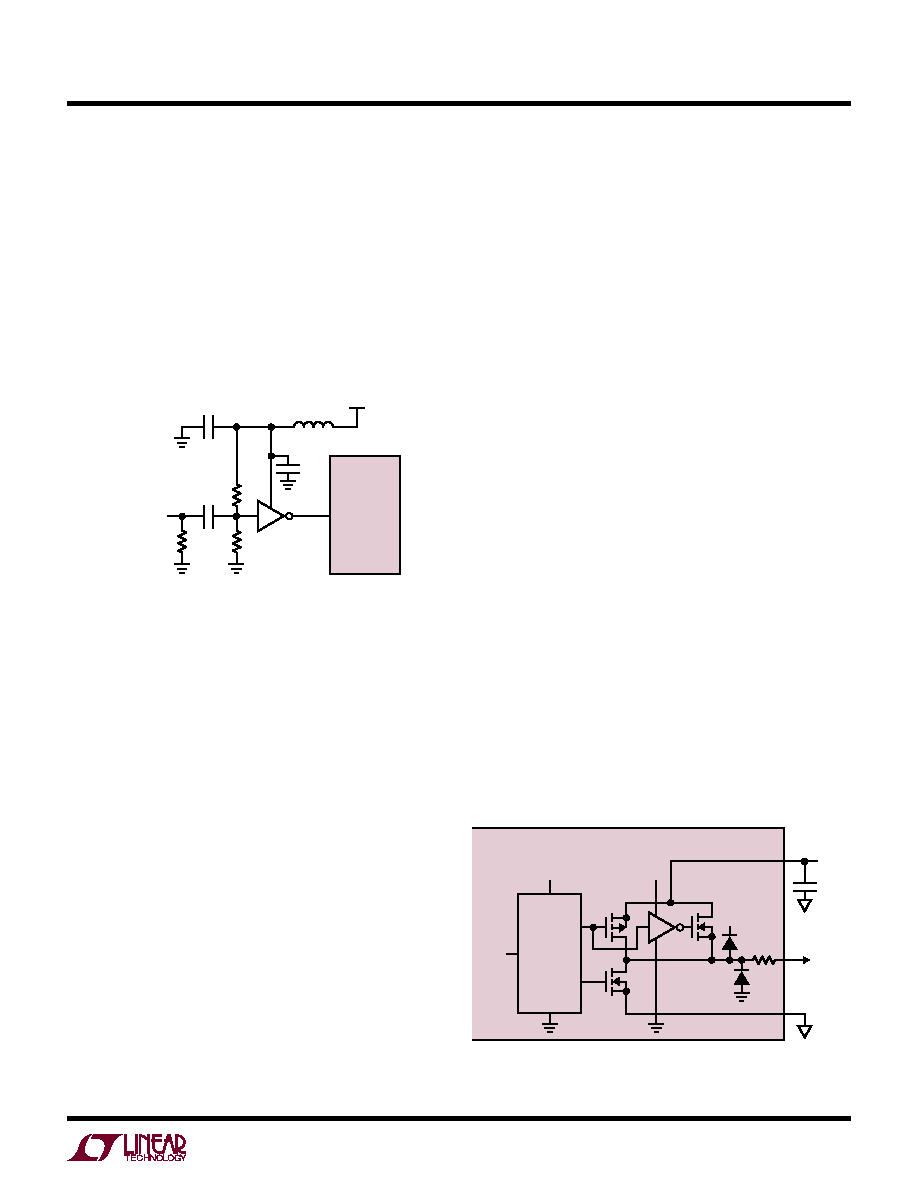

Figure 9 shows an equivalent circuit for a single output

buffer in CMOS Mode. Each buffer is powered by OVDD

and OGND, isolated from the ADC power and ground. The

additional N-channel transistor in the output driver allows

operation down to low voltages. The internal resistor in

series with the output makes the output appear as 50Ω

to external circuitry and eliminates the need for external

damping resistors.

Figure 8. Sinusoidal Single-Ended CLK Drive

CLK

0.1

F

0.1

F

4.7

F

1k

FERRITE

BEAD

CLEAN 3.3V

SUPPLY

SINUSOIDAL

CLOCK

INPUT

22032 F09

NC7SVU04

LTC2203/02

56

higher for input frequencies above 100MHz. For applica-

tions with high input frequencies, the low input range will

have improved distortion; however, the SNR will be 2.4dB

worse. See the typical performance curves section.

Driving the Clock Input

The CLK input can be driven directly with a CMOS or TTL

level signal. A sinusoidal clock can also be used along

with a low-jitter squaring circuit before the CLK pin (see

Figure 8).

The noise performance of the LTC2203/2202 can depend

on the clock signal quality as much as on the analog

input. Any noise present on the clock signal will result in

additional aperture jitter that will be RMS summed with

the inherent ADC aperture jitter.

In applications where jitter is critical, such as when digi-

tizing high input frequencies, use as large an amplitude

as possible. Also, if the ADC is clocked with a sinusoidal

signal, lter the CLK signal to reduce wideband noise and

distortion products generated by the source.

Maximum and Minimum Conversion Rates

ThemaximumconversionratefortheLTC2203is25Msps.

ThemaximumconversionratefortheLTC2202is10Msps.

FortheADCtooperateproperlytheCLKsignalshouldhave

a 50% (±5%) duty cycle. Each half cycle must have at least

18.9ns for the LTC2203 internal circuitry to have enough

settling time for proper operation. For the LTC2202, each

half cycle must be at least 40ns.

Figure 9. Equivalent Circuit for a Digital Output Buffer

LTC2203/02

22032 F10

OVDD

VDD

0.1

F

TYPICAL

DATA

OUTPUT

OGND

43

OVDD 0.5V

TO 3.6V

PREDRIVER

LOGIC

DATA

FROM

LATCH

相关PDF资料 |

PDF描述 |

|---|---|

| LTC2203C#TR | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2203C | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2203I#TRPBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2203I#TR | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2202C#PBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC2203CUK | 制造商:Linear Technology 功能描述:ADC Single Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP |

| LTC2203CUK#PBF | 制造商:Linear Technology 功能描述:ADC Single Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP 制造商:Linear Technology 功能描述:Single ADC Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC 16-BIT 25MSPS 48-QFN 制造商:Linear Technology 功能描述:IC, ADC, 16BIT, 25MSPS, QFN-48, Resolution (Bits):16bit, Sampling Rate:25MSPS, Supply Voltage Type:Single, Supply Voltage Min:3.135V, Supply Voltage Max:3.465V, Supply Current:66mA, Digital IC Case Style:QFN, No. of Pins:48 , RoHS Compliant: Yes 制造商:Linear Technology 功能描述:MS-ADC/High Speed, 16-bit, 25Msps ADC |

| LTC2203CUK#TRPBF | 制造商:Linear Technology 功能描述:ADC Single Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP T/R 制造商:Linear Technology 功能描述:IC ADC 16-BIT 25MSPS 48-QFN |

| LTC2203IUK | 制造商:Linear Technology 功能描述:Single ADC Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP |

| LTC2203IUK#PBF | 制造商:Linear Technology 功能描述:ADC Single Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP 制造商:Linear Technology 功能描述:Single ADC Pipelined 25Msps 16-bit Parallel 48-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC 16-BIT 25MSPS 48-QFN 制造商:Linear Technology 功能描述:IC ADC 16BIT 25MSPS QFN-48 制造商:Linear Technology 功能描述:IC, ADC, 16BIT, 25MSPS, QFN-48, Resolution (Bits):16bit, Sampling Rate:25MSPS, Supply Voltage Type:Single, Supply Voltage Min:3.135V, Supply Voltage Max:3.465V, Supply Current:66mA, Digital IC Case Style:QFN, No. of Pins:48 , RoHS Compliant: Yes 制造商:Linear Technology 功能描述:MS-ADC/High Speed, 16-bit, 25Msps ADC |

发布紧急采购,3分钟左右您将得到回复。