- 您现在的位置:买卖IC网 > PDF目录2005 > LTC2268IUJ-14#TRPBF (Linear Technology)IC ADC 14BIT 125MSPS DUAL 40QFN PDF资料下载

参数资料

| 型号: | LTC2268IUJ-14#TRPBF |

| 厂商: | Linear Technology |

| 文件页数: | 15/32页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 125MSPS DUAL 40QFN |

| 标准包装: | 2,000 |

| 位数: | 14 |

| 采样率(每秒): | 125M |

| 数据接口: | Serial LVDS |

| 转换器数目: | 2 |

| 功率耗散(最大): | 364mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘 |

| 供应商设备封装: | 40-QFN(6x6) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 Differential; 2 Single-Ended |

| 配用: | DC1371A-ND - BOARD USB DATA ACQUISITION HS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

LTC2268-14/

LTC2267-14/LTC2266-14

22

22687614fa

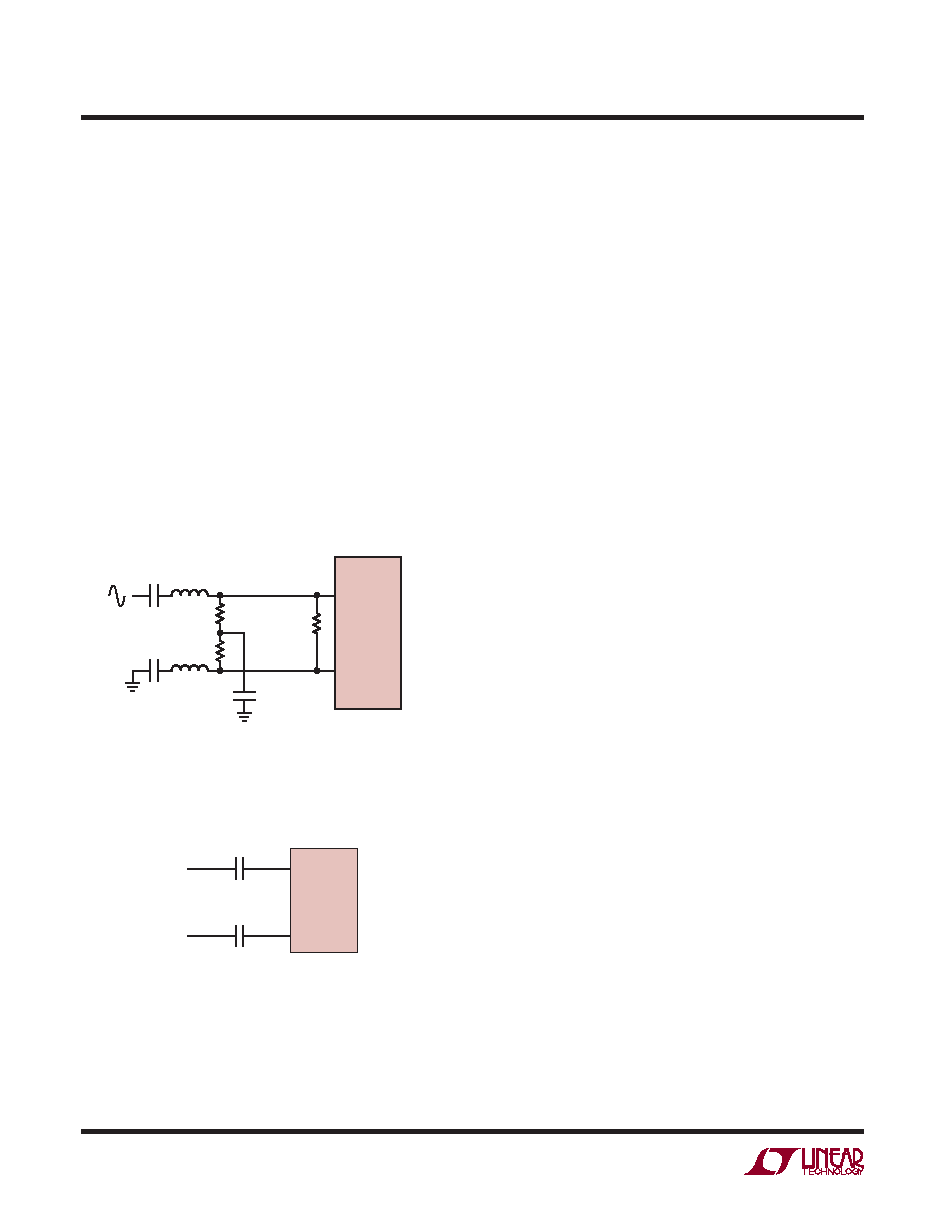

The differential encode mode is recommended for sinu-

soidal, PECL, or LVDS encode inputs (Figures 12 and 13).

The encode inputs are internally biased to 1.2V through

10k equivalent resistance. The encode inputs can be taken

above VDD (up to 3.6V), and the common mode range is

from 1.1V to 1.6V. In the differential encode mode, ENC–

should stay at least 200mV above ground to avoid falsely

triggering the single-ended encode mode. For good jitter

performance ENC+ should have fast rise and fall times.

Thesingle-endedencodemodeshouldbeusedwithCMOS

encode inputs. To select this mode, ENC– is connected

to ground and ENC+ is driven with a square wave encode

input. ENC+ can be taken above VDD (up to 3.6V) so 1.8V

to3.3VCMOSlogiclevelscanbeused.TheENC+threshold

is 0.9V. For good jitter performance ENC+ should have fast

rise and fall times.

applicaTions inForMaTion

Clock PLL and Duty Cycle Stabilizer

The encode clock is multiplied by an internal phase-locked

loop (PLL) to generate the serial digital output data. If the

encode signal changes frequency or is turned off, the PLL

requires 25s to lock onto the input clock.

A clock duty cycle stabilizer circuit allows the duty cycle

of the applied encode signal to vary from 30% to 70%.

In the serial programming mode it is possible to disable

the duty cycle stabilizer, but this is not recommended. In

the parallel programming mode the duty cycle stabilizer

is always enabled.

DIGITAL OUTPUTS

The digital outputs of the LTC2268-14/LTC2267-14/

LTC2266-14 are serialized LVDS signals. Each channel

outputs two bits at a time (2-lane mode). At lower sam-

pling rates there is a one bit per channel option (1-lane

mode). The data can be serialized with 16-, 14-, or 12-bit

serialization (see Timing Diagrams for details). Note that

with 12-bit serialization the two LSBs are not available

— this mode is included for compatibility with the 12-bit

versions of these parts.

The output data should be latched on the rising and falling

edges of the data clock out (DCO). A data frame output

(FR) can be used to determine when the data from a new

conversion result begins. In the 2-lane, 14-bit serialization

mode, the frequency of the FR output is halved.

Themaximumserialdatarateforthedataoutputsis1Gbps,

so the maximum sample rate of the ADC will depend on

the serialization mode as well as the speed grade of the

ADC (see Table 1). The minimum sample rate for all seri-

alization modes is 5Msps.

Figure 12. Sinusoidal Encode Drive

Figure 13. PECL or LVDS Encode Drive

50

100

0.1F

T1

T1 = MA/COM ETC1-1-13

RESISTORS AND CAPACITORS

ARE 0402 PACKAGE SIZE

50

LTC2268-14

226814 F12

ENC–

ENC+

ENC+

ENC–

PECL OR

LVDS

CLOCK

0.1F

226814 F13

LTC2268-14

相关PDF资料 |

PDF描述 |

|---|---|

| LTC2280CUP#PBF | IC ADC DUAL 10BIT 105MSPS 64-QFN |

| LTC2281IUP#PBF | IC ADC 10BIT DUAL 64-QFN |

| LTC2282CUP#PBF | IC ADC DUAL 12BIT 105MSPS 64-QFN |

| LTC2284CUP#PBF | IC ADC DUAL 14BIT 105MSPS 64-QFN |

| LTC2285CUP#PBF | IC ADC DUAL 14BIT 125MSPS 64QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC2269 | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 20Msps Low Noise ADC |

| LTC2269CUK#PBF | 制造商:Linear Technology 功能描述:ADC Single 20Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC 16BIT 20MSPS 48-QFN 制造商:Linear Technology 功能描述:ADC 16BIT 1.8V 20MSPS 48QF 制造商:Linear Technology 功能描述:ADC, 16BIT, 1.8V, 20MSPS, 48QFN 制造商:Linear Technology 功能描述:ADC, 16BIT, 20MSPS, PARALLEL, SERIAL, QFN-48; Resolution (Bits):16bit; Sampling Rate:20MSPS; Supply Voltage Type:Single; Supply Voltage Min:1.7V; Supply Voltage Max:1.9V; Supply Current:48.9mA; Digital IC Case Style:QFN; DNL:0.2LSB ;RoHS Compliant: Yes |

| LTC2269CUK#TRPBF | 制造商:Linear Technology 功能描述:ADC Single 20Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP T/R 制造商:Linear Technology 功能描述:IC ADC 16BIT 20MSPS 48-QFN |

| LTC2269IUK#PBF | 制造商:Linear Technology 功能描述:ADC Single 20Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC 16BIT 20MSPS 48-QFN 制造商:Linear Technology 功能描述:ADC 16BIT 1.8V 20MSPS 48QF 制造商:Linear Technology 功能描述:ADC, 16BIT, 1.8V, 20MSPS, 48QFN 制造商:Linear Technology 功能描述:ADC, 16BIT, 20MSPS, PARALLEL, SERIAL, QFN-48; Resolution (Bits):16bit; Sampling Rate:20MSPS; Supply Voltage Type:Single; Supply Voltage Min:1.7V; Supply Voltage Max:1.9V; Supply Current:48.9mA; Digital IC Case Style:QFN; DNL:0.2LSB ;RoHS Compliant: Yes |

| LTC2269IUK#TRPBF | 制造商:Linear Technology 功能描述:ADC Single 20Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP T/R 制造商:Linear Technology 功能描述:IC ADC 16BIT 20MSPS 48-QFN |

发布紧急采购,3分钟左右您将得到回复。