- 您现在的位置:买卖IC网 > PDF目录10073 > LTC2282CUP#TRPBF (Linear Technology)IC ADC DUAL 12BIT 105MSPS 64-QFN PDF资料下载

参数资料

| 型号: | LTC2282CUP#TRPBF |

| 厂商: | Linear Technology |

| 文件页数: | 5/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC DUAL 12BIT 105MSPS 64-QFN |

| 标准包装: | 2,000 |

| 位数: | 12 |

| 采样率(每秒): | 105M |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 功率耗散(最大): | 630mW |

| 电压电源: | 单电源 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-WFQFN 裸露焊盘 |

| 供应商设备封装: | 64-QFN(9x9) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个单端,双极; 2 个差分, 双极 |

LTC2282

13

2282fb

acquire a new sample. Since the sampling capacitors still

hold the previous sample, a charging glitch proportional to

the change in voltage between samples will be seen at this

time. If the change between the last sample and the new

sample is small, the charging glitch seen at the input will

be small. If the input change is large, such as the change

seen with input frequencies near Nyquist, then a larger

charging glitch will be seen.

Single-Ended Input

For cost sensitive applications, the analog inputs can be

driven single-ended. With a single-ended input the har-

monic distortion and INL will degrade, but the SNR and

DNL will remain unchanged. For a single-ended input, AIN+

should be driven with the input signal and AIN– should be

connected to 1.5V or VCM.

Common Mode Bias

For optimal performance, the analog inputs should be

driven differentially. Each input should swing ±0.5V for the

2V range or ±0.25V for the 1V range, around a common

mode voltage of 1.5V. The VCM output pin may be used

to provide the common mode bias level. VCM can be tied

directly to the center tap of a transformer to set the DC

input level or as a reference level to an op amp differential

driver circuit. The VCM pin must be bypassed to ground

close to the ADC with a 2.2μF, or greater, capacitor.

Input Drive Impedance

As with all high performance, high speed ADCs, the dy-

namic performance of the LTC2282 can be inuenced by

the input drive circuitry, particularly the second and third

harmonics. Source impedance and reactance can inuence

SFDR. At the falling edge of CLK, the sample-and-hold

circuit will connect the 4pF sampling capacitor to the input

pin and start the sampling period. The sampling period

ends when CLK rises, holding the sampled input on the

sampling capacitor. Ideally the input circuitry should be fast

enough to fully charge the sampling capacitor during the

sampling period 1/(2FENCODE); however, this is not always

possible and the incomplete settling may degrade the SFDR.

APPLICATIONS INFORMATION

The sampling glitch has been designed to be as linear as

possible to minimize the effects of incomplete settling.

For the best performance, it is recommended to have a

source impedance of 100Ω, or less, for each input. The

source impedance should be matched for the differential

inputs. Poor matching will result in higher even order

harmonics, especially the second.

Input Drive Circuits

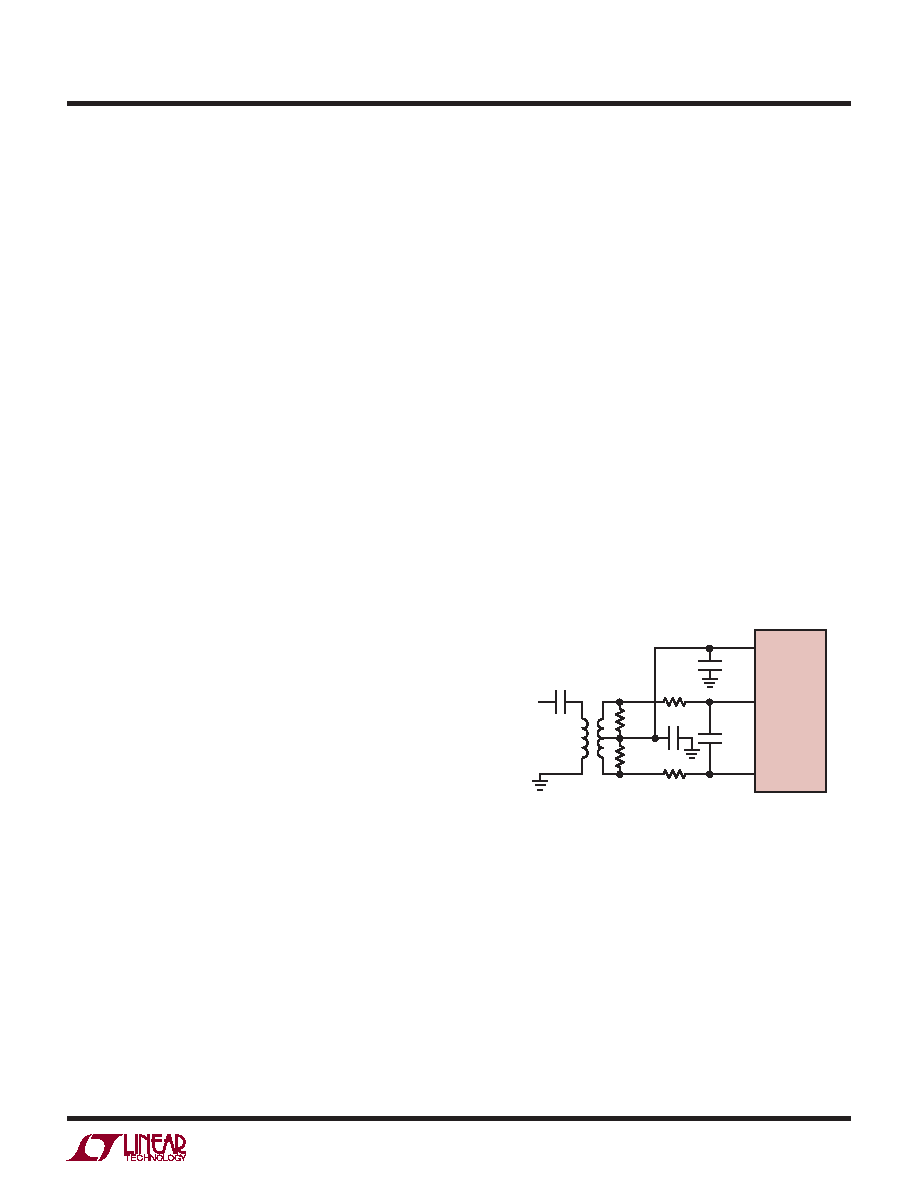

Figure 3 shows the LTC2282 being driven by an RF trans-

former with a center tapped secondary. The secondary

center tap is DC biased with VCM, setting the ADC input

signal at its optimum DC level. Terminating on the trans-

former secondary is desirable, as this provides a common

mode path for charging glitches caused by the sample and

hold. Figure 3 shows a 1:1 turns ratio transformer. Other

turns ratios can be used if the source impedance seen

by the ADC does not exceed 100Ω for each ADC input.

A disadvantage of using a transformer is the loss of low

frequency response. Most small RF transformers have

poor performance at frequencies below 1MHz.

Figure 4 demonstrates the use of a differential amplier to

convert a single-ended input signal into a differential input

signal. The advantage of this method is that it provides

low frequency input response; however, the limited gain

bandwidth of most op amps will limit the SFDR at high

input frequencies.

25Ω

0.1μF

AIN

+

AIN

–

12pF

2.2μF

VCM

LTC2282

ANALOG

INPUT

0.1μF

T1

1:1

T1 = MA/COM ETC1-1T

RESISTORS, CAPACITORS

ARE 0402 PACKAGE SIZE

2282 F03

Figure 3. Single-Ended to Differential Conversion

Using a Transformer

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BN1-IV-F4 | CONVERTER MOD DC/DC 12V 150W |

| LTC2262CUJ-12#TRPBF | IC ADC 12BIT 150MSPS 40-QFN |

| MS27473E18B11P | CONN PLUG 11POS STRAIGHT W/PINS |

| AD7876CR-REEL | IC ADC 12BIT SAMPLING 10V 24SOIC |

| AD976ABRZRL | IC ADC 16BIT 200KSPS 28SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC2282IUP | 制造商:Linear Technology 功能描述:ADC Dual Pipelined 105Msps 12-bit Parallel 64-Pin QFN EP |

| LTC2282IUP#PBF | 功能描述:IC ADC DUAL 12BIT 105MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| LTC2282IUP#TRPBF | 功能描述:IC ADC DUAL 12BIT 105MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| LTC2282IUP-PBF | 制造商:LINER 制造商全称:Linear Technology 功能描述:Dual 12-Bit, 105Msps Low Power 3V ADC |

| LTC2282IUP-TR | 制造商:LINER 制造商全称:Linear Technology 功能描述:Dual 12-Bit, 105Msps Low Power 3V ADC |

发布紧急采购,3分钟左右您将得到回复。