- 您现在的位置:买卖IC网 > PDF目录2006 > LTC2418IGN#TRPBF (Linear Technology)IC ADC 24BIT DIFF INPUT 28SSOP PDF资料下载

参数资料

| 型号: | LTC2418IGN#TRPBF |

| 厂商: | Linear Technology |

| 文件页数: | 8/48页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT DIFF INPUT 28SSOP |

| 标准包装: | 2,500 |

| 位数: | 24 |

| 采样率(每秒): | 7.5 |

| 数据接口: | MICROWIRE?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 1mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 28-SSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 16 个单端,单极;16 个单端,双极;8 个差分,单极;8 个差分,双极 |

| 配用: | DC571A-ND - BOARD DELTA SIGMA ADC LTC2418 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

LTC2414/LTC2418

16

241418fa

parity bit representing the parity of the previous 31 bits. The

parity bit is useful to check the output data integrity espe-

cially when the output data is transmitted over a distance.

The third and fourth bits together are also used to indicate

an underrange condition (the differential input voltage is be-

low – FS) or an overrange condition (the differential input

voltage is above + FS).

Bit 31 (first output bit) is the end of conversion (EOC)

indicator. This bit is available at the SDO pin during the

conversion and sleep states whenever the CS pin is LOW.

This bit is HIGH during the conversion and goes LOW

when the conversion is complete.

Bit 30 (second output bit) is a dummy bit (DMY) and is

always LOW.

Bit 29 (third output bit) is the conversion result sign indi-

cator (SIG). If VIN is >0, this bit is HIGH. If VIN is <0, this

bit is LOW.

Bit 28 (fourth output bit) is the most significant bit (MSB)

of the result. This bit in conjunction with Bit 29 also

provides the underrange or overrange indication. If both

Bit 29 and Bit 28 are HIGH, the differential input voltage is

above +FS. If both Bit 29 and Bit 28 are LOW, the

differential input voltage is below –FS.

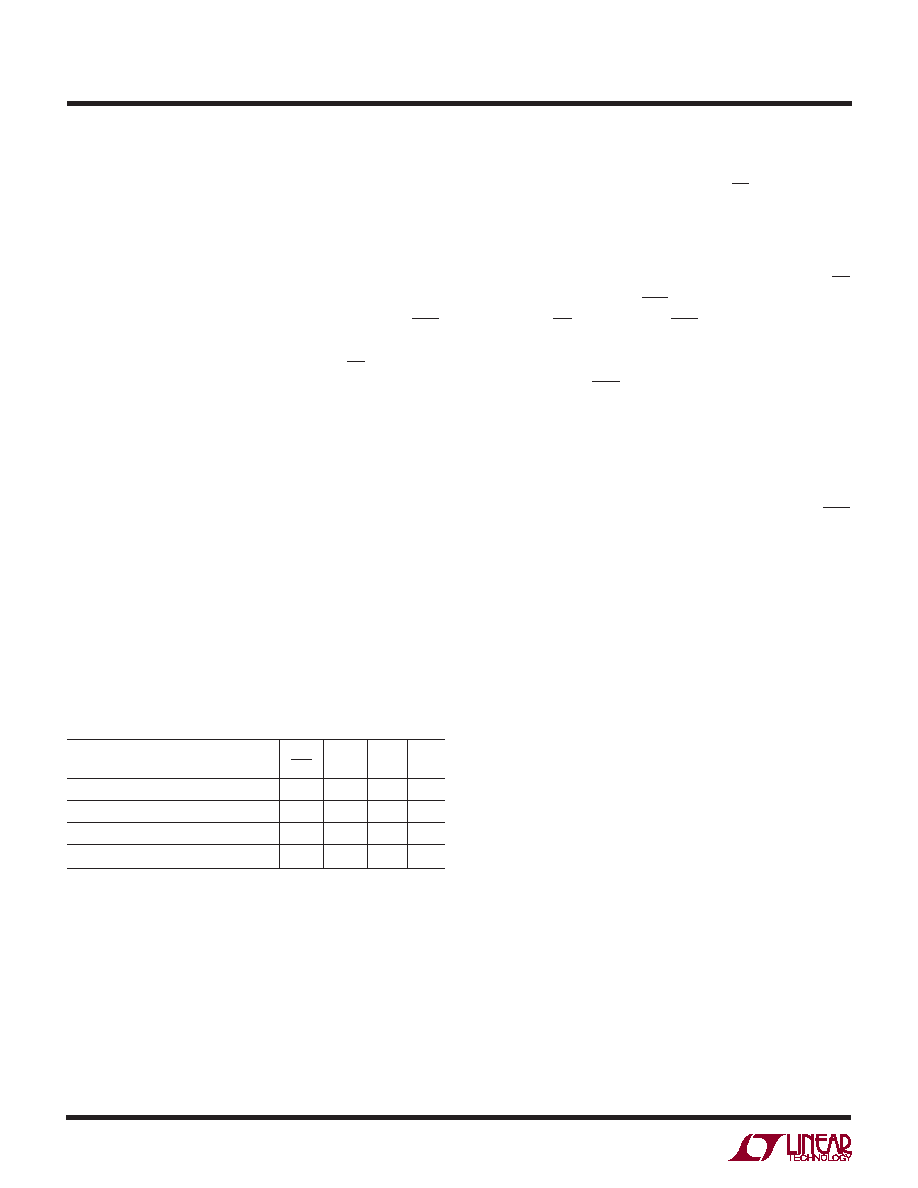

The function of these bits is summarized in Table 3.

Table 3. LTC2414/LTC2418 Status Bits

Bit 31

Bit 30 Bit 29 Bit 28

Input Range

EOC

DMY

SIG

MSB

VIN ≥ 0.5 VREF

00

1

0V

≤ VIN < 0.5 VREF

00

1

0

–0.5 VREF ≤ VIN < 0V

0

1

VIN < – 0.5 VREF

00

0

Bits 28-6 are the 23-bit conversion result MSB first.

Bit 6 is the least significant bit (LSB).

Bits 5-1 are the corresponding channel selection bits for

the present conversion result with bit SGL output first as

shown in Figure 3.

Bit 0 is the parity bit representing the parity of the previous

31 bits. Including the parity bit, the total numbers of 1’s

and 0’s in the output data are always even.

Data is shifted out of the SDO pin under control of the serial

clock (SCK), see Figure 3. Whenever CS is HIGH, SDO

remains high impedance and any externally generated

SCK clock pulses are ignored by the internal data out shift

register.

In order to shift the conversion result out of the device, CS

must first be driven LOW. EOC is seen at the SDO pin of the

device once CS is pulled LOW. EOC changes real time from

HIGH to LOW at the completion of a conversion. This

signal may be used as an interrupt for an external micro-

controller. Bit 31 (EOC) can be captured on the first rising

edge of SCK. Bit 30 is shifted out of the device on the first

falling edge of SCK. The final data bit (Bit 0) is shifted out

on the falling edge of the 31st SCK and may be latched on

the rising edge of the 32nd SCK pulse. On the falling edge

of the 32nd SCK pulse, SDO goes HIGH indicating the

initiation of a new conversion cycle. This bit serves as EOC

(Bit 31) for the next conversion cycle. Table 4 summarizes

the output data format.

As long as the voltage applied to any channel (CH0-CH15,

COM) is maintained within the – 0.3V to (VCC + 0.3V)

absolute maximum operating range, a conversion result is

generated for any differential input voltage VIN from

–FS = – 0.5 VREF to +FS = 0.5 VREF. For differential input

voltages greater than +FS, the conversion result is clamped

to the value corresponding to the +FS + 1LSB. For differ-

ential input voltages below –FS, the conversion result is

clamped to the value corresponding to –FS – 1LSB.

Frequency Rejection Selection (FO)

The LTC2414/LTC2418 internal oscillator provides better

than 110dB normal mode rejection at the line frequency

and all its harmonics for 50Hz

±2% or 60Hz ±2%. For

60Hz rejection, FO should be connected to GND while for

50Hz rejection the FO pin should be connected to VCC.

The selection of 50Hz or 60Hz rejection can also be made

by driving FO to an appropriate logic level. A selection

change during the sleep or data output states will not

disturb the converter operation. If the selection is made

during the conversion state, the result of the conversion in

progress may be outside specifications but the following

conversions will not be affected.

APPLICATIO S I FOR ATIO

WU

UU

相关PDF资料 |

PDF描述 |

|---|---|

| LTC2431IMS#TRPBF | IC ADC 20BIT DIFFINPUT/REF10MSOP |

| LTC2433-1IMS#TRPBF | IC ADC DIFF 16BIT 3WIRE 10-MSOP |

| LTC2435CGN#TRPBF | IC ADC DIFF I/REF 20BIT 16-SSOP |

| LTC2442IG#PBF | IC ADC 24BIT 4CH 36-SSOP |

| LTC2446IUHF#TRPBF | IC ADC 24BIT 8CH HI SPEED 38QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC2420CS8 | 功能描述:IC ADC 20BIT MICRPWR W/OSC 8SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| LTC2420CS8#PBF | 功能描述:IC ADC 20BIT MICRPWR W/OSC 8SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| LTC2420CS8#PBF | 制造商:Linear Technology 功能描述:A/D Converter (A-D) IC |

| LTC2420CS8#TR | 功能描述:IC A/D CONV 20BIT MICRPWR 8-SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| LTC2420CS8#TRPBF | 功能描述:IC ADC 20BIT MICRPWR W/OSC 8SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

发布紧急采购,3分钟左右您将得到回复。